半导体结构的形成方法与流程

1.本发明涉及半导体技术领域,尤其涉及一种半导体结构的形成方法。

背景技术:

2.随着半导体工业在追求更高的器件密度、更高的性能和更低的成本的过程中进入纳米技术工艺节点,来自制造和设计问题的挑战已经引起了多栅极场效应晶体管的三维设计的发展。

3.传统的鳍式场效应晶体管在进一步增大工作电流方面存在限制。具体的,由于鳍部中只有靠近顶部表面和侧壁的区域用来作为沟道区,使得鳍部中用于作为沟道区的体积较小,这对增大鳍式场效应晶体管的工作电流造成限制。因此,提出了一种沟道栅极环绕(gate-all-around,简称gaa)结构的鳍式场效应晶体管,使得用于作为沟道区的体积增加,进一步的增大了沟道栅极环绕结构鳍式场效应晶体管的工作电流。

4.在提出沟道栅极环绕(gate-all-around,简称gaa)结构的鳍式场效应晶体管的基础上,为了进一步提高器件密度,提出了具有多个垂直堆叠对gaa的互补鳍式场效应晶体管(简称cfet)。互补鳍式场效应晶体管通过在布局上,将一个n型的gaa设置于一个p型的gaa上方或下方,并且,使该堆叠对的n型gaa和p型gaa共用贯穿并包覆各沟道区的栅极,实现进一步缩小集成电路的面积。

5.因此,亟需提出一种用于上述互补鳍式场效应晶体管的电互连结构的形成方法。

技术实现要素:

6.本发明解决的技术问题是提供一种用于互补鳍式场效应晶体管的电互连结构的形成方法。

7.为解决上述技术问题,本发明的技术方案提供一种半导体结构的形成方法,包括:提供衬底,所述衬底包括沿第一方向排布的第一区、第二区和第三区,所述第二区位于所述第一区和第三区之间;在所述第二区上形成若干第一纳米线,所述第一方向垂直于所述第一纳米线的延伸方向;在若干所述第一纳米线顶面上形成若干第二纳米线;在所述衬底表面形成包围所述第一纳米线和第二纳米线的介质层;在所述第一区的介质层内形成第一开口,所述第一开口暴露出第一区的衬底表面;在所述第一开口上的第一区及第二区的介质层内形成第二开口,所述第二开口暴露出所述第一纳米线,并且所述第一开口和所述第二开口连通;在所述第一开口和所述第二开口内形成第一电互连结构,所述第一电互连结构用于使所述第一纳米线和所述衬底之间电互连;在所述第三区的介质层内形成第三开口,所述第三开口暴露出第三区的衬底表面;在所述第二开口和所述第三开口上的第三区及第二区的介质层内形成第四开口,所述第四开口暴露出所述第二纳米线,并且所述第三开口和所述第四开口连通;在所述第三开口和所述第四开口内形成第二电互连结构,所述第二电互连结构用于使所述第二纳米线和所述衬底之间电互连。

8.可选的,形成所述第一开口和第二开口的方法包括:在所述介质层表面形成第一

图形化层,所述第一图形化层暴露出所述第一区的介质层表面;以所述第一图形化层为掩膜,刻蚀所述介质层;在以所述第一图形化层为掩膜,刻蚀所述介质层后,在所述介质层顶部表面形成第二图形化层,所述第二图形化层暴露出所述第一区和第二区的介质层表面;以所述第二图形化层为掩膜,刻蚀所述介质层,直至暴露出第一纳米线以及第一区的衬底表面。

9.可选的,形成所述第一图形化层的方法包括:在所述介质层表面形成初始第一图形化层,所述初始第一图形化层具有第一图形开口,所述第一图形开口暴露出第一区和第二区的介质层表面;在所述第一图形开口内形成第一待去除层;在形成所述第一待去除层后,去除部分第一区的第一待去除层以形成第二图形开口,所述第二图形开口暴露出所述第一区的介质层表面。

10.可选的,形成所述第二图形化层的方法包括:在以所述第一图形化层为掩膜,刻蚀所述介质层后,去除所述第一待去除层。

11.可选的,形成所述第三开口和第四开口的方法包括:在形成所述第一电互连结构之后,在所述介质层表面形成第三图形化层,所述第三图形化层暴露出所述第三区的介质层表面;以所述第三图形化层为掩膜,刻蚀所述介质层;在以所述第三图形化层为掩膜,刻蚀所述介质层后,在所述介质层顶部表面形成第四图形化层,所述第四图形化层暴露出所述第二区和第三区的介质层表面;以所述第四图形化层为掩膜,刻蚀所述介质层,直至暴露出第二纳米线以及第三区的衬底表面。

12.可选的,形成所述第三图形化层的方法包括:在所述介质层表面形成初始第三图形化层,所述初始第三图形化层具有第三图形开口,所述第三图形开口暴露出第三区和第二区的介质层表面;在所述第三图形开口内形成第二待去除层;在形成所述第二待去除层后,去除部分第三区的第二待去除层以形成第四图形开口,所述第四图形开口暴露出所述第三区的介质层表面。

13.可选的,形成所述第四图形化层的方法包括:在以所述第三图形化层为掩膜,刻蚀所述介质层后,去除所述第二待去除层,以形成第四图形化层。

14.可选的,所述介质层包括第一介质层和第二介质层;形成所述第一介质层和所述第二介质层的方法包括:在形成所述第一纳米线和第二纳米线后,在所述衬底表面形成包围所述第一纳米线和第二纳米线的第一介质层;刻蚀所述第一介质层,以形成所述第一开口和所述第二开口;在形成所述第一电互连结构后,在所述第一电互连结构表面上形成包围所述第二纳米线的第二介质层。

15.可选的,形成所述第一电互连结构的方法包括:在所述第一开口和第二开口内形成第一电互连结构材料层;平坦化所述第一电互连结构材料层,直至暴露出所述第二纳米线顶部表面;在平坦化所述第一电互连结构材料层后,刻蚀所述第一电互连结构材料层,直至暴露出所述第二纳米线底部表面。

16.可选的,刻蚀所述第一电互连结构材料层的工艺包括干法刻蚀工艺。

17.可选的,所述第一纳米线内具有第一离子,所述第二纳米线内具有第二离子,并且所述第一离子和所述第二离子的导电类型相反。

18.可选的,在所述第一方向上,所述第一纳米线具有第一宽度,在垂直于衬底表面的方向上,所述第一纳米线具有第一高度,并且,所述第一高度大于所述第一宽度。

19.可选的,所述第一宽度的范围为2纳米至20纳米。

20.可选的,在所述第一方向上,所述第二纳米线具有第二宽度,在垂直于衬底表面的方向上,所述第二纳米线具有第二高度,并且,所述第二高度大于所述第二宽度。

21.可选的,所述第二宽度的范围为2纳米至20纳米。

22.可选的,形成所述第一开口和第二开口的工艺包括干法刻蚀工艺。

23.可选的,形成所述第三开口和第四开口的工艺包括干法刻蚀工艺。

24.可选的,所述第一电互连结构的材料包括金属材料。

25.可选的,所述第二电互连结构的材料包括金属材料。

26.可选的,所述介质层的材料包括氮化硅、氧化硅、氮氧化硅、碳氧化硅、碳氮化硅或碳氮氧化硅。

27.可选的,所述衬底还包括沿第二方向排布的2个互连区,以及位于所述2个互连区之间的栅极区,所述第二方向为所述第一纳米线的延伸方向,所述第一电互连结构和所述第二电互连结构位于所述互连区中。

28.可选的,还包括:在形成所述第一纳米线之后,在所述栅极区的第一纳米线表面形成第一栅极结构;在形成所述第二纳米线之后,在所述栅极区的第二纳米线表面形成第二栅极结构。

29.可选的,所述若干第一纳米线之间相互分立,所述若干第二纳米线之间相互分立。

30.可选的,所述第二纳米线底面与所述第一纳米线顶面之间相互间隔。

31.可选的,所述第二电互连结构与所述第一电互连结构之间电绝缘。

32.与现有技术相比,本发明的技术方案具有以下有益效果:

33.在本发明技术方案中的半导体结构的形成方法中,通过形成所述第一开口和第二开口,并在所述第一开口和第二开口内形成与第一纳米线以及衬底电互连的所述第一电互连结构,实现了形成第一纳米线与衬底之间的电互连结构,通过形成所述第三开口和第四开口,并在所述第三开口和第四开口内形成与第二纳米线以及衬底电互连的所述第二电互连结构,实现了形成第二纳米线与衬底之间的电互连结构,从而,实现了形成互补鳍式场效应晶体管中纳米线与衬底之间的电互连结构,有利于实现进一步缩小集成电路的面积。同时,由于在形成所述第一开口的同时形成第二开口,因此,减小了形成第一开口过程中工艺需要克服的深宽比,有利于减少大深宽比引起的孔穴,并改善第一开口的图形形貌,从而,能够提高半导体结构的性能。同理,由于在形成所述第三开口的同时形成所述第四开口,因此,减小了形成第三开口过程中工艺需要克服的深宽比,有利于减少大深宽比引起的孔穴,并改善第三开口的图形形貌,从而,能够提高半导体结构的性能。

附图说明

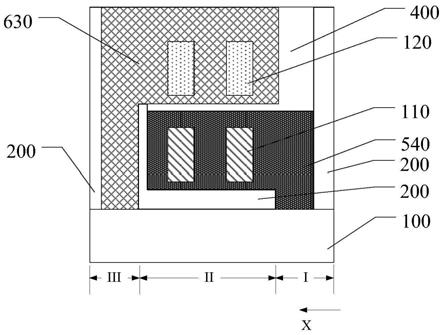

34.图1至图10是本发明实施例的半导体结构的形成方法各步骤的剖面结构示意图。

具体实施方式

35.如背景技术所述,为了实现具有多个垂直堆叠对gaa的互补鳍式场效应晶体管,以进一步缩小集成电路的面积,因此,亟需提出一种用于上述互补鳍式场效应晶体管的电互连结构的形成方法。

36.为了解决上述问题,本发明技术方案提供一种半导体结构的形成方法,通过形成所述第一开口和第二开口,并在所述第一开口和第二开口内形成与第一纳米线以及衬底电互连的所述第一电互连结构,以及形成第三开口和第四开口,并在所述第三开口和第四开口内形成与第二纳米线及衬底电互连的所述第二电互连结构,实现了形成互补鳍式场效应晶体管中纳米线与衬底之间的电互连,从而,有利于实现进一步缩小集成电路的面积。

37.为使本发明的上述目的、特征和有益效果能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

38.需要注意的是,本说明书中的“表面”,用于描述空间的相对位置关系,并不限定于是否直接接触。

39.图1至图10是本发明实施例的半导体结构的形成方法各步骤的剖面结构示意图。

40.请参考图1,提供衬底100,所述衬底100包括沿第一方向x排布的第一区i、第二区ii和第三区iii,所述第二区ii位于所述第一区i和第三区iii之间;在所述第二区ii上形成若干第一纳米线110,所述第一方向x垂直于所述第一纳米线110的延伸方向;在若干所述第一纳米线110顶面上形成若干第二纳米线120;在形成所述第一纳米线110和第二纳米线120后,在所述衬底100表面形成包围所述第一纳米线110和第二纳米线120的第一介质层200。

41.所述第一介质层200和后续形成的第二介质层构成介质层。

42.所述衬底100的材料包括半导体材料。

43.在本实施例中,所述衬底100的材料包括硅。

44.在其他实施例中,所述衬底的材料包括碳化硅、硅锗、

ⅲ-ⅴ

族元素构成的多元半导体材料、绝缘体上硅(soi)或者绝缘体上锗。其中,

ⅲ-ⅴ

族元素构成的多元半导体材料包括inp、gaas、gap、inas、insb、ingaas或者ingaasp。

45.在其他实施例中,所述衬底内具有器件层(未图示)。所述器件层可以包括器件结构,例如,pmos晶体管或者nmos晶体管。所述器件层还可以包括与器件结构电连接的互连结构,以及包围所述器件结构与所述互连结构的绝缘层。

46.在本实施例中,所述第一纳米线110和第二纳米线120的材料包括硅。

47.在其他实施例中,所述第一纳米线和第二纳米线的材料包括碳化硅、硅锗、

ⅲ-ⅴ

族元素构成的多元半导体材料、绝缘体上硅(soi)或者绝缘体上锗。其中,

ⅲ-ⅴ

族元素构成的多元半导体材料包括inp、gaas、gap、inas、insb、ingaas或者ingaasp。

48.在本实施例中,所述第一纳米线110内具有第一离子,所述第二纳米线120内具有第二离子,并且所述第一离子和所述第二离子的导电类型相反。

49.具体而言,在本实施例中,所述第一离子为p型离子,所述第一离子包括硼离子、bf

2-离子或铟离子;所述第二离子为n型离子,所述第二离子包括磷离子、砷离子或锑离子。

50.在其他实施例中,所述第一离子为n型离子,所述第一离子包括磷离子、砷离子或锑离子;所述第二离子为p型离子,所述第二离子包括硼离子、bf

2-离子或铟离子。

51.在本实施例中,所述若干第一纳米线110之间相互分立。

52.在本实施例中,所述若干第二纳米线120之间相互分立,并且,所述第二纳米线120底面与所述第一纳米线110顶面之间相互间隔。

53.在本实施例中,在所述第一方向x上,所述第一纳米线110具有第一宽度w1,在垂直于衬底100表面的方向上,所述第一纳米线110具有第一高度h1,并且,所述第一高度h1大于

所述第一宽度w1。

54.在本实施例中,在所述第一方向上,所述第二纳米线120具有第二宽度w2,在垂直于衬底100表面的方向上,所述第二纳米线120具有第二高度h2,并且,所述第二高度h2大于所述第二宽度w2。

55.通过使所述第一高度h1大于所述第一宽度w1,能够减小所述第一纳米线110的占用面积,通过使所述第二高度h2大于所述第二宽度w2,能够减小所述第二纳米线120的占用面积,从而,能够提高半导体结构的集成度。

56.在本实施例中,所述第一宽度w1的范围为2纳米至20纳米;所述第二宽度w2的范围为2纳米至20纳米。

57.在本实施例中,形成所述第一纳米线110、第二纳米线120和第一介质层200的方法包括:在所述衬底100表面形成第一材料层(未图示);在所述第二区ii的第一材料层表面形成若干相互分立的第一纳米线110;在所述第一纳米线110表面和所述第一材料层表面形成第二材料层(未图示);在所述第一纳米线110上的第二材料层表面形成若干相互分立第二纳米线120;在所述第二纳米线120表面和第二材料层表面形成第三材料层。

58.所述第一材料层、第二材料层和第三材料层构成所述第一介质层200。

59.在本实施例中,所述第一介质层200的材料包括氧化硅。

60.在其他实施例中,所述第一介质层的材料包括氮化硅、氮氧化硅、碳氧化硅、碳氮化硅或碳氮氧化硅。

61.形成所述第一材料层、第二材料层和第三材料层的工艺包括化学气相沉积工艺或者旋涂工艺。

62.在本实施例中,形成所述第一材料层、第二材料层和第三材料层的工艺包括化学气相沉积工艺。

63.在本实施例中,形成所述第一纳米线110和第二纳米线120的工艺包括干法刻蚀工艺。

64.在本实施例中,所述衬底100还包括沿第二方向排布的2个互连区(未图示),以及位于所述2个互连区之间的栅极区(未图示),所述第二方向为所述第一纳米线110的延伸方向(垂直纸面方向)。

65.在本实施例中,在形成所述第一纳米线110之后,在所述栅极区的第一纳米线110表面形成第一栅极结构(未图示);在形成所述第二纳米线120之后,在所述栅极区的第二纳米线表面形成第二栅极结构(未图示)。

66.在本实施例中,在所述第一区i的介质层内形成第一开口,所述第一开口暴露出第一区i的衬底100表面;在所述第一开口上的第一区i及第二区ii的介质层内形成第二开口,所述第二开口暴露出所述第一纳米线110,并且所述第一开口和所述第二开口连通。具体形成所述第一开口和第二开口的过程请参考图2至图4。

67.请参考图2,在所述介质层表面形成第一图形化层,所述第一图形化层暴露出所述第一区i的介质层表面;以所述第一图形化层为掩膜,刻蚀所述介质层。

68.具体而言,在本实施例中,在所述介质层表面形成第一图形化层是指,在所述第一介质层200表面形成第一图形化层;以所述第一图形化层为掩膜,刻蚀所述介质层是指,以所述第一图形化层为掩膜刻蚀所述第一介质层200。

69.在本实施例中,刻蚀所述第一介质层200的工艺包括干法刻蚀工艺。

70.形成所述第一图形化层的方法包括:在所述第一介质层200表面形成初始第一图形化层310,所述初始第一图形化层310具有第一图形开口(未图示),所述第一图形开口暴露出第一区i和第二区ii的第一介质层200表面;在所述第一图形开口内形成第一待去除层320;在形成所述第一待去除层320后,去除部分第一区i的第一待去除层320以形成第二图形开口330,所述第二图形开口330暴露出所述第一区i的第一介质层200表面。

71.所述初始第一图形化层310、第一待去除层320和第二图形开口330构成所述第一图形化层。

72.在本实施例中,形成所述初始第一图形化层310的方法包括:在所述第一介质层200表面形成第一图形化材料层(未图示);在所述第一图形化材料层表面形成第一光刻胶层(未图示),所述第一光刻胶层暴露出第一区i和第二区ii的第一图形化材料层表面;以所述第一光刻胶层为掩膜,刻蚀所述第一图形化材料层,直至暴露出所述第一介质层200表面,以形成所述初始第一图形化层310。

73.在本实施例中,形成所述初始第一图形化层310后,去除所述第一光刻胶层。

74.在本实施例中,形成第二图形开口330的方法包括:在去除所述第一光刻胶层后,在所述初始第一图形化层310表面及所述第一待去除层320表面形成第二光刻胶层(未图示);所述第二光刻胶层暴露出所述第一区i的第一待去除层320表面;以所述第二光刻胶层为掩膜,刻蚀所述第一待去除层320,直至暴露出所述第一介质层200表面。

75.在本实施例中,形成所述第二图形开口330后,去除所述第二光刻胶层。

76.请参考图3,在以所述第一图形化层为掩膜,刻蚀所述第一介质层200后,在所述第一介质层200顶部表面形成第二图形化层,所述第二图形化层暴露出所述第一区i和第二区ii的第一介质层200表面。

77.在本实施例中,形成所述第二图形化层的方法包括:在以所述第一图形化层为掩膜,刻蚀所述第一介质层200后,去除所述第一待去除层320。

78.具体而言,在本实施例中,所述第二图形化层是指所述初始第一图形化层310。

79.在其他实施例中,形成所述第二图形化层的方法包括:在以所述第一图形化层为掩膜,刻蚀所述第一介质层后,去除所述第一图形化层;在去除所述第一图形化层后,在所述第一介质层表面形成第二图形化材料层;去除部分第一区和第二区的第二图形化材料层,以形成第二图形化层。

80.请参考图4,以所述第二图形化层为掩膜,刻蚀所述介质层,直至暴露出第一纳米线110以及第一区i的衬底100表面。

81.具体而言,在本实施例中,以所述初始第一图形化层310为掩膜,刻蚀所述第一介质层200,直至暴露出第一纳米线110、第二纳米线120以及第一区i的衬底100表面,以在第一区i的第一介质层200内形成第一开口510,在所述第一开口510上的第一区i及第二区ii的第一介质层200内形成第二开口520,以及,在所述第二开口520上的第一介质层200内形成第五开口530。

82.所述第一开口510暴露出所述第一区i的衬底100表面,所述第二开口520暴露出所述第一纳米线110,所述第五开口530暴露出所述第二纳米线120,并且,所述第一开口510和第二开口520连通,所述第二开口520和所述第五开口530连通。

83.由于在形成所述第一开口510的同时形成第二开口520,因此,减小了形成第一开口510过程中工艺需要克服的深宽比,有利于减少大深宽比引起的孔穴,并改善第一开口510的图形形貌,从而,能够提高半导体结构的性能。

84.在本实施例中,刻蚀所述第一介质层200以形成所述第一开口510和第二开口520的工艺包括干法刻蚀工艺。

85.在本实施例中,在形成所述第一开口510和所述第二开口520后,去除所述第二图形化层,即,所述初始第一图形化层310。

86.请参考图5,在所述第一开口510和所述第二开口520内形成第一电互连结构540。

87.所述第一电互连结构540用于使所述第一纳米线110与所述衬底100之间电互连。

88.从而,通过形成所述第一开口510和第二开口520,并在所述第一开口510和第二开口520内形成与第一纳米线110以及衬底100电互连的所述第一电互连结构540,实现了形成第一纳米线110与衬底100之间的电互连结构。

89.在本实施例中,形成所述第一电互连结构540的方法包括:在所述第一开口510、第二开口520和第五开口530内形成第一电互连结构材料层(未图示);平坦化所述第一电互连结构材料层,直至暴露出所述第二纳米线120顶部表面;在平坦化所述第一电互连结构材料层后,刻蚀所述第一电互连结构材料层,直至暴露出所述第二纳米线120底部表面。

90.形成所述第一电互连结构材料层的工艺包括化学气相沉积工艺、电镀工艺或者外延生长工艺。

91.在本实施例中,形成所述第一电互连结构材料层的工艺包括化学气相沉积工艺。

92.在本实施例中,刻蚀所述第一电互连结构材料层的工艺包括干法刻蚀工艺。通过采用干法刻蚀工艺,能够在刻蚀所述第一电互连结构材料层时,减少刻蚀工艺对所述第二纳米线120的损伤,从而改善半导体结构的形貌,提高半导体结构的图形精度。

93.在本实施例中,所述第一电互连结构540的材料包括金属材料,例如钨或者钛。

94.请参考图6,在形成所述第一电互连结构540后,在所述第一电互连结构540表面上形成包围所述第二纳米线110的第二介质层400。

95.所述第一介质层200和第二介质层400构成所述介质层。

96.具体而言,在本实施例中,形成所述第二介质层400的方法包括:在所述第五开口530内形成所述第二介质层400。

97.在本实施例中,所述第二介质层400的材料包括氧化硅。

98.在其他实施例中,所述第二介质层的材料包括氮化硅、氮氧化硅、碳氧化硅、碳氮化硅或碳氮氧化硅。

99.后续,在形成所述第一电互连结构540之后,在所述第三区iii的介质层内形成第三开口,所述第三开口暴露出第三区iii的衬底100表面;在所述第二开口520和所述第三开口上的第三区iii及第二区ii的介质层内形成第四开口,所述第四开口暴露出所述第二纳米线120,并且所述第三开口和所述第四开口连通。具体形成所述第三开口和第四开口的过程请参考图7至图9。

100.请参考图7,在形成所述第一电互连结构540之后,在所述介质层表面形成第三图形化层,所述第三图形化层暴露出所述第三区iii的介质层表面;以所述第三图形化层为掩膜,刻蚀所述介质层。

101.具体而言,在本实施例中,在所述介质层表面形成第三图形化层是指,在所述第一介质层200顶部表面和第二介质层400顶部表面形成第三图形化层;以所述第三图形化层为掩膜,刻蚀所述介质层是指,以所述第三图形化层为掩膜刻蚀所述第一介质层200。

102.在本实施例中,刻蚀所述第一介质层200的工艺包括干法刻蚀工艺。

103.形成所述第三图形化层的方法包括:在所述第一介质层200顶部表面和第二介质层400顶部表面形成初始第三图形化层340,所述初始第三图形化层340具有第三图形开口(未图示),所述第三图形开口暴露出第三区iii的第一介质层200表面以及第二区ii的第二介质层400表面;在所述第三图形开口内形成第二待去除层350;在形成所述第二待去除层350后,去除部分第三区iii的第二待去除层350,以形成第四图形开口360,所述第四图形开口360暴露出所述第三区iii的第一介质层200表面。

104.所述初始第三图形化层340、第二待去除层350和第四图形开口360构成所述第三图形化层。

105.在本实施例中,形成所述初始第三图形化层340的方法包括:在所述第一介质层200顶部表面和第二介质层400顶部表面形成第三图形化材料层(未图示);在所述第三图形化材料层表面形成第三光刻胶层(未图示),所述第三光刻胶层暴露出第三区iii和第二区ii的第三图形化材料层表面;以所述第三光刻胶层为掩膜,刻蚀所述第三图形化材料层,直至暴露出所述第一介质层200顶部表面和第二介质层400顶部表面,以形成所述初始第三图形化层340。

106.在本实施例中,形成所述初始第三图形化层340后,去除所述第三光刻胶层。

107.在本实施例中,形成第四图形开口360的方法包括:在去除所述第三光刻胶层后,在所述初始第三图形化层340表面及所述第二待去除层350表面形成第四光刻胶层(未图示);所述第四光刻胶层暴露出所述第三区iii的第二待去除层350表面;以所述第四光刻胶层为掩膜,刻蚀所述第二待去除层350,直至暴露出所述第一介质层200表面。

108.在本实施例中,形成所述第四图形开口360后,去除所述第四光刻胶层。

109.请参考图8,在以所述第三图形化层为掩膜,刻蚀所述第一介质层200后,在所述第一介质层200顶部表面和所述第二介质层400顶部表面形成第四图形化层,所述第四图形化层暴露出所述第三区iii的第一介质层200表面以及第二区ii的第二介质层400表面。

110.具体而言,在本实施例中,形成所述第四图形化层的方法包括:在以所述第三图形化层为掩膜,刻蚀所述第一介质层200后,去除所述第二待去除层350。

111.具体而言,在本实施例中,所述第四图形化层是指所述初始第三图形化层340。

112.请参考图9,以所述第四图形化层为掩膜,刻蚀所述介质层,直至暴露出第二纳米线120以及第三区iii的衬底100表面。

113.具体而言,在本实施例中,以所述初始第三图形化层340为掩膜,刻蚀所述第一介质层200和第二介质层400,直至暴露出第二纳米线120以及第三区iii的衬底100表面,以在第三区iii的第一介质层200内形成第三开口610,在所述第三开口610上的第二区ii和第三区iii的第一介质层200及第二介质层400内形成第四开口620。

114.所述第三开口610暴露出所述第三区iii的衬底100表面,所述第四开口620暴露出所述第二纳米线120,并且,所述第三开口610和第四开口620连通。

115.由于在形成所述第三开口610的同时形成所述第四开口620,因此,减小了形成第

三开口610过程中工艺需要克服的深宽比,有利于减少大深宽比引起的孔穴,并改善第三开口610的图形形貌,从而,能够提高半导体结构的性能。

116.在本实施例中,所述第三开口610、所述第四开口620与所述第一电互连结构540之间间隔,即,所述第一电互连结构540表面具有第一介质层200和第二介质层400,从而,通过所述第一电互连结构540表面的第一介质层200和第二介质层400,使后续形成的第二电互连结构与所述第一电互连结构540之间电绝缘。

117.在本实施例中,刻蚀所述第一介质层200和第二介质层400以形成所述第三开口610和第四开口620的工艺包括干法刻蚀工艺。

118.请参考图10,在所述第三开口610和所述第四开口620内形成第二电互连结构630。

119.所述第二电互连结构630用于使所述第二纳米线120与所述衬底100之间电互连。

120.从而,通过形成所述第三开口610和所述第四开口620,并在所述第三开口610和所述第四开口620内形成与第二纳米线120以及衬底100电互连的所述第二电互连结构630,实现了形成第二纳米线120以及衬底100之间的电互连结构。从而,通过第一电互连结构540和第二电互连结构630,实现了形成互补鳍式场效应晶体管中纳米线与衬底之间的电互连结构,有利于实现进一步缩小集成电路的面积。

121.在本实施例中,所述第二电互连结构630与所述第一电互连结构540之间电绝缘。

122.在本实施例中,形成所述第二电互连结构630的方法包括:在所述第三开口610、所述第四开口620和所述介质层顶部表面形成第二电互连结构材料层(未图示);平坦化所述第二电互连结构材料层,直至暴露出所述介质层顶部表面。

123.形成所述第二电互连结构材料层的工艺包括化学气相沉积工艺、电镀工艺或者外延生长工艺。

124.在本实施例中,形成所述第二电互连结构材料层的工艺包括化学气相沉积工艺。

125.在本实施例中,所述第二电互连结构630的材料包括金属材料,例如钨或者钛。

126.在本实施例中,所述第一电互连结构540和所述第二电互连结构630位于所述互连区中。

127.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1