封装结构及其制造方法与流程

1.本发明涉及一种封装结构,特别是涉及一种封装结构及其制造方法。

背景技术:

2.现有技术的封装结构大部分都具有电磁屏蔽的功能,在第五代通信技术或车用领域,无线或数字高效能芯片除了电磁屏蔽需求外,其装置本身对内部芯片的散热设计,直接关系到整体效能与可靠度表现。但是,现有架构均着重在电磁屏蔽的功能,其散热效果仍有待改进。

3.因此,如何通过结构设计的改良,以提升具有防止电磁干扰的屏蔽效果的封装结构的散热效率,来克服上述的缺陷,已成为该项技术所欲解决的重要课题之一。

技术实现要素:

4.本发明所要解决的技术问题在于,针对现有技术的不足提供一种封装结构及其制造方法。

5.为了解决上述的技术问题,本发明所采用的其中一技术方案是提供一种封装结构,其包括:一电路板、一模封层、一导电金属板件以及一导电层。该电路板包括一基板及设置于该基板上的一第一电子元件。该模封层设置于该基板上且覆盖该第一电子元件,该模封层具有一顶表面、相对于该顶表面的一底表面及连接于该顶表面与该底表面之间的一侧表面。该导电金属板件设置在该顶表面上且邻近于该第一电子元件。该导电层设置在该侧表面上且电性连接于该导电金属板件。该导电金属板件及导电层为各自独立的元件。

6.为了解决上述的技术问题,本发明所采用的另外一技术方案是提供一种封装结构的制造方法,其包括:提供一电路板模块,该电路板模块包括一基板组件及设置在该基板组件上的多个第一电子元件;涂布一模封胶体于该电路板模块上,以覆盖多个该第一电子元件;设置一导电金属板件组于未固化的该模封胶体上;固化该模封胶体,以形成与该导电金属板件组相互结合的一模封结构,且该模封结构覆盖多个该第一电子元件;切割该导电金属板件组及该模封结构,以形成多个容置槽,且在多个该容置槽中分别裸露出该基板组件的一接地导电件;成形一导电涂层于多个该容置槽中,且该导电涂层电性连接于该接地导电件与该导电金属板件组;以及切割该导电涂层,以形成多个封装结构。

7.为了解决上述的技术问题,本发明所采用的另外一技术方案是提供一种封装结构的制造方法,其包括:提供一电路板模块,该电路板模块包括一基板组件及设置在该基板组件上的多个第一电子元件;涂布一模封胶体于该电路板模块上,以覆盖多个该第一电子元件;设置多个导电金属板件于未固化的该模封胶体上;固化该模封胶体,以形成与该导电金属板件相互结合的一模封结构,且该模封结构覆盖多个该第一电子元件;切割该模封结构及该基板组件,以形成多个待涂布的封装结构;以及成形一导电层于多个该待涂布的封装结构。

8.本发明的其中一有益效果在于,本发明所提供的封装结构及其制造方法,其能通

过“该导电金属板件设置在该顶表面上且邻近于该第一电子元件”、“该导电层设置在该侧表面上且电性连接于该导电金属板件”以及“该导电金属板件及导电层为各自独立的元件”的技术方案,以使得封装结构具有防止电磁干扰的屏蔽效果,并提升封装结构的散热效率。此外,本发明所提供的封装结构及其制造方法,也能通过“设置一导电金属板件组于未固化的该模封胶体上”以及“成形一导电涂层于多个该容置槽中,且该导电涂层电性连接于该接地导电件与该导电金属板件组”以使得封装结构具有防止电磁干扰的屏蔽效果,并提升封装结构的散热效率。

9.为使能更进一步了解本发明的特征及技术内容,请参阅以下有关本发明的详细说明与附图,然而所提供的附图仅用于提供参考与说明,并非用来对本发明加以限制。

附图说明

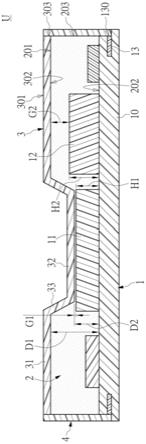

10.图1为本发明第一实施例的封装结构的其中一实施方式的剖视示意图。

11.图2为本发明第一实施例的封装结构的另外一实施方式的剖视示意图。

12.图3为本发明第一实施例的封装结构的再一实施方式的剖视示意图。

13.图4为本发明第二实施例的封装结构的制造方法的流程图。

14.图5为本发明第二实施例的封装结构的制造方法的步骤s106的示意图。

15.图6为本发明第二实施例的封装结构的制造过程的其中一示意图。

16.图7为本发明第二实施例的封装结构的制造过程的另外一示意图。

17.图8为本发明第二实施例的封装结构的制造过程的再一示意图。

18.图9为本发明第二实施例的封装结构的制造过程的又一示意图。

19.图10为本发明第二实施例的封装结构的制造过程的另外再一示意图。

20.图11为图10的俯视示意图。

21.图12为本发明第二实施例的封装结构的制造过程的另外又一示意图。

22.图13为本发明第二实施例的封装结构的制造过程的另外又再一示意图。

23.图14为本发明第三实施例的封装结构的制造方法的流程图。

24.图15为本发明第三实施例的封装结构的制造过程的其中一示意图。

25.图16为本发明第三实施例的封装结构的制造过程的另外一示意图。

26.图17为本发明第三实施例的封装结构的制造过程的再一示意图。

27.图18为本发明第三实施例的封装结构的其中一实施方式的剖视示意图。

28.图19为本发明第三实施例的封装结构的另外一实施方式的剖视示意图。

29.主要组件符号说明:

30.u

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

封装结构

31.u

’ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

封装结构

32.1a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电路板模块

[0033]1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电路板

[0034]

10a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

基板组件

[0035]

10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

基板

[0036]

11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一电子元件

[0037]

12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二电子元件

[0038]

13

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接地导电件

[0039]

130

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

裸露表面

[0040]

2a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

模封胶体

[0041]

2a

’ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

模封结构

[0042]2ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

模封层

[0043]

201

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

顶表面

[0044]

202

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

底表面

[0045]

203

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

侧表面

[0046]

3a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电金属板件组

[0047]3ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电金属板件

[0048]

301

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

顶面

[0049]

302

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

底面

[0050]

303

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

侧面

[0051]

31

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本体部

[0052]

32

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

散热部

[0053]

33

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

连接部

[0054]

4a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电胶层

[0055]

4a

’ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电涂层

[0056]4ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

导电层

[0057]

s

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

容置槽

[0058]

g1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一预定间距

[0059]

g2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二预定间距

[0060]

d1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一预定距离

[0061]

d2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二预定距离

[0062]

d3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三预定距离

[0063]

d4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四预定距离

[0064]

h1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一预定高度

[0065]

h2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二预定高度

[0066]

h3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三预定高度

[0067]

h4

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四预定高度

具体实施方式

[0068]

以下是通过特定的具体实施例来说明本发明所公开有关“封装结构及其制造方法”的实施方式,本领域技术人员可由本说明书所公开的内容了解本发明的优点与效果。本发明可通过其他不同的具体实施例加以施行或应用,本说明书中的各项细节也可基于不同观点与应用,在不背离本发明的构思下进行各种修改与变更。另外,本发明的附图仅为简单示意说明,并非依实际尺寸的描绘,事先声明。以下的实施方式将进一步详细说明本发明的相关技术内容,但所公开的内容并非用以限制本发明的保护范围。另外,应当可以理解的是,虽然本文中可能会使用到“第一”、“第二”、“第三”等术语来描述各种元件,但这些元件

不应受这些术语的限制。这些术语主要是用以区分一元件与另一元件。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。

[0069]

[第一实施例]

[0070]

请参阅图1所示,图1为本发明第一实施例的封装结构的其中一剖视示意图。本发明提供一种封装结构u及其制造方法,第一实施例将先介绍封装结构u的整体架构,封装结构u的制造方法于后续实施例再行说明。另外,值得说明的是,在其中一实施方式中,本发明所提供的封装结构u及其制造方法可用于封装半导体元件、芯片或者电路,本发明不以此为限。此外,在其中一实施方式中,本发明所提供的封装结构u及封装结构u的制造方法可以应用在无线通信系统封装(rf system in package,rf sip)。

[0071]

接着,请再参阅图1所示,封装结构u可包括一电路板1、一模封层2、一导电金属板件3以及一导电层4。电路板1包括一基板10及设置于基板10上的一第一电子元件11。举例来说,电路板1可为印刷电路板(printed circuit board,pcb),第一电子元件11可为设置在基板10上的线路或芯片。此外,电路板1还可进一步包括设置于基板10上的一第二电子元件12及/或其他电子元件(图中未标号),第二电子元件12的可为设置在基板10上的线路或芯片等。然而,本发明不以上述所举的例子为限制。

[0072]

承上述,模封层2设置于基板10上且直接接触并覆盖第一电子元件11及第二电子元件12。模封层2具有一顶表面201、相对于顶表面201的一底表面202及连接于顶表面201与底表面202之间的一侧表面203。此外,导电金属板件3设置在模封层2的顶表面201上,且导电金属板件3在模封层2的顶表面201上的垂直投影与第一电子元件11及第二电子元件12在模封层2的顶表面201上的垂直投影至少部分重叠。此外,导电层4设置在模封层2的侧表面203上且电性连接于导电金属板件3,且导电金属板件3及导电层4为各自独立的元件。

[0073]

承上述,举例来说,模封层2的材质可为树脂,例如环氧树脂(epoxy)或硅胶(silicone),导电金属板件3为具有导电性的板材,例如一预成型的金属散热件(pre-formed metal foil),而导电层4为涂层,且导电层4由一涂覆层或一胶体所形成。然而,须说明的是,本发明不以模封层2、导电金属板件3及导电层4的实际材质为限制。此外,须说明的是,导电金属板件3与导电层4为各自独立的元件所代表的是导电金属板件3的材质与导电层4的材质完全不同,或者是导电金属板件3的材质与导电层4的材质都包括相同的基础材质,但导电金属板件3的材质与导电层4的材质都分别进一步加入了不同特性的材质,而使得导电金属板件3的材质特性与导电层4的材质特性不同。

[0074]

承上述,导电金属板件3具有一顶面301、相对于顶面301的一底面302及连接于顶面301与底面之间的侧面303,且导电金属板件3的底面302可黏着于模封层2的顶表面201上。此外,导电层4同时抵靠在模封层2的侧表面203及导电金属板件3的侧面303上,以使得导电层4电性连接于导电金属板件3。此外,以本发明而言,电路板1还可进一步包括一接地导电件13,接地导电件13可设置在基板10上。导电金属板件3与导电层4电性连接于接地导电件13,且导电层4电性连接于导电金属板件3与接地导电件13之间,即,导电层4串联于导电金属板件3与接地导电件13之间的导电路径上。此外,举例来说,接地导电件13包括相对于基板10裸露的一裸露表面130,导电层4同时抵靠在模封层2的侧表面203、导电金属板件3

的侧面303及裸露表面130上,以使得导电层4电性连接于导电金属板件3及接地导电件13。然而,在其他实施方式中,导电层4也可以同时抵靠在模封层2的侧表面203、导电金属板件3的侧面303、导电金属板件3的至少一部分的顶面301及接地导电件13的裸露表面130上,以使得导电层4电性连接于导电金属板件3及接地导电件13。此外,在其他实施方式中,导电层4也可以同时抵靠在模封层2的侧表面203、模封层2的顶表面201、导电金属板件3的侧面303及接地导电件13的裸露表面130上,以使得导电层4电性连接于导电金属板件3及接地导电件13。换句话说,本发明不以导电层4是抵靠在模封层2及导电金属板件3的哪一个表面为限制。藉此,导电金属板件3及导电层4可利用电路板1上的接地导电件13的接地路径而接地。此外,利用导电金属板件3及导电层4接地的作用,也可以使得封装结构u具有防止电磁干扰的屏蔽效果。

[0075]

接着,请再参阅图1所示,以本发明而言,在其中一实施方式中,第一电子元件11可为电路板1上产生最大热能的元件,且导电金属板件3设置在模封层2的顶表面201上且邻近于第一电子元件11。藉此,由于导电金属板件3邻近于第一电子元件11,所以本发明能利用导电金属板件3增加第一电子元件11的散热效率。较佳地,以本发明而言,导电金属板件3与第一电子元件11之间仅具有模封层2,也就是说,导电金属板件3的底面302是直接接触且覆盖在模封层2的顶表面201上。然而,在其他实施方式中,导电金属板件3与第一电子元件11之间也可以设置有一导热垫(thermal pad)或散热膏,本发明不以此为限。此外,须说明的是,本发明是以导电金属板件3与第一电子元件11之间仅具有模封层2,且导电金属板件3的底面302紧邻第一电子元件11作为举例说明。举例来说,第一预定间距g1可小于500微米(micrometer,μm),较佳地,第一预定间距g1可小于100微米。藉此,第一电子元件11能尽可能的紧邻导电金属板件3,而提升第一电子元件的散热效率,然而本发明不以此为限。

[0076]

接着,请参阅图2所示,图2为本发明第一实施例的封装结构的另外一实施方式的剖视示意图。由图2与图1的比较可知,在图2的实施方式中,可利用改变导电金属板件3的形状,而使得导电金属板件3更邻近于第一电子元件11,以增加第一电子元件11的散热效率。此外,相较于图1中的实施方式是将接地导电件13设置在基板10的表面上,在图2的实施方式中,接地导电件13是嵌埋在基板10中。然而,本发明不以接地导电件13的设置位置为限制。值得说明的是,在某些情况下,第二电子元件12与导电金属板件3之间的距离过近时,有可能会受到干扰,例如串扰(cross talk)。因此,为了同时达到增加第一电子元件11的散热效率,且避免第二电子元件12受到干扰,在图2的实施方式中,第二电子元件12较第一电子元件11远离于导电金属板件3,即,第一电子元件11较第二电子元件12更邻近于导电金属板件3。此外,须说明的是,图2中的封装结构u的其他构件的特征都与前述图1的封装结构u相仿,在此不再赘述。

[0077]

接着,在图2的实施方式中,第一电子元件11具有一第一预定高度h1,第二电子元件12具有一第二预定高度h2,第一预定高度h1小于第二预定高度h2。此外,第一电子元件11与导电金属板件3之间具有一第一预定间距g1,第二电子元件12与导电金属板件3之间具有一第二预定间距g2,第一预定间距g1小于第二预定间距g2。举例来说,第一预定间距g1可小于500微米,较佳地,第一预定间距g1可小于100微米,然而本发明不以此为限。

[0078]

承上述,导电金属板件3可包括一本体部31及连接于本体部31的一散热部32,散热部32可相对于本体部31呈凹陷状的设置,以使得散热部32能邻近于第一电子元件11设置,

且散热部32较本体部31更邻近于基板10。此外,散热部32在基板10上的垂直投影与第一电子元件11在基板10上的垂直投影至少部分重叠,本体部31可邻近于第二电子元件12设置,且本体部31在基板10上的垂直投影与第二电子元件12在基板10上的垂直投影至少部分重叠。此外,导电金属板件3还可进一步包括连接于本体部31与散热部32之间的连接部33,位于本体部31上的底面302与位于散热部32上的底面302彼此平行,且位于连接部33上的底面302倾斜于位于本体部31上的底面302及位于散热部32上的底面302。

[0079]

承上述,进一步来说,位于导电金属板件3的本体部31上的底面302至模封层2的底表面202之间具有一第一预定距离d1,位于导电金属板件3的散热部32上的底面302至模封层2的底表面202之间具有一第二预定距离d2,第一预定距离d1大于第二预定距离d2。

[0080]

接着,请参阅图3所示,图3为本发明第一实施例的封装结构的再一实施方式的剖视示意图。由图3与图3的比较可知,在图3的实施方式中,可因应第一电子元件11的高度而改变导电金属板件3的形状,以增加第一电子元件11的散热效率。此外,须说明的是,图3中的封装结构u的其他构件的特征都与前述图1的封装结构u相仿,在此不再赘述。

[0081]

承上述,在图3的实施方式中,第一电子元件11具有一第三预定高度h3,第二电子元件12具有一第四预定高度h4,第三预定高度h3大于第四预定高度h4。此外,第一电子元件11与导电金属板件3之间具有一第一预定间距g1,第二电子元件12与导电金属板件3之间具有一第二预定间距g2,第一预定间距g1小于第二预定间距g2。举例来说,第一预定间距g1可小于500微米,较佳地,第一预定间距g1可小于100微米,然而本发明不以此为限。

[0082]

详细来说,在图3的实施方式中,导电金属板件3的散热部32相对于导电金属板件3的本体部31呈凸起状,散热部32在基板10上的垂直投影与第一电子元件11在基板10上的垂直投影至少部分重叠,且本体部31较散热部32更邻近于基板10。此外,位于导电金属板件3的本体部31上的底面302至模封层2的底表面202之间具有一第三预定距离d3,位于导电金属板件3的散热部32上的底面302至模封层2的底表面202之间具有一第四预定距离d4,第三预定距离d3小于第四预定距离d4。此外,位于本体部31上的底面302与位于散热部32上的底面302彼此平行,且位于连接部33上的底面302倾斜于位于本体部31上的底面302及位于散热部32上的底面302。

[0083]

[第二实施例]

[0084]

首先,请参阅图4及图6至图13所示,图4为本发明第二实施例的封装结构的制造方法的流程图,图6至图13分别为本发明第二实施例的封装结构的制造过程的示意图。须说明的是,第二实施例所提供的封装结构u的制造方法中的各个元件特征都与前述实施例相仿,在此不再赘述。此外,第二实施例是以图2的实施方式作为举例说明,图1及图3所提供的封装结构u也可以利用第二实施例所提供的封装结构u的制造方法所制作。

[0085]

接着,请再参阅图4及图6,如步骤s101所示:提供一电路板模块1a,电路板模块1a包括一基板组件10a及设置在基板组件10a上的多个第一电子元件11。举例来说,基板组件10a可由前述实施例的多个基板10所构成,也就是多个基板10还连接在一起未被切割时的状态。此外,多个第二电子元件12及多个接地导电件13也可以设置在基板组件10a上。

[0086]

接着,请再参阅图4及图7,如步骤s102所示:涂布一模封胶体2a于电路板模块1a上。举例来说,可利用模封胶体2a覆盖多个第一电子元件11及第二电子元件12。此外,在涂布模封胶体2a于电路板模块1a上的步骤中,是在具有一预定真空压力的一真空环境下涂布

模封胶体2a,以覆盖多个第一电子元件11及第二电子元件12。换句话说,可以利用一真空印刷封装机台进行真空印刷封装制程(vacuum printing encapsulation system,vpes)将模封胶体2a涂布在电路板模块1a上,以覆盖多个第一电子元件11及第二电子元件12,然而本发明不以此为限。在其他实施方式中,在涂布模封胶体2a于电路板模块1a上的步骤中,也可以是在一大气压力环境下涂布模封胶体2a。另外,须说明的是,模封胶体2a的材质及特性如同前述实施例中的模封层2,在此不再赘述。

[0087]

接着,请再参阅图4、图8及图9,如步骤s103所示:设置一导电金属板件组3a于未固化的模封胶体2a上。以本发明而言,由于导电金属板件组3a是设置在未固化的模封胶体2a上,因此,当导电金属板件组3a具有一凹或凸的形状时,未固化的模封胶体2a可以沿着导电金属板件组3a的轮廓流动,且导电金属板件组3a能进一步的邻近第一电子元件11。

[0088]

接着,请再参阅图4及图9,如步骤s104所示:固化模封胶体2a,以形成与导电金属板件组3a相互结合的一模封结构2a’。举例来说,在固化模封胶体2a,以形成模封结构2a’的步骤中,可以通过自然固化或加热固化的方式来固化模封胶体2a,以形成固化及/或定型的模封结构2a’。举例来说,加热固化的方式可以为烘烤。此外,须说明的是,模封结构2a’是由前述实施例的多个模封层2所构成,也就是多个模封层2还连接在一起未被切割时的状态。藉此,由于导电金属板件组3a是设置在未固化的模封胶体2a上,因此,当模封胶体2a固化成模封结构2a’时,导电金属板件组3a可黏着在模封结构2a’上。也就是说,在固化模封胶体2a,以形成模封结构2a’的步骤中,导电金属板件组3a也会一并结合在模封结构2a’上,即,导电金属板件组3a是利用键结结合的方式而使得导电金属板件组3a直接接触且黏着在模封结构2a’上。

[0089]

接着,请再参阅图4、图10及图11,如步骤s105所示:切割导电金属板件组3a及模封结构2a’,以形成多个容置槽s。举例来说,在切割导电金属板件组3a及模封结构2a’,以形成多个容置槽s的步骤中,能进一步地在多个容置槽s中分别裸露出基板组件10a的一接地导电件13。换句话说,在切割导电金属板件组3a及模封结构2a’,以形成多个容置槽s的步骤中,导电金属板件组3a被切割而形成多个导电金属板件3,模封结构2a’被切割而形成多个模封层2。

[0090]

承上述,每一导电金属板件3分别对应于相对应的第一电子元件11及第二电子元件12,每一导电金属板件3包括一本体部31及连接于本体部的一散热部32,散热部32在基板组件10a上的垂直投影与第一电子元件11在基板组件10a上的垂直投影至少部分重叠,且本体部31在基板组件10a上的垂直投影与第二电子元件12在基板组件10a上的垂直投影至少部分重叠。此外,当本案发明第二实施例应用在图2的实施方式中时,散热部32相对于本体部呈凹陷状,且散热部32较该本体部31更邻近于基板组件10a。然而,当本案发明第二实施例应用在图3的实施方式中时,散热部32相对于本体部呈凸起状,且本体部31较散热部32更邻近于基板组件10a。

[0091]

此外,在图2实施方式中,由于接地导电件13是嵌埋在基板10之中,因此,在切割导电金属板件组3a及模封结构2a’,以形成多个容置槽s的步骤中,还可进一步包括切割基板组件10a的至少一部分,以在多个容置槽s中分别裸露出位于基板组件10a中的接地导电件13。此外,须说明的是,为了后续制程的便利性,在切割基板组件10a的至少一部分的步骤中,可以不完全切穿基板组件10a,然而本发明不以此为限。

[0092]

接着,请再参阅图4、图5及图12,图5为本发明第二实施例的封装结构的制造方法的步骤s106的示意图。如步骤s106所示:成形一导电涂层4a’于多个容置槽s中。举例来说,该导电涂层4a’能电性连接于接地导电件13与导电金属板件组3a。

[0093]

承上述,在成形导电涂层4a’于多个容置槽s中的步骤中,包括下列步骤:如步骤s1061所示,涂布一导电胶层4a于多个容置槽s中。举例来说,在涂布导电胶层4a于多个容置槽s中的步骤中,是在具有一预定真空压力的一真空环境下涂布导电胶层4a,然而本发明不以此为限。换句话说,可以利用一真空印刷封装机台进行真空印刷封装制程将导电胶层4a涂布在多个容置槽s中,然而本发明不以此为限。在其他实施方式中,在涂布导电胶层4a于多个容置槽s中的步骤中,也可以是在一大气压力环境下涂布导电胶层4a。此外,须说明的是,导电胶层4a是一涂覆层或一胶体,且可以利用喷涂或印刷而涂布在多个容置槽s中。进一步来说,如步骤s1062所示,固化导电胶层4a,以形成导电涂层4a’。举例来说,在固化导电胶层4a的步骤中,可以通过自然固化或加热固化的方式来固化导电胶层4a,以形成固化及/或定型的导电涂层4a’。藉此,在步骤s106中,能通过成形一导电胶层4a于多个容置槽s,而形成电性连接于接地导电件13与导电金属板件组3a的导电涂层4a’。此外,导电胶层4a为导电涂层4a’固化前的形态,而导电涂层4a’则是两个相邻的导电层4还连接在一起未被切割时的形态。

[0094]

接着,请再参阅图4及图13,如步骤s107所示,切割导电涂层4a’,以形成多个封装结构u。举例来说,可沿着一预定切割线进行切割,而形成多个封装结构u。此外,在切割导电涂层4a’,以形成多个封装结构u。的步骤中,还可进一步包括切割基板组件10a,以形成多个封装结构u。藉此,导电涂层4a’被切割而形成多个导电层4,基板组件10a被切割而形成多个基板10,且每一基板10上分别设置有相对应的第一电子元件11。

[0095]

[第三实施例]

[0096]

首先,请参阅图14至图18所示,图14为本发明第三实施例的封装结构的制造方法的流程图,图15至图17分别为本发明第三实施例的封装结构的制造过程的示意图,图18为本发明第三实施例的封装结构的剖视示意图。须说明的是,在第三实施例所提供的封装结构u的制造方法中的各个元件特征都与前述实施例相仿,在此不再赘述。

[0097]

承上述,请再参阅图6、图7及图14所示,如步骤s201所示:提供一电路板模块1a,电路板模块1a包括一基板组件10a及设置在基板组件10a上的多个第一电子元件11。接着,如步骤s202所示:涂布一模封胶体2a于电路板模块1a上。须说明的是,步骤s201及步骤s202的制造过程,都与前述步骤s101及步骤s102的制造过程相仿,在此不再赘述。

[0098]

接着,请再参阅图14及图15所示,如步骤s203所示,设置多个导电金属板件3于未固化的模封胶体2a上。以本发明而言,每一个导电金属板件3分别对应于相对应的第一电子元件11。此外,由于导电金属板件3是设置在未固化的模封胶体2a上,因此,当导电金属板件3具有一凹或凸的形状时,未固化的模封胶体2a可以沿着导电金属板件3的轮廓流动,且导电金属板件3能进一步的邻近第一电子元件11。换句话说,相较于步骤s103,步骤s203是设置多个导电金属板件3于未固化的模封胶体2a上,以使得导电金属板件3在挤压未固化的模封胶体2a时,能增加未固化的模封胶体2a的可流动性。

[0099]

接着,请再参阅图14及图16所示,如步骤s204所示,固化模封胶体2a,以形成与多个导电金属板件3相互结合的一模封结构2a’。藉此,多个电金属板件3可黏着在模封结构

2a’上。也就是说,在固化模封胶体2a,以形成模封结构2a’的步骤中,导电金属板件3也会一并结合在模封结构2a’上,即,导电金属板件3是利用键结结合的方式而使得导电金属板件3直接接触且黏着在模封结构2a’上。另外,在步骤s204中的固化模封胶体2a的方式,与步骤s104相仿,在此不再赘述。

[0100]

接着,请再参阅图14及图17所示,如步骤s205所示:切割模封结构2a’及基板组件10a,以形成多个待涂布的封装结构u’。举例来说,在切割模封结构2a’及基板组件10a,以形成多个待涂布的封装结构u’的步骤中,能进一步地在两个相邻的待涂布的封装结构u’中裸露出基板组件10a的一接地导电件13。此外,在切割模封结构2a’及基板组件10a,以形成多个待涂布的封装结构u’的步骤中,模封结构2a’被切割而形成多个模封层2,且基板组件10a被切割而形成多个基板10。换句话说,在步骤s205中,可完全切穿模封结构2a’及基板组件10a,而形成多个待涂布的封装结构u’。

[0101]

接着,请再参阅图14及图18所示,如步骤s206所示:成形一导电层4于待涂布的封装结构u’上。举例来说,在成形导电层4于待涂布的封装结构u’上的步骤中,可以利用喷涂或印刷而先涂布一导电胶层4a于涂布的封装结构u’的侧表面203上,接着,再固化导电胶层4a,以形成导电层4。换句话说,相较于前述第二实施例,在第三实施例中,是将每一个待涂布的封装结构u’分别涂布导电层4,且导电层4可形成在待涂布的封装结构u’的侧表面上。

[0102]

承上述,请一并参阅图2所示,由图2与图18的比较可知,在第三实施例的步骤s205中,是利用切割模封结构2a’及基板组件10a,而形成多个彼此分离的待涂布的封装结构u’,因此,在设置导电层4时,导电层4不仅可形成在模封层2的侧表面203、导电金属板件3的侧面303及接地导电件13的裸露表面130上,也能够完全覆盖基板10的外侧表面。也就是说,本发明主要是利用导电层4电性连接于导电金属板件3及接地导电件13之间,而不以导电层所设置的位置为限制。另外,值得说明的是,图18的封装结构u的其他结构特征与图2的封装结构u的结构特征相仿,在此不再赘述。

[0103]

接着,请参阅图19所示,由图19与图18的比较可知,在图18的实施方式中,导电层4同时抵靠在模封层2的侧表面203、导电金属板件3的侧面303及裸露表面130上,以使得导电层4电性连接于导电金属板件3及接地导电件13。但是,在图19的实施方式中,导电层4同时抵靠在模封层2的侧表面203、模封层2的顶表面201、导电金属板件3的侧面303及接地导电件13的裸露表面130上,以使得导电层4电性连接于导电金属板件3及接地导电件13。换句话说,为了形成如图19所示的封装结构u,在步骤s205:切割模封结构2a’及基板组件10a,以形成多个待涂布的封装结构u’的步骤中,可以预留一相对于导电金属板件3裸露的模封层2,也就是说,模封层2的顶表面201可相对于、导电金属板件3裸露。藉此,在步骤s206:成形一导电层4于待涂布的封装结构u’上的步骤中,可以将一导电胶层4a涂布在待涂布的封装结构u’的侧表面203以及相对于导电金属板件3裸露的模封层2的顶表面201上。接着,再固化导电胶层4a,而形成多个封装结构u。

[0104]

[实施例的有益效果]

[0105]

本发明的其中一有益效果在于,本发明所提供的封装结构u及其制造方法,其能通过“导电金属板件3设置在顶表面201上且邻近于第一电子元件11”、“导电层4设置在侧表面203上且电性连接于导电金属板件3”以及“导电金属板件3及导电层4为各自独立的元件”的技术方案,以使得封装结构u具有防止电磁干扰的屏蔽效果,并提升封装结构u的散热效率。

此外,本发明所提供的封装结构u及其制造方法,也能通过“设置一导电金属板件组3a于未固化的该模封胶体2a上”以及“成形一导电涂层4a’于多个容置槽s中,且导电涂层4a’电性连接于接地导电件13与导电金属板件组3a”以使得封装结构u具有防止电磁干扰的屏蔽效果,并提升封装结构u的散热效率。

[0106]

以上所公开的内容仅为本发明的优选可行实施例,并非因此局限本发明的申请专利范围,所以凡是运用本发明说明书及附图内容所做的等同技术变化,均包含于本发明的申请专利范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1