半导体模块装置的制作方法

[0001]

本公开涉及包括可控半导体元件的半导体模块装置。

背景技术:

[0002]

功率半导体模块装置往往包括布置在壳体中的至少一个半导体衬底。包括多个可控半导体元件(例如,半桥配置的两个晶体管元件)的半导体装置布置在至少一个衬底上。每个衬底通常包括衬底层(例如,陶瓷层)、沉积在衬底层的第一侧上的第一金属化层和沉积在衬底层的第二侧上的第二金属化层。可控半导体元件例如安装在第一金属化层上。第二金属化层可以可选地附接到基板。可控半导体元件通常通过焊接或烧结技术安装到半导体衬底。

[0003]

需要一种具有令人满意的电磁兼容性(emc)促进特性的半导体模块装置,该半导体模块装置易于制造而无需添加制造步骤,并且即使对于高反向电压等级也能满足对绝缘电压的要求。

技术实现要素:

[0004]

一种半导体模块装置包括壳体和布置在壳体内部的至少一对半导体衬底。每对半导体衬底包括第一半导体衬底和第二半导体衬底。所述第一半导体衬底包括布置在第一金属化层与第三金属化层之间的第一电介质绝缘层、以及布置在所述第三金属化层与第二金属化层之间的第二电介质绝缘层。第二半导体衬底包括布置在第一金属化层与第三金属化层之间的第一电介质绝缘层、以及布置在第三金属化层与第二金属化层之间的第二电介质绝缘层。第一半导体衬底的第三金属化层电耦合到第一电势,并且第二半导体衬底的第三金属化层电耦合到与第一电势相反的第二电势。

[0005]

参考以下附图和说明书可以更好地理解本发明。附图中的部件不一定按比例绘制,而是将重点放在说明本发明的原理上。在附图中,类似的附图标记在不同的视图中指示对应的部分。

附图说明

[0006]

图1示意性地示出了半导体模块装置的截面图。

[0007]

图2示意性地示出了示例性多层半导体衬底的截面图。

[0008]

图3示意性地示出了示例性半导体模块装置的截面图。

[0009]

图4是示例性半导体装置的电路图。

[0010]

图5是示例性半导体模块装置的俯视图。

[0011]

图6是另一个示例性半导体模块装置的俯视图。

[0012]

包括图7a至图7c的图7示出了根据另一个示例的半导体衬底的俯视图。

具体实施方式

[0013]

在下面的具体实施方式中,参考了附图。附图示出了在其中可以实践本发明的具体示例。应当理解,除非另外特别指出,否则关于各个示例描述的特征和原理可以彼此组合。在说明书以及权利要求中,被指定为“第一元件”、“第二元件”、“第三元件”等的某些元件不应被理解为列举。相反,这样的指定仅用于提出不同的“元件”。换言之,例如,“第三元件”的存在不要求“第一元件”和“第二元件”的存在。如本文描述的电线可以是单个导电元件,或者包括串联和/或并联连接的至少两个个体的导电元件。电线可以包括金属和/或半导体材料,并且可以是永久导电的(即,不可切换的)。电线可以具有与流过其的电流的方向无关的电阻率。本文描述的半导体主体可以由(掺杂的)半导体材料制成,并且可以是半导体芯片或被包括在半导体芯片中。半导体主体具有电连接焊盘并且包括至少一个具有电极的半导体元件。焊盘电连接到电极,这包括焊盘是电极,并且反之亦然。

[0014]

参考图1,示意性地示出了功率半导体模块装置100的截面图。功率半导体模块装置100包括壳体17和半导体衬底10。半导体衬底10包括电介质绝缘层11、附接到电介质绝缘层11的(结构化的)第一金属化层111、以及附接到电介质绝缘层11的(结构化的)第二金属化层112。电介质绝缘层11设置在第一和第二金属化层111、112之间。

[0015]

第一和第二金属化层111、112中的每个可以由以下材料之一组成或包括以下材料之一:铜;铜合金;铝;铝合金;或在功率半导体模块装置的操作期间保持固态的任何其他金属或合金。半导体衬底10可以是陶瓷衬底,换言之,其中电介质绝缘层11是陶瓷(例如薄陶瓷层)的衬底。陶瓷可以由以下材料之一组成或包括以下材料之一:氧化铝;氮化铝;氧化锆;氮化硅;氮化硼;或任何其他电介质陶瓷。例如,电介质绝缘层11可以由以下材料之一组成或包括以下材料之一:al2o3、aln、sic、beo或si3n4。例如,衬底10可以是例如直接铜键合(dcb)衬底、直接铝键合(dab)衬底、或活性金属钎焊(amb)衬底。此外,衬底10可以是绝缘金属衬底(ims)。绝缘金属衬底一般包括电介质绝缘层11,例如,电介质绝缘层11包括诸如环氧树脂或聚酰亚胺的(填充)材料。例如,电介质绝缘层11的材料可以填充有陶瓷颗粒。这样的颗粒可以包括例如si2o、al2o3、aln、或bn,并且可以具有处于约1μm与约50μm之间的直径。衬底10也可以是具有非陶瓷的电介质绝缘层11的常规印刷电路板(pcb)。例如,非陶瓷的电介质绝缘层11可以由固化树脂组成或包括固化树脂。

[0016]

半导体衬底10布置在壳体17中。在图1所示的示例中,半导体衬底10布置在形成壳体17的底表面的基板12上,而壳体17本身仅包括侧壁和盖。然而,这仅是示例。壳体17还包括底表面并且半导体衬底10和(可选的)基板12布置在壳体17内部也是可能的。在一些功率半导体模块装置100中,多于一个半导体衬底10布置在单个基板12上或壳体17的底表面上。

[0017]

一个或多个半导体主体120可以布置在至少一个半导体衬底10上。布置在至少一个半导体衬底10上的半导体主体120中的每个可以包括二极管、igbt(绝缘栅双极晶体管)、mosfet(金属氧化物半导体场效应晶体管)、jfet(结型场效应晶体管)、hemt(高电子迁移率晶体管)、和/或任何其他合适的半导体元件。

[0018]

一个或多个半导体主体120可以在至少一个半导体衬底10上形成半导体装置。在图1中,仅示例性地示出了两个半导体主体120。图1中的半导体衬底10的第二金属化层112是连续的层。在图1所示的示例中,第一金属化层111是结构化的层。在该上下文中,“结构化的层”是指第一金属化层111不是连续的层,而是在该层的不同区段之间包括凹陷。在图1中

示意性地示出了这样的凹陷。在该示例中,第一金属化层111包括三个不同的区段。然而,这仅是示例。任何其他数量的区段都是可能的。可以将不同的半导体主体120安装到第一金属化层111的相同或不同的区段。第一金属化层111的不同的区段可以不具有电连接部,或者可以使用例如键合线13电连接到一个或多个其他区段。仅列举几个示例,例如,电连接部13也可以包括键合带、连接板或导体轨。一个或多个半导体主体120可以通过导电连接层130电和机械连接到半导体衬底10。例如,这样的导电连接层可以是焊料层、导电粘合剂层、或烧结的金属粉末(例如,烧结的银粉末)层。

[0019]

根据其他示例,第二金属化层112也有可能是结构化的层。还有可能完全省略第二金属化层112。例如,第一金属化层111一般也有可能是连续的层。

[0020]

图1所示的功率半导体模块装置100还包括端子元件14。端子元件14电连接到第一金属化层111,并在壳体17的内部和外部之间提供电连接。端子元件14可以以第一端电连接到第一金属化层111,而端子元件14中的每个的第二端141伸出到壳体17之外。端子元件14可以在其相应的第二端141被从外部电接触。端子元件14的第一部分可以在竖直方向y上延伸穿过壳体17的内部。竖直方向y是垂直于半导体衬底10的顶表面的方向,其中,半导体衬底10的顶表面是在其上安装到少一个半导体主体120的表面。然而,图1中所示的端子元件14仅是示例。端子元件14可以以任何其他方式实施,并且可以布置在壳体17内的任何位置。例如,一个或多个端子元件14可以布置为靠近壳体17的侧壁或与壳体17的侧壁相邻。端子元件14也可以突出穿过壳体17的侧壁而不是穿过盖。

[0021]

半导体主体120均可以包括芯片焊盘金属化(未具体示出),例如,源极、漏极、发射极、集电极、阳极、阴极或栅极金属化。芯片焊盘金属化一般提供用于电连接半导体主体120的接触表面。芯片焊盘金属化可以例如电接触连接层130、端子元件14、或电连接部13。芯片焊盘金属化可以由诸如铝、铜、金或银的金属组成或包括诸如铝、铜、金或银的金属。电连接部13和端子元件14也可以由诸如铝、铜、金或银的金属组成或包括诸如铝、铜、金或银的金属。

[0022]

功率半导体模块装置100一般还包括浇铸化合物15。浇铸化合物15例如可以由硅酮凝胶组成或包括硅酮凝胶,或者可以是刚性模制化合物。浇铸化合物15可以至少部分地填充壳体17的内部区域,由此覆盖布置在半导体衬底10上的部件和电连接部。端子元件14可以部分地嵌入在浇铸化合物15中。然而,至少它们的第二端141未被浇铸化合物15覆盖并且从浇铸化合物15穿过壳体17突出到壳体17的外部。浇铸化合物15被配置为保护功率半导体模块100内部(特别是壳体17内部)的部件和电连接部免受某些环境条件和机械损坏。

[0023]

如上所述,两个或更多半导体主体120可以在至少一个半导体衬底10上形成半导体装置。将两个或更多半导体主体120布置成半桥装置仅仅是一个示例。半导体装置也可以包括诸如anpc(有源中性点钳位)拓扑。anpc拓扑包括几个可控半导体元件(例如,六个可控半导体元件),每个半导体元件具有形成在第一负载电极(例如,源极电极或发射极电极)和第二负载电极(例如漏极电极或集电极电极)与控制电极(例如,栅极或基极电极)之间的负载路径。可以在半导体装置中实施的其他拓扑例如包括中性点钳位(npc)拓扑(例如,所谓的npc1或npc2拓扑)。

[0024]

现在参考图2,示例性地示出了多层半导体衬底10。除了上面已经相对于图1描述的电介质绝缘层11、第一金属化层111和第二金属化层112之外,半导体衬底10还可以包括

附加的电介质绝缘层和第三金属化层。换言之,图2中所示的多层半导体衬底10包括第一电介质绝缘层11a、第二电介质绝缘层11b、第一金属化层111、第二金属化层112和第三金属化层113。金属化层113布置在第一电介质绝缘层11a和第二电介质绝缘层11b之间。第一金属化层111布置在第一电介质绝缘层11a的与在其上布置第三金属化层113的表面相对的表面上。第二金属化层112布置在第二电介质绝缘层11b的与在其上布置第三金属化层113的表面相对的表面上。换句话说,第一电介质绝缘层11a布置在第一金属化层111与第三金属化层113之间,并且第二电介质绝缘层11b布置在第二金属化层112与第三金属化层113之间。

[0025]

在图2的示例中,在第一金属化层111与第三金属化层113之间或在第二金属化层112与第三金属化层113之间未提供电连接部。在图2的示例中,金属化层111、112、113是连续的金属化层。然而,图2的多层半导体衬底10仅是示例。一般而言,半导体衬底10也有可能包括多于两个电介质绝缘层和多于三个金属化层。任何附加的电介质绝缘层11可以由与上面相对于图1已经相对于电介质绝缘层11描述的相同的材料组成或包括所述材料。任何附加的金属化层可以由与上面相对于图1已经相对于第一和第二金属化层111、112描述的相同的材料组成或包括所述材料。

[0026]

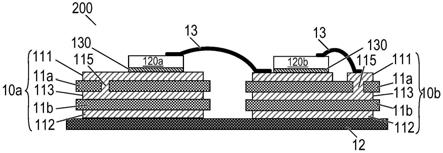

现在参考图3,示例性地示出了半导体模块装置200。半导体模块装置200包括布置在基板12上的两个多层半导体衬底10a、10b。两个多层半导体衬底10a、10b中的每个类似于上面相对于图2已经描述的多层半导体衬底10。然而,在图3的示例中,第一多层半导体衬底10a包括为连续的层的第一金属化层111。此外,在第一金属化层111与第三金属化层113之间提供电连接部。例如,可以在第一电介质绝缘层11a中提供所谓的过孔115。过孔115可以填充有导电材料。例如,这样的材料可以与第一、第二和第三金属化层111、112、113的材料等同。过孔115可以由第一电介质绝缘层11a中的孔或开口形成。例如,这样的孔或开口可以具有圆化的、矩形的或正方形的横截面。然而,其他横截面也是可能的。过孔一般从第一金属化层111穿过第一电介质绝缘层11a延伸到第三金属化层113。

[0027]

第二半导体衬底10b的第一金属化层111是结构化的层。在图3的示例中,第二衬底10b的第一金属化层111包括两个单独的区段。然而,如将在下面进一步描述的,半导体衬底10的第一金属化层111也有可能包括多于两个单独的区段。区段的数量例如可以取决于在半导体衬底10a、10b上实施的半导体装置的种类。第二衬底10b的第一金属化层111的区段之一电耦合到第二半导体衬底10b的第三金属化层113。如上面相对于第一半导体衬底10a已经描述的,可以在第一电介质绝缘层11a中设置过孔115(过孔115可以延伸穿过第一电介质绝缘层11a),以便将第一金属化层111的第二区段耦合到第三金属化层113。在图3所示的示例中,第一半导体衬底10a的第三金属化层113和第二半导体衬底10b的第三金属化层113都是连续的层。然而,一般而言,第三金属化层113也有可能是结构化的层。

[0028]

在图3的装置中,第一半导体主体120a布置在第一半导体衬底10a上,并且第二半导体主体120b布置在第二半导体衬底10b上。第一半导体主体120a通过导电连接层130电耦合到第一半导体衬底10a的第一金属化层111。第一半导体主体120a例如经由诸如键合线的电连接部13进一步电耦合到第二半导体衬底10b的第一金属化层111。电连接部13可以机械连接到第一半导体主体120a的顶表面,其中,半导体主体120的顶表面是背离其安装到的半导体衬底10的表面。第二半导体主体120b通过导电连接层130电耦合到第二半导体衬底10b的第一金属化层111的第一区段。第二半导体主体120b例如经由诸如键合线的电连接部13

进一步电耦合第二半导体衬底10b的第一金属化层111的第二区段。电连接部13可以机械连接到第二半导体主体120b的顶表面。以这种方式,第一半导体主体120a和第二半导体主体120b可以例如形成半桥装置。

[0029]

图4是示例性半桥装置的电路图。半桥装置被配置为将在半桥装置的输入端1、2处提供的dc电压转换成在半桥装置的输出端3处提供的ac电压。可以将ac电压提供给例如耦合到半桥装置的输出端3的负载(未示出)。半桥装置耦合在被配置为可操作地耦合到第一电势的第一供应节点1与被配置为可操作地耦合到第二电势的第二供应节点2之间。第一电势可以是正电势dc+,并且第二电势可以是负电势dc-,以经由第一和第二供应节点1、2供应dc电压。第一和第二供应节点1、2形成半桥装置的输入端。

[0030]

半桥可以包括彼此串联耦合并且耦合在第一供应节点1和第二供应节点2之间的一个高侧开关s1(第一开关或第一可控半导体元件)和一个低侧开关s2(第二开关或第一可控半导体元件)。半桥装置可以被配置为驱动在其输出节点3处的负载(未具体示出)。该负载例如可以是电感负载。输出节点3电连接到高侧开关s1和低侧开关s2之间的公共节点。

[0031]

在图4的电路装置中,半桥装置的每个开关s1、s2被实施为igbt(绝缘栅双极晶体管)。开关s1、s2中的每个可以包括并联耦合到其相应的负载路径的内部或外部二极管元件d1、d2(续流二极管)。根据另一个示例,开关s1、s2中的每个包括彼此并联电耦合的两个或更多单独的开关元件(未示出)。

[0032]

第一开关s1和第二开关s2中的每个包括控制电极4、5和在第一负载电极和第二负载电极之间的可控负载路径。第一开关s1和第二开关s2的负载路径串联耦合并且耦合在第一供应节点1和第二供应节点2之间。

[0033]

现在参考图5,示意性地示出了示例性半导体装置的俯视图。图5的半导体装置可以对应于图4中所示的半桥装置。第一半导体衬底10a和第二半导体衬底10b布置在基板12上。如上面相对于图1已经描述的,基板12可以布置在半导体壳体17中。代替基板12,如果半导体装置不包括基板12,则半导体衬底10a、10b可以布置在壳体17的底表面上。一般而言,不管半导体模块装置是否包括基板12,第一半导体衬底10a和第二半导体衬底10b都布置在同一壳体17中。第一半导体衬底10a和第二半导体衬底10b形成一对半导体衬底。如图5所示,半导体装置可选地可以包括多于一对的半导体衬底10a、10b。在图5中,示意性地示出了两对半导体衬底10a、10b,其中,仅针对一对示出了基本特征,并且为了清楚起见,已经省略了第二对的基本特征。该装置甚至可以包括多于两对半导体衬底10a、10b。

[0034]

一般而言,半导体装置包括至少一对半导体衬底10a、10b。换言之,半导体装置包括偶数个(两个的倍数)半导体衬底10。至少一对半导体衬底中的每对包括第一半导体衬底10a和第二半导体衬底10b。第一和第二半导体衬底10a、10b中的每个包括至少两个电介质绝缘层11a、11b和至少三个金属化层111、112、113。换言之,每个半导体衬底10a、10b包括布置在两个电介质绝缘层11a、11b之间的至少一个中间金属化层113。如果半导体衬底10包括多于两个电介质绝缘层11,则可以存在多于一个中间金属化层。至少一个中间金属化层(图3中的第三金属化层113)与第一金属化层111的至少一个区段电接触,第一金属化层111是在其上安装或可以安装至少一个半导体主体120的外部金属化层。第一金属化层111仅与电介质绝缘层11之一(图5中的第一电介质绝缘层11a)直接接触。

[0035]

在图5所示的装置中,第一半导体衬底10a的第一金属化层111仅包括一个(单个/

不多于一个)区段。第一可控开关元件s1布置在第一半导体衬底10a的第一金属化层111上。此外,第一二极管元件d1布置在第一半导体衬底10a的第一金属化层111上。然而,第一二极管元件d1是可选的。第一半导体衬底10a的第一金属化层111的单个区段电耦合到第一半导体衬底10a的第三金属化层113(如图3所示)。第一半导体衬底10a的第一金属化层111可以形成或可以耦合到第一供应节点,其中,第一供应节点耦合到第一电势(例如,dc+)。换言之,第一金属化层111和电耦合到第一金属化层111的第三金属化层113都电耦合到第一电势。

[0036]

在图5的示例中,第二半导体衬底10b的第一金属化层111包括两个单独的区段1111、1112。第二可控开关元件s2布置在第二半导体衬底10b的第一金属化层111的第一区段1111上。此外,第二二极管元件d2布置在第二半导体衬底10b的第一金属化层111的第一区段1111上。然而,第二二极管元件d2是可选的。第一可控开关元件s1和第一二极管元件d1均可以分别通过至少一个电连接部13电耦合到第二半导体衬底10b的第一金属化层111的第一区段1111。第二半导体衬底10b的第一金属化层111的第一区段1111可以形成或可以耦合到输出端。根据图4的示例性半桥装置,例如,可以在输出端处提供ac电压。第二可控半导体元件s2和第二二极管元件d2均可以分别通过至少一个电连接部13电耦合到第二半导体衬底10b的第一金属化层111的第二区段1112。第二半导体衬底10b的第一金属化层111的第二区段1112可以形成或可以耦合到第二供应节点,其中第二供应节点耦合到第二电势,所述第二电势是与第一电势相反的电势。

[0037]

由于第一半导体衬底10a的第一金属化层111电耦合到第一半导体衬底的第三金属化层113,因此第三金属化层133也耦合到第一电势。第二半导体衬底10b的第三金属化层113电耦合到第二半导体衬底10b的第一金属化层111的第二区段1112,并因此耦合到第二电势。换言之,根据一个示例,在一对半导体衬底10a、10b中,第一衬底10a的中间金属化层(第三金属化层)113耦合到与第二半导体衬底10b的中间金属化层(第三金属化层)113所耦合到的电势相反的电势。换言之,如果第一半导体衬底10a的中间金属化层113耦合到正电势,则同一对半导体衬底10a、10b中的第二衬底10b的中间金属化层耦合到负电势,并且反之亦然。可以以相同的方式来构建与第一对布置在同一封装17内的其他对半导体衬底10a、10b。

[0038]

根据一个示例,第一半导体衬底10a的大小(尺寸)可以等于同一对半导体衬底10a、10b的第二半导体衬底10b的大小(尺寸)。换言之,第一半导体衬底10a的电介质绝缘层11a、11b在第一水平方向x上的长度可以等于第二半导体衬底10b的对应的电介质绝缘层11a、11b在同一方向上的长度。这同样适用于电介质绝缘层11a、11b在第二水平方向z上的宽度。此外,第一半导体衬底10a的第三金属化层113(中间金属化层)的尺寸可以等于同一对半导体衬底10a、10b的第二半导体衬底10b的第三金属化层113(中间金属化层)的尺寸。换言之,第一半导体衬底10a的第三金属化层113在第一水平方向x上的长度可以等于第二半导体衬底10b的对应的第三金属化层113在同一方向上的长度。这同样适用于第三金属化层113在第二水平方向z上的宽度。水平方向x、z是平行于半导体衬底10a、10b的顶表面的方向,其中半导体衬底10的顶表面是在其上安装或可以安装至少一个半导体主体120的表面。

[0039]

然而,一对半导体衬底的第一半导体衬底10a和第二半导体衬底10b的电介质绝缘层11a、11b和/或第三金属化层113的尺寸相等仅是示例。根据另一个示例,第一半导体衬底

10a的第三金属化层113的表面积在对应的第二半导体衬底10b的第三金属化层113的表面积的95%至105%之间。换言之,在表面积之间可能存在一定偏差。金属化层的表面积由其在第一水平方向x上的长度和其在第二水平方向z上的宽度确定。这同样适用于电介质绝缘层11a、11b。根据一个示例,第一半导体衬底10a的第一电介质绝缘层11a的表面积在对应的第二半导体衬底10b的第一电介质绝缘层11a的表面积的95%至105%之间。根据一个示例,第一半导体衬底10a的第二电介质绝缘层11b的表面积在对应的第二半导体衬底10b的第二电介质绝缘层11b的表面积的95%至105%之间。

[0040]

在图5所示的装置中,半导体装置的第一开关s1以及可选的第一二极管元件d1布置在第一半导体衬底10a上,并且半导体装置的第二开关s2以及可选的第二二极管元件d2布置在半导体衬底10b上,第一和第二半导体衬底10a、10b形成一对半导体衬底。然而,这仅是示例。

[0041]

现在参考图6,还有可能在衬底10上布置多于一个开关、以及可选地多于一个二极管元件。在图6所示的示例中,第一半导体衬底10a包括结构化的第一金属化层111。在图6的示例中,第一半导体衬底10a的第一金属化层111包括三个不同的区段1111、1112、1113。然而,第一半导体衬底10a的第一金属化层111一般也有可能包括多于三个区段。第一可控半导体元件s1和第一二极管元件d1安装并且电耦合到第一金属化层111的第一区段1111。第二可控半导体元件s2和第二二极管元件d2安装到第一金属化层111的第二区段1112。第一区段1111电耦合到第一电势。第一电势例如可以是正电势dc+。第一可控半导体元件s1和第一二极管元件d1通过至少一个电连接部13电耦合到第二区段1112。第二区段1112可以形成或可以耦合到半导体装置的输出端。第一可控半导体元件s1和第二可控半导体元件s2例如可以形成半桥装置。因此,例如可以在半导体装置的输出端处提供ac电压。第二可控半导体元件s2和第二二极管元件d2可以通过至少一个电连接部13电耦合到第三区段1113。第三区段1113可以电耦合到与第一电势相反的第二电势。换言之,如果第一电势是正电势dc+,则第二电势是负电势dc-,并且反之亦然。

[0042]

第一区段1111例如可以通过过孔115电耦合到第一半导体衬底10a的中间金属化层(第三金属化层)113。换言之,第一半导体衬底10a的中间金属化层113电耦合到第一电势dc+。

[0043]

第一半导体衬底10a和第二半导体衬底10b形成一对衬底。与第一半导体衬底10a相比,图6中所示的第二半导体衬底10b一般具有类似的结构。然而,代替第一区段1111,第一金属化层111的第二区段1112通过过孔115电耦合到中间金属化层(第三金属化层)113。换言之,第二半导体衬底10b的中间金属化层113电耦合到第二电势dc-。类似于图5中所示的装置,在图6的装置中,一对半导体衬底10a、10b中的一个半导体衬底包括耦合到第一电势的中间金属化层113,而该对半导体衬底10a、10b中的另一个半导体衬底包括耦合到与第一电势相反的第二电势的中间金属化层113。

[0044]

在图6所示的示例中,示意性地示出了一对半导体衬底10a、10b。然而,也有可能在基板12上、或者一般来说在同一壳体17内部布置多于一对半导体衬底10a、10b。

[0045]

在图6的示例中,第一半导体衬底10a与第二半导体衬底10b有所不同。特别地,过孔115被布置在相应的衬底上的不同位置,并且均被配置为将第一金属化层111的区段中的不同的区段电耦合到中间金属化层113(第一半导体衬底10a:第一区段1111和中间金属化

层113之间的过孔115;第二半导体衬底10b:第三区段1113和中间金属化层113之间的过孔115)。然而,这仅是示例。

[0046]

根据另一个示例,如图7a和图7b所示例性示出的,第一半导体衬底10a(图7a)的通用结构可以与第二半导体衬底10b(图7b)的通用结构等同。换言之,第一半导体衬底10a可以包括与第二半导体衬底10b相同数量的金属化层111、112、113,以及相同数量的电介质绝缘层11a、11b。此外,第一半导体衬底10a的第一金属化层111可以包括与第二半导体衬底10b的第一金属化层111相同数量的区段。在图7的示例中,第一半导体衬底10a和第二半导体衬底10b均包括具有五个不同区段的第一金属化层111。

[0047]

通用结构类似于上面相对于图6已经描述的结构。第一可控半导体元件s1和(可选的)第一二极管元件d1被安装并且电耦合到第一金属化层111的第一区段1111。第二可控半导体元件s2和(可选的)第二二极管元件d2被安装到第一金属化层111的第二区段1112。第一区段1111电耦合到第一电势。例如,第一电势可以是正电势dc+。第一可控半导体元件s1和可选的第一二极管元件d1通过至少一个电连接部13电耦合到第二区段1112。第二区段1112可以形成或可以耦合到半导体装置的输出端。第一可控半导体元件s1和第二可控半导体元件s2例如可以形成半桥。因此,可以在半桥装置的输出端处提供ac电压。第二可控半导体元件s2和可选的第二二极管元件d2可以通过至少一个电连接部13电耦合到第三区段1113。第三区段1113可以电耦合到与第一电势相反的第二电势。换言之,如果第一电势是正电势dc+,则第二电势是负电势dc-,并且反之亦然。

[0048]

第一金属化层111的第四部分1114和第五部分1115均通过过孔115电耦合到中间金属化层(第三金属化层)113。然而,第四部分1114和第五部分1115中仅一个被电接触。在第一半导体衬底10a上,在第一区段1111和第四区段1114之间提供至少一个电连接部13。然而,在第五区段1115和第一金属化层111的任何其他区段之间不提供电连接部。这样,中间金属化层113通过过孔115、第四区段1114、至少一个电连接部13和第一区段1111电耦合到第一电势dc+。

[0049]

第二半导体衬底10b与第一半导体衬底10a的不同之处仅在于,第五区段1115被电接触而不是第四区段1114被电接触。换言之,第二半导体衬底10b的中间金属化层113通过过孔115、第五区段1115、第五区段1115和第三区段1113之间的至少一个电连接部13、以及第三区段1113电耦合到第二电势dc-。图7a和图7b中所示的半导体衬底10a、10b的结构允许制造等同的衬底,而与它们以后用作一对半导体衬底10a、10b中的第一半导体衬底还是第二半导体衬底无关。中间金属化层(第三金属化层)113的电势可以通过在第四区段1114与第一区段1111之间或者在第五区段1115与第三区段1113之间提供对应的电连接部13来确定。

[0050]

在图7c中示出了允许第一半导体衬底10a的通用结构与第二半导体衬底10b的通用结构等同的另一个示例性装置。图7c所示的衬底10ab一般类似于以上相对于图7a和图7b已经描述的衬底。然而,代替提供两个单独的第四和第五区段1114、1115,可以仅提供第四区段1114。第四区段1114通过过孔115电耦合到中间金属化层113。该第四区段1114可以被布置为与第一区段1111和第三区段1113这两者相邻。在图7c所示的示例中,第一区段1111和第三区段1113都通过至少一个电连接部13a、13b电耦合到第四区段1114。然而,这仅出于说明的目的。如果将图7c的衬底10ab用作一对衬底中的第一衬底10a,则仅第一区段1111将通过至少一个电连接部13a电耦合到第四部分1114。如果将图7c的衬底10ab用作一对衬底中的第

二衬底10b,则仅第三区段1113将通过至少一个电连接部13b电耦合到第四部分1114。换言之,取决于区段1111、1113中的哪个区段电耦合到第四区段1114,半导体衬底10的中间金属化层113电耦合到第一电势dc+或第二电势dc-。

[0051]

在上面通过图3至图7所描述的示例中,第一金属化层111的区段可以例如通过端子元件14从壳体17的外部被电连接,如以上相对于图1已经描述的。例如,第一端子元件14可以电耦合到第一金属化层111的区段,以便将该区段电耦合到第一电势dc+。另一个端子元件14可以电耦合到第一金属化层的另一个区段,以便将该区段耦合到第二电势dc-。另一个端子元件14可以电耦合到第一金属化层111的另一区段,以便向壳体17的外部提供输出电压或输出电流。取决于区段的数量,一个半导体衬底10可以通过一个或多于一个端子元件14被电连接。

[0052]

在整个说明书和附图中,仅示出并特别提及了与理解不同的实施例相关的第一金属化层111的这样的区段111

n

。然而,第一金属化层111一般可以包括比上述不同区段更多的区段。例如,可能需要附加的区段以便提供允许电接触半导体主体的任何栅极、辅助发射极或辅助源极端子的控制轨和导体轨。还有可能的是,在半导体模块装置内需要上述电势之外的附加的电势。因此,可能需要附加的区段以便提供这样的附加的电势。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1