一种基于大尺寸像素的电荷快速转移方法与流程

[0001]

本发明涉及cmos图像传感器技术领域,特别是涉及一种基于大尺寸像素的电荷快速转移方法。

背景技术:

[0002]

cmos图像传感器凭借着高集成度、低功耗、高分辨率、大动态范围、高灵敏度等优点逐渐变为成像领域重点研究对象,在多种应用场景如静态拍摄、动态图像捕捉、指纹识别等都会广泛涉及大尺寸像素的设计和使用。大尺寸像素单元先天存在的缺点是由于感光区面积较大其边缘的光生电子距传输栅较远,因此附近的光生电子只能凭借扩散作用和沟道电势梯度形成的电场力运输到远距离的传输栅下,这种光生电子运输模式很容易造成电荷的不完全转移最终产生图像拖尾,此外如果传输栅开启的时间很短,那么图像拖尾情况将会更严重。

[0003]

除由光电转化区距传输栅较远引起的电荷转移速率过慢因素外,在cmos 图像传感器芯片制造步骤中的缺陷也会导致电荷转移速率的下降。衬底材料硅的晶格的缺陷和离子污染会在光电荷转移路径上引入势垒或势阱,退火过程中的表面p型钳位层向传输栅下的离子扩散也会引起电荷传输路径上的势垒出现,这些势垒或势阱会阻碍电子从光电二极管流向电荷电压转化节点(fd)导致其转移速率下降。

技术实现要素:

[0004]

本发明的目的是针对上述的现有技术的缺陷,而提供一种基于大尺寸像素的电荷快速转移方法,最终实现大尺寸像素电荷的快速转移,解决大尺寸像素电荷转移速率慢而引起图像拖尾的技术问题。

[0005]

为实现本发明的目的所采用的技术方案是:

[0006]

一种基于大尺寸像素的电荷快速转移方法,包括步骤:

[0007]

在像素的光电转化区,使pdn的顶端部分露出于pdp外,使在pdn与pdp 交界处形成多个pn结;

[0008]

在所述光电转化区与fd节点之间设置第一传输栅tx1与第二传输栅tx2,第一传输栅tx1与第二传输栅tx2之间形成n区,该n区注入n型施主杂质以降低开启阈值;

[0009]

电荷转移阶段,控制第一传输栅tx1与第二传输栅tx2同时开启,储存在 pdn的电子在pn结内建电场力、扩散作用力、pdn与fd节点的电势差形成的电场力三者共同作用下,从pdn出发经过传输管最终运输到fd节点中;

[0010]

第一第一传输栅tx1负责调整由像素制造过程中引入的势垒或势阱;第二传输栅tx2施加适当高电压让其栅下反型层面积增大,保证电荷转移进行。

[0011]

其中,所述第一传输栅tx1覆盖的电荷转移沟道表现为势阱时,那么在第一传输栅tx1上施加稍低的开启电压以填平势阱,若沟道表现为势垒,则在第一传输栅tx1上施加稍高的电压以降低势垒。

[0012]

其中,所述pdn的轴截面呈等腰三角形状(pdn呈圆锥体),顶点露出于所述pdp外,形成所述pn结。

[0013]

优选的,所述pdn的轴截面呈等腰梯形状(pdn呈圆锥台结构),上端露出于所述pdp外,形成所述pn结。本发明提出的多边形光电转化区结合双传输栅的新结构和相应的操作方法,利用所设计的多边形光电转化区和带有电势调整的的双传输栅的新型像素结构,实现大尺寸像素电荷的快速转移。

附图说明

[0014]

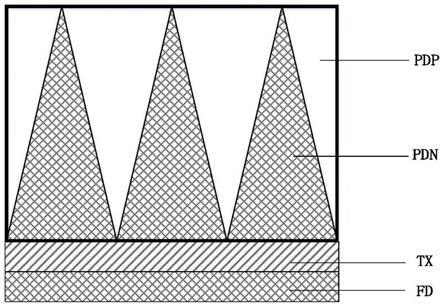

图1是本发明提供的像素结构的光电转化区的示意图;

[0015]

图2是本发明提供的像素结构原理示意图;

[0016]

图3是梯形pdn像素有源区俯视图。

具体实施方式

[0017]

以下结合附图和具体实施例对本发明作进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

[0018]

本发明利用光电转化区内部形成的pn结内建电场使得电荷转移速率增加,此外由两个传输栅的电压配合消除的电荷转移路径上的势垒势阱会进一步加快电荷转移速率。

[0019]

在常规大尺寸像素设计规则的基础上,设计出形状如图1所示的光电转化区。在施主型掺杂区(pdn)全耗尽的条件下,可以认为pdn就是进行光电转化的区域,由光电转化生成的光电子储存在pdn中。从图中可以看出pdn并不是被表面受主型杂质(pdp)完全覆盖,所以在pdn与pdp交界处会存在多个小pn 结,根据pn结空间电荷区的内建电势可知:曝光结束后的电荷转移阶段,pdn 储存的光生电子会在pn结内建电场力的作用下漂移到电荷转移沟道,这部分增加的电场力因此增加了电荷转移的速率。

[0020]

具体的,pn结空间电荷区内建电势如公式1所示,其中v

bi

表示pn结的内建电势差,k为玻尔兹曼常量,t表示温度,q为电子电荷量,n

a

表示受主杂质浓度,n

d

表示施主杂质浓度,n

i

表示衬底硅的本征浓度。由pdp层退火过程延伸到传输栅下表面而引起的势垒问题,可以利用带有势垒修正的双传输栅结构解决,具体的像素结构如图2所示。

[0021]

图2中tx1为第一传输栅,负责电荷转移沟道电势的调整,tx2为第二传输栅保证电荷转移沟道的正常开启。对于第一传输栅tx1与第二传输栅tx2之间的部分没有栅上电压的直接覆盖导致沟道开启不完全的问题,可以注入一定剂量的n型施主杂质从而降低这部分的开启阈值,保证电荷转移没有阻碍,这个区域对应图2中的n区。因为pdn的新形貌设计牺牲了部分感光面积,所以像素的满阱容量也有所降低,本发明利用双栅结构的高灵活性可以巧妙地解决这一问题,即在像素曝光对tx1施加负压来增加像素的满阱容量。

[0022][0023]

本发明利用标准的cmos像素制造工艺完成,但与常规过程不同的是本发明需要制作特殊形状的pdn和双传输栅极结构。图1所示的pdn形貌设计适用于理想情况,受工艺水平的限制,实际设计中可以对图1中pdn尖角部分做适量的调整,例如梯形的pdn,具体如图3所

示。像素制造工艺与普通的cmos制造工艺不同的是前者允许特殊形状的存在,但设计图案出现尖角会增加制造难度并降低良品率,所以在不同工艺节点和工艺水平条件下需要对本发明pdn形貌设计做适当调整。

[0024]

其中,双传输栅(传输栅tx1与传输栅tx2)的制作不需要增加光刻板的数量,只需调整在栅极形成过程中光刻胶的位置,双传输栅(传输栅tx1与传输栅tx2)之间沟道的n型调整层注入需要增加一块额外的光刻板,其余步骤就可以按照标准的像素制造工艺进行。

[0025]

像素制造完成后,需要设定像素工作过程,本发明像素的操作时序与标准的四管有源像素相比电荷转移阶有所不同,除此阶段外的操作时序可沿用传统时序。

[0026]

其中,电荷转移阶段,第一传输栅tx1与第二传输栅tx2同时开启,储存在pdn的电子在pn结内建电场力、扩散作用力、pdn与fd节点的电势差形成的电场力三者共同作用下,从pdn出发经过传输管最终运输到fd节点中。传输栅 tx1负责调整由像素制造过程中引入的势垒或势阱。传输栅tx1覆盖的电荷转移沟道表现为势阱时,那么在传输栅tx1上施加稍低的开启电压以填平势阱,若沟道表现为势垒,则在传输栅tx1上施加稍高的电压以降低势垒。传输栅tx2 施加适当的高电压让其栅下反型层面积增大,保证电荷转移的正常进行。

[0027]

以上所述仅是本发明的优选实施方式,应当指出的是,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1