半导体结构及其形成方法与流程

1.本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

2.随着半导体制造技术越来越精密,集成电路也发生着重大的变革,集成在同一芯片上的元器件数量已从最初的几十、几百个增加到现在的数以百万个。为了达到电路密度的要求,半导体集成电路芯片的制作工艺利用批量处理技术,在衬底上形成各种类型的复杂器件,并将其利用互连结构互相连接以使其具有完整的电子功能,目前大多采用在导线之间以超低k层间介电层作为隔离各金属内连线的介电材料,互连结构用于提供在ic芯片上的器件和整个封装之间的布线。在该技术中,在半导体衬底表面首先形成例如场效应晶体管(fet)的器件,然后在集成电路制造后段制程(back end of line,beol)中形成互连结构。

3.正如摩尔定律所预测的,半导体衬底尺寸的不断缩小,以及为了提高器件的性能在半导体衬底上形成了更多的晶体管,采用互连结构来连接晶体管是必然的选择。然而随着元器件的微型化和集成度的增加,电路中导体连线数目不断的增多,互连结构的形成质量对后端(back end of line,beol)电路的性能影响很大,严重时会影响半导体器件的正常工作。

4.因此,如何在后端工艺中形成更小尺寸的互连结构,成为本领域技术人员亟需解决的技术问题。

技术实现要素:

5.本发明实施例解决的问题是提供一种半导体结构的形成方法,提升半导体结构的电学性能。

6.为解决上述问题,本发明实施例提供一种半导体结构的形成方法,包括:

7.提供基底,所述基底包括金属互连层;

8.在所述基底上形成图形记忆层,所述图形记忆层开设有第一沟槽,第二沟槽以及第三沟槽,所述第一沟槽的延伸方向、所述第二沟槽的延伸方向和第三沟槽的延伸方向相互平行,且所述第一沟槽,所述第二沟槽以及所述第三沟槽采用不同的光罩形成;

9.形成核心材料层,所述核心材料层填充所述第一沟槽,所述第二沟槽和所述第三沟槽;

10.图形化所述核心材料层,形成核心层,所述核心层开设有隔离开口;

11.填充所述隔离开口形成隔离层,所述隔离层的顶部至少与所述核心层的顶部齐平;

12.去除所述核心层,形成第四沟槽,所述第四沟槽对应所述金属互连层。

13.相应的,本发明实施例提供一种半导体结构,包括:

14.基底,所述基底包括金属互连层;

15.图形记忆层和隔离层,均设置于所述基底上,且所述隔离层的顶部与所述图形记忆层的顶部齐平,所述图形记忆层和所述隔离层围成第四沟槽,所述第四沟槽对应所述金属互连层,各所述第四沟槽的延伸方向相同。

16.与现有技术相比,本发明实施例的技术方案具有以下优点:

17.本发明实施例提供的所述半导体结构的形成方法中,首先在基底上形成图形记忆层,之后采用不同的光罩在图形记忆层分别形成第一沟槽,第二沟槽以及第三沟槽,所述第一沟槽的延伸方向平行于所述第二沟槽和第三沟槽的延伸方向;接着向所述第一沟槽,所述第二沟槽以及第三沟槽内填充核心材料层;之后图形化所述核心材料层,形成开设有隔离开口的核心层;接着填充所述隔离开口形成隔离层;最后去除所述核心层,形成第四沟槽,所述第四沟槽对应基底内的金属互连层。可见,本发明实施例所提供的半导体结构的形成方法,通过采用多道光刻工艺利用不同的光罩在图形记忆层上形成第一沟槽,第二沟槽以及第三沟槽,之后再采用隔离层同时将第一沟槽,第二沟槽以及第三沟槽的沟槽形状进行调整,可以形成满足尺寸要求的第四沟槽,从而,后续再以第四沟槽周围的图形记忆层和隔离层组成的介质为掩膜向下刻蚀时,可以在基底上形成与第四沟槽形貌一致的沟槽,因所述第四沟槽对应基底内的金属互连层,即在基底上形成的沟槽能够露出金属互连层,这样,通过后续在基底的沟槽内形成能够与金属互连层接触的金属层,就可以实现金属层与金属互连层电连接。本发明实施例所提供的半导体结构的形成方法,由于多道第一沟槽,第二沟槽以及第三沟槽的图形状态的调整可以在同一工艺步骤完成,因此简化了工艺流程;另一方面,通过3道光罩来形成多道第一沟槽,第二沟槽以及第三沟槽,以及通过在第一沟槽,第二沟槽以及第三沟槽内形成隔离层的方式实现对沟槽形状的调整,可以在即使图形尺寸接近设备参数极限的情况下,也能够实现后端加工工艺中对更小尺寸的图形的加工,保证加工质量的同时降低生产成本。

附图说明

18.图1至图23是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图。

具体实施方式

19.随着元器件的微型化和集成度的增加,电路中导体连线数目不断的增多,这就要求金属互连线的图形尺寸越来越小,图形尺寸越来越接近光刻设备极限,如何在后端工艺中形成更小尺寸的互连结构,成为亟需解决的技术问题。

20.为了解决所述技术问题,本发明实施例提供一种半导体结构的形成方法,提供基底,所述基底包括金属互连层;在所述基底上形成图形记忆层,所述图形记忆层开设有第一沟槽,第二沟槽以及第三沟槽,所述第一沟槽的延伸方向平行于所述第二沟槽和第三沟槽的延伸方向,所述第一沟槽,第二沟槽以及第三沟槽采用不同的光罩形成;形成核心材料层,所述核心材料层填充所述第一沟槽,所述第二沟槽以及所述第三沟槽;图形化所述核心材料层,形成核心层,所述核心层开设有隔离开口;填充所述隔离开口形成隔离层,所述隔离层的顶部至少与所述核心层的顶部齐平;去除所述核心层,形成第四沟槽,所述第四沟槽对应所述金属互连层。

21.本发明实施例提供的所述半导体结构的形成方法中,通过采用多道光刻工艺利用不同的光罩在图形记忆层上形成第一沟槽,第二沟槽以及第三沟槽,之后再采用隔离层同时将第一沟槽,第二沟槽以及第三沟槽的沟槽形状进行调整,可以形成满足尺寸要求的第四沟槽,从而,后续再以第四沟槽周围的图形记忆层和隔离层组成的介质为掩膜向下刻蚀时,可以在基底上形成与第四沟槽形貌一致的沟槽,因所述第四沟槽对应基底内的金属互连层,即在基底上形成的沟槽能够露出金属互连层,这样,通过后续在基底的沟槽内形成能够与金属互连层接触的金属层,就可以实现金属层与金属互连层电连接。本发明实施例所提供的半导体结构的形成方法,由于多道第一沟槽,第二沟槽以及第三沟槽的图形状态的调整可以在同一工艺步骤完成,因此简化了工艺流程;另一方面,通过3道光罩(mask)来形成多道第一沟槽,第二沟槽以及第三沟槽,以及通过在第一沟槽,第二沟槽以及第三沟槽内形成隔离层的方式实现对沟槽形状的调整,可以在即使图形尺寸接近设备参数极限的情况下,也能够实现后端加工工艺中对更小尺寸的图形的加工,保证加工质量的同时降低生产成本。

22.为使本发明实施例的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

23.图1至图23是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图。

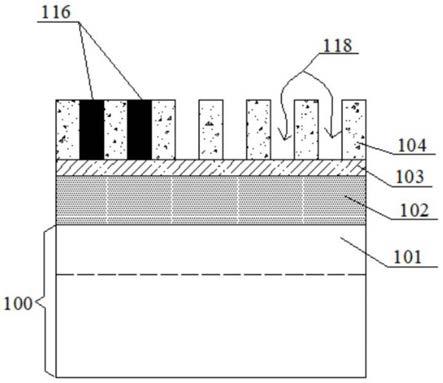

24.请参考图1和图2,图1是一种半导体结构的俯视图,图2是图1沿aa’方向切割得到的剖视图。

25.如图所示,提供基底100,所述基底100包括金属互连层(图中未示出);

26.所述基底100用于为工艺制程提供工艺平台。基底100中可以形成有晶体管、电容器等半导体器件,基底中还可以形成有电阻结构、导电结构等功能结构。

27.所述基底100包括金属互连层,后续在所述基底100形成金属层后,金属互连层用于实现后段(back end of line,beol)制程中与金属层电连接,从而使半导体器件(例如晶体管)或者功能结构与外部电路或其他互连结构电连接。

28.所述基底还包括介质层101,所述介质层101覆盖所述金属互连层。所述介质层101用于实现后段(back end of line,beol)制程中金属层的相邻互连线之间的电隔离。

29.继续结合图1参考图2,在所述基底上形成图形记忆层104,所述图形记忆层104开设有第一沟槽107,第二沟槽110以及第三沟槽113,所述第一沟槽107的延伸方向、所述第二沟槽的延伸方向和第三沟槽113的延伸方向相互平行,所述第一沟槽107,第二沟槽110以及第三沟槽113采用不同的光罩形成。

30.容易理解的是,随着半导体器件集成度增加,电路中金属连线数目也不断增多,导致金属连线的图形线宽越来越小,受工艺限制,多个图形无法采用一张光罩形成,为了保证图形质量,避免多个相邻的图形同时曝光后相连接,所述第一沟槽107,第二沟槽110以及第三沟槽113采用不同的光罩形成,即3道沟槽通过3次光刻和刻蚀工艺形成。本实施例中,第一次光刻和刻蚀工艺形成第一沟槽107;第二次光刻和刻蚀工艺形成第二沟槽110;第三次光刻和刻蚀工艺形成第三沟槽113。

31.图形记忆层104用于为3张光罩提供支撑平台,使得3张光罩的图形最终分别转移到的图形记忆层上。

32.本实施例中,所述图形记忆层104的材料为氧化硅,在其他实施例中,所述图形记忆层的材料可以为氧化硅,氮化硅,氮氧化硅中的一者或者至少两者的组合。

33.具体地,请结合图2参考图3-图7,形成所述图形记忆层104的步骤包括:

34.首先形成第一沟槽107。

35.具体地,如图3和图4所示,在所述基底100上形成图形记忆材料层104a;

36.在所述图形记忆材料层104a上形成图形化的第一光刻胶层106;

37.以所述第一光刻胶层106为掩膜刻蚀所述图形记忆材料层104a,形成第一沟槽107;

38.本实施例中,以所述第一光刻胶层106为掩膜刻蚀第一抗反射材料层105,形成第一反射层(图中未示出),接着以所述第一光刻胶和所述第一反射层为掩膜刻蚀所述图形记忆材料层104a,形成第一沟槽107。

39.接着,形成第二沟槽110。

40.如图5和图6所示,在所述图形记忆材料层上形成图形化的第二光刻胶层109;

41.以所述第二光刻胶层109为掩膜刻蚀所述图形记忆材料层,形成第二沟槽110;

42.本实施例中,在形成第二光刻胶层之前,先形成填充第一沟槽107且覆盖图形记忆材料层的第二抗反射材料层,以所述第二光刻胶层109为掩膜刻蚀第二抗反射材料层108,形成第二反射层(图中未示出),接着以所述第二光刻胶层109和所述第二反射层为掩膜刻蚀所述图形记忆材料层104a,形成第二沟槽110。

43.之后,再形成第三沟槽113。

44.如图2和图7所示,在所述图形记忆材料层104上形成图形化的第三光刻胶层112;

45.以所述第三光刻胶层112为掩膜刻蚀所述图形记忆材料层,形成第三沟槽113。

46.本实施例中,在形成第三光刻胶层112之前,先形成填充第一沟槽107和第二沟槽110且覆盖图形记忆材料层的第三抗反射材料层111,以所述第三光刻胶层112为掩膜刻蚀第三抗反射材料层111,形成第三反射层(图中未示出),接着以所述第三光刻胶层112和所述第三反射层为掩膜刻蚀所述图形记忆材料层104a,形成第三沟槽113。

47.第一沟槽107,第二沟槽110以及第三沟槽113为后续形成核心材料层提供空间。

48.参考图8-图13,其中,图9和图11是本发明实施例的半导体结构的俯视示意图;图10是沿图9的aa’方向的剖视图;图13是沿图11的bb’方向的剖视图。

49.形成核心材料层114a,所述核心材料层114a分别填充所述第一沟槽,所述第二沟槽以及第三沟槽;

50.如图8所示,本实施例中,采用沉积工艺形成填充所述第一沟槽和所述第二沟槽的核心材料层,为了保证核心材料层完全填充第一沟槽,第二沟槽以及第三沟槽,以更好地形成核心材料层的形貌,所述核心材料层114a还覆盖所述图形记忆层104。接着,平坦化所述核心材料层114a,直至露出所述图形记忆层,当然,在其他实施例中,核心材料层也可以仅填充第一沟槽,第二沟槽以及第三沟槽。

51.接着,参考图11-图13,图形化所述核心材料层114a,形成隔离开口115,形成核心层114。

52.容易理解的是,以第一沟槽为例,在实际工艺过程中,受工艺限制,在沿第一沟槽延伸方向上,如果相邻的2个第一沟槽之间的距离太小,则无法通过光刻直接形成2个第一

沟槽,因此,为了形成更小尺寸的第一沟槽,首先形成一个完整的沟槽,接着对完整沟槽进行切断。因此,本发明实施例中,在形成第一沟槽,第二沟槽和第三沟槽后,还需要对3道沟槽进行核心材料层填充(图9)和图形化(图11),以形成满足工艺要求的图形。

53.所述核心层114用于为后续形成第四沟槽提供空间。

54.本实施例中,所述核心层114的材料为多晶硅。在其他实施例中,所述核心层的材料还可以为无定形碳、光刻胶、有机介质层材料、介电抗反射涂层材料、中的一种或者至少两种的组合。

55.需要说明的是,在核心层114的延伸方向上,通过隔离开口115(示于图11中)将连续延伸的核心材料层截断,使得完整的核心材料层114a分散为数个长短不一的核心层,从而在核心层延伸方向上,缩小核心层的尺寸,以满足工艺尺寸要求。

56.本实施例中,形成的所述隔离开口115在一个工艺步骤中同时切断填充于第一沟槽,第二沟槽以及第三沟槽中的核心材料层,从而简化了加工工艺。

57.具体地,如图12和图13所示,图形化所述核心材料层114a,形成所述核心层114的步骤包括:

58.在所述核心材料层114a上形成遮挡层117,所述遮挡层117露出部分所述核心材料层114a;

59.以所述遮挡层117为掩膜刻蚀所述核心材料层114a,形成隔离开口115(示于图11),以剩余的核心材料层作为核心层114。

60.需要说明的是,所述遮挡层露出部分所述核心材料层,指的是所述遮挡层露出图11中的用于形成隔离开口115的位置处的核心材料层,所述遮挡层用于遮挡不需要被刻蚀的核心材料层区域,从而以遮挡层为掩膜向下刻蚀时,保证形成的隔离开口115能够满足形貌要求。

61.接着,如图14-图16所示,填充所述隔离开口形成隔离层116,所述隔离层116的顶部至少与所述核心层的顶部齐平;其中,图16是俯视图;图15是图16沿bb’方向的剖视图。

62.所述隔离层116用于填充隔离开口,在沿核心层114延伸方向上,所述隔离层116分别与相邻的核心层114接触,以保证后续去除核心层形成第四沟槽后,隔离层能够切断第四沟槽,从而形成的第四沟槽能够满足形貌要求,后续以第四沟槽周围的侧壁为掩膜向下刻蚀时,保证最终形成的图形满足尺寸形貌要求。

63.所述隔离层116的材料与所述核心层的材料不同,以保证隔离层的材料与核心层的材料具有不同的刻蚀速率。

64.需要说明的是,所述隔离层至少与所述核心层的顶部齐平,指的是所述隔离层的顶面可以与核心层的顶面齐平,或者所述隔离层的顶面高于所述核心层的顶面。

65.具体地,如图14和图15所示,本实施例中,所述隔离层116的形成步骤包括:

66.形成隔离材料层116a,所述隔离材料层116a填充所述隔离开口且覆盖所述核心层114和所述图形记忆层104;

67.平坦化所述隔离材料层116a,形成隔离层116,所述隔离层116的顶面与所述核心层114的顶面齐平。

68.平坦化所述隔离材料层116a,形成隔离层116时,以所述核心层作为刻蚀停止层。

69.结合图16参考图17和图18,其中,图17是沿图16中bb’方向的剖视图,图18是沿图

16的aa’方向的剖视图。

70.去除所述核心层114(示于图10中),形成第四沟槽118,所述第四沟槽114对应所述金属互连层(图中未示出)。

71.需要说明的是,所述第四沟槽对应所述金属互连层,指的是后续以第四沟槽周围的侧壁为掩膜向下刻蚀基底时,能够露出基底内的金属互连层。

72.所述去除所述核心层的工艺可以为干法刻蚀工艺,也可以是湿法刻蚀工艺,只要能够保证核心层完全去除即可。

73.可见,本发明实施例所提供的半导体结构的形成方法,通过采用多道光刻工艺利用不同的光罩在图形记忆层上形成第一沟槽,第二沟槽以及第三沟槽,之后再采用隔离层同时将第一沟槽,第二沟槽以及第三沟槽的沟槽形状进行调整,可以形成满足尺寸要求的第四沟槽,从而,后续再以第四沟槽周围的图形记忆层和隔离层组成的介质为掩膜向下刻蚀时,可以在基底上形成与第四沟槽形貌一致的沟槽,因所述第四沟槽对应基底内的金属互连层,即在基底上形成的沟槽能够露出金属互连层,这样,通过后续在基底的沟槽内形成能够与金属互连层接触的金属层,就可以实现金属层与金属互连层电连接。本发明实施例所提供的半导体结构的形成方法,由于多道第一沟槽,第二沟槽以及第三沟槽的图形状态的调整可以在同一工艺步骤完成,因此简化了工艺流程;另一方面,通过3道光罩来形成多道第一沟槽,第二沟槽以及第三沟槽,以及通过在第一沟槽,第二沟槽以及第三沟槽内形成隔离层的方式实现对沟槽形状的调整,可以在即使图形尺寸接近设备参数极限的情况下,也能够实现后端加工工艺中对更小尺寸的图形的加工,保证加工质量的同时降低生产成本。

74.如图18-图21所示,去除所述核心层,形成第四沟槽118之后,还包括:

75.以所述图形记忆层104和所述隔离层116为掩膜,刻蚀所述第四沟槽118露出的所述基底的介电层101,形成第五沟槽(示于图21),所述第五沟槽用于形成金属层,所述第五沟槽对应下方的所述金属互连层。

76.需要说明的是,所述第五沟槽对应所述金属互连层,指的是第五沟槽能够露出基底内的金属互连层,后续在第五沟槽内形成金属层后,金属层能够与所述金属互连层电连接。

77.当然,为了提高将图形转移到基底上的准确性,避免以第四沟槽周围的侧壁(图形记忆层和隔离层)为掩膜时掩膜被过早消耗造成图形精度下降,本发明实施例所提供的半导体结构的形成方法,在形成图形记忆层104之前,还包括:在所述基底上形成掩膜层102(示于图18中);当存在掩膜层102时,图形记忆层形成于掩膜层上。

78.掩膜层102用于在后续工艺步骤中,对介电层101的顶面起到保护的作用;在后续形成第五沟槽的过程中,图形化后的掩膜层102还用于作为刻蚀第五沟槽的刻蚀掩膜。

79.结合图18参考图19和图20,所述形成第五沟槽120的步骤包括:

80.以所述图形记忆层104和所述隔离层116(示于图17中)为掩膜,刻蚀所述第四沟槽118露出的所述掩膜层102,形成第六沟槽119;

81.以所述掩膜层102为掩膜刻蚀所述第六沟槽119露出的所述基底100的介电层101,形成第五沟槽120。

82.本实施例中,形成第五沟槽的步骤中,所述图形记忆层和隔离层均被消耗,所述掩

膜层可以剩余,在其他实施例中,形成所述第五沟槽后,所述掩膜层也可以被消耗。

83.如图20和图21所示,形成第五沟槽120后,若存在掩膜层102,还包括去除剩余的掩膜层102。

84.本实施例中,所述掩膜层102的材料为氮化钛。在其他实施例中,所述掩膜层的材料可以为氮化钽、氧化钛、氧化钽、钨碳复合材料中的一种或至少两种的组合。

85.容易理解的是,为了提高形成于所述掩膜层上的核心材料层的牢固性,形成所述掩膜层之后,形成图形记忆层之前,还包括:

86.在所述基底上形成粘合层103,所述粘合层103覆盖所述掩膜层102。当存在粘合层时,图形记忆层形成于粘合层上。

87.本实施例中,所述粘合层103的材料为氧化铝。在其他实施例中,所述粘合层的材料还可以为氧化硅。

88.当存在粘合层时,以所述图形记忆层104和所述隔离层116(示于图17中)为掩膜,刻蚀所述第四沟槽118露出的所述掩膜层102,形成第六沟槽119时,还同时刻蚀所述掩膜层上方的粘合层。

89.如图22和图23所示,所述形成第五沟槽120(示于图20中)后,还包括:

90.形成金属层121,所述金属层121填充所述第五沟槽,且所述金属层121的顶面与所述介电层101的顶面齐平,所述金属层与所述金属互连层电连接。

91.所述金属层用于实现后段(back end of line,beol)制程中与基底内的金属互连层电连接,从而使半导体器件(例如晶体管)或者功能结构与外部电路或其他互连结构电连接。

92.本实施例中,所述金属层的材料为铜,在其他实施例中,所述金属层的材料还可以是钨、钴或者铝中的一种或者至少两种的组合。

93.具体地,形成所述金属层121的步骤包括:

94.形成金属材料层121a,所述金属材料层121a填充所述第五沟槽且覆盖所述基底;

95.平坦化所述金属材料层121a,形成金属层121,所述金属层121的顶面与所述介电层101的顶面齐平。

96.平坦化所述金属材料层121a,形成金属层121时,以所述介电层作为刻蚀停止层。

97.相应的,结合图16参考图17,本发明实施例还提供一种半导体结构。

98.所述半导体结构包括:基底100,所述基底100包括金属互连层(图中未示出);图形记忆层104和隔离层116,均设置于所述基底100上,且所述隔离层116的顶部与所述图形记忆层104的顶部齐平,所述图形记忆层104和所述隔离层116围成第四沟槽118,所述第四沟槽118对应所述金属互连层,各所述第四沟槽118的延伸方向相同。

99.基底100中可以形成有晶体管、电容器等半导体器件,基底中还可以形成有电阻结构、导电结构等功能结构。

100.所述基底100包括金属互连层,后续在所述基底100形成金属层后,金属互连层用于实现后段(back end of line,beol)制程中与金属层电连接,从而使半导体器件(例如晶体管)或者功能结构与外部电路或其他互连结构电连接。

101.需要说明的是,所述第四沟槽对应所述金属互连层,指的是后续以第四沟槽周围的侧壁为掩膜向下刻蚀基底时,能够露出基底内的金属互连层。后续以第四沟槽周围的介

质层为掩膜向下刻蚀时,可以在基底上形成与第四沟槽形貌一致的沟槽,因所述第四沟槽对应基底内的金属互连层,即在基底上形成的沟槽能够露出金属互连层,从而,后续在基底的沟槽内形成的金属层能够与金属互连层接触,后续通电后,金属层与金属互连层电连接。

102.本实施例中,所述第四沟槽的形成过程首先经过3道光罩分别形成第一沟槽,第二沟槽以及第三沟槽,再在同一工艺步骤完成多道第一沟槽,第二沟槽以及第三沟槽的切断,因此简化了工艺流程;另一方面,通过3道光罩来形成多道第一沟槽,第二沟槽以及第三沟槽,即使在图形尺寸接近设备参数极限的情况下,也能够实现后端加工工艺中对更小尺寸的图形的加工,从而降低生产成本。

103.本实施例中,所述图形记忆层104的材料为氧化硅,在其他实施例中,所述图形记忆层的材料可以为氧化硅,氮化硅,氮氧化硅中的一者或者至少两者的组合。

104.所述隔离层116用于切断第四沟槽,从而形成的第四沟槽能够满足形貌要求,后续以第四沟槽周围的侧壁为掩膜向下刻蚀时,保证最终形成的图形满足尺寸形貌要求。

105.所述基底100、所述图形记忆层104和所述隔离层116之间设置有掩膜层102。

106.需要说明的是,所述掩膜层设置于所述基底、所述图形记忆层和所述隔离层之间,指的是在沿半导体结构生长方向上,所述掩膜层覆盖所述基底,所述图形记忆层和所述隔离层位于同一膜层上,所述图形记忆层和所述隔离层位于所述掩膜层上。

107.本实施例中,所述掩膜层102的材料为氮化钛。在其他实施例中,所述掩膜层的材料可以为氮化钽、氧化钛、氧化钽、钨碳复合材料中的一种或至少两种的组合。

108.所述掩膜层102、所述图形记忆层104和所述隔离层116之间设置有粘合层103。

109.同理,所述粘合层设置于所述掩膜层、所述图形记忆层和所述隔离层之间,指的是在沿半导体结构生长方向上,所述粘合层覆盖所述掩膜层,所述图形记忆层和所述隔离层位于同一膜层上,所述图形记忆层和所述隔离层位于所述粘合层上。

110.本实施例中,所述粘合层103的材料为氧化铝。在其他实施例中,所述粘合层的材料还可以为氧化硅。

111.本实施例所述半导体结构可以采用前述实施例所述的形成方法所形成,也可以采用其他形成方法所形成。对本实施例所述半导体结构的具体描述,可参考前述实施例中的相应描述,本实施例在此不再赘述。

112.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1