半导体工艺设备及其阻抗调节方法与流程

[0001]

本发明实施例涉及半导体加工技术领域,具体地,涉及一种半导体工艺设备及其阻抗调节方法。

背景技术:

[0002]

在诸如物理气相沉积、刻蚀、化学气相沉积以及离子注入等的半导体工艺中,静电卡盘的主要作用是:吸附被加工工件,如晶圆、托盘等,以及在工艺过程中,用于加热或冷却被加工工件。

[0003]

具体地,如图1所示,静电卡盘100包括用于承载晶圆101的介质层104和设置在该介质层104底部的基座109。其中,在介质层104中设置有静电电极(图中未示出),用于产生吸附晶圆101的静电引力;并且,在介质层104中还设置有射频电极107,其通过阻抗匹配器与射频电源电连接,用以在晶圆101上形成射频偏压;阻抗匹配器用于确保输入阻抗等于输出阻抗,以实现最大功率的传输。基座109通过接地结构111接地,以使部分射频能量能够通过地回路返回射频电源。

[0004]

但是,在半导体工艺腔室的制造中,静电卡盘自身差异,线缆的长度,机械结构的细微装配差异都可能会导致其自身的分布电感和分布电容发生变化,从而导致不同腔室间的腔室阻抗不能完全一致。这就造成了同一设计和工艺条件下,不同腔室间的工艺性能的不匹配。对于某些对腔室阻抗的变化非常敏感的工艺,即使利用阻抗匹配器已经完成阻抗匹配,也无法达到工艺要求。

技术实现要素:

[0005]

本发明实施例旨在至少解决现有技术中存在的技术问题之一,提出了一种半导体工艺设备及其阻抗调节方法,其可以使不同腔室间的腔室阻抗一致,从而可以在同一设计和工艺条件下,确保不同腔室间的工艺性能匹配。

[0006]

为实现上述目的,本发明实施例提供了一种半导体工艺设备,包括工艺腔室、阻抗匹配器和射频电源,所述工艺腔室中设置有卡盘装置,所述卡盘装置包括基座和设置在所述基座上,用于承载被加工工件的介质层,所述介质层中设置有射频电极,所述射频电极通过所述阻抗匹配器与所述射频电源电连接;所述基座通过接地结构接地,所述半导体工艺设备还包括阻抗调节电路,所述阻抗调节电路一端与所述基座的电连接,另一端接地,所述阻抗调节电路用于调节所述阻抗匹配器的输出端与所述接地结构的接地端之间的实际阻抗值,以使其与预设的标准阻抗值一致。

[0007]

可选的,所述阻抗调节电路与所述接地结构相互串联或并联。

[0008]

可选的,所述阻抗调节电路包括至少一个可调电容,或者至少一个可调电感,或者电性连接的至少一个可调电容和至少一个可调电感。

[0009]

可选的,所述至少一个可调电容和至少一个可调电感采用的电性连接方式包括并联、串联或者混联。

[0010]

可选的,所述卡盘装置为静电卡盘。

[0011]

作为另一个技术方案,本发明实施例还提供一种阻抗调节方法,应用于本发明实施例提供的上述半导体工艺设备,包括:

[0012]

在所述工艺腔室使用之前,检测所述阻抗匹配器的输出端与所述接地结构的接地端之间的实际阻抗值;

[0013]

将所述实际阻抗值与预设的标准阻抗值进行比较,并根据比较结果调节所述阻抗调节电路,使所述实际阻抗值与预设的标准阻抗值一致。

[0014]

可选的,所述标准阻抗值的获得方法包括:

[0015]

根据预设的工艺要求选定一标准腔室;

[0016]

在所述标准腔室未进行工艺时,检测所述标准腔室的所述阻抗匹配器的输出端与所述接地结构的接地端之间的实际阻抗值,并将其用作所述标准阻抗值。

[0017]

可选的,所述阻抗调节电路与所述接地结构相互串联;所述阻抗调节电路包括至少一个可调电容,或者至少一个可调电感,或者电性连接的至少一个可调电容和至少一个可调电感;

[0018]

所述将所述实际阻抗值与预设的标准阻抗值进行比较,并根据比较结果调节所述阻抗调节电路,以使所述实际阻抗值与预设的标准阻抗值一致,具体包括:

[0019]

若所述实际阻抗值为感性阻抗,则通过增大或减小所述至少一个可调电容的电容值和/或至少一个可调电感的电感值,来增大或减小所述实际阻抗值的感性分量;

[0020]

若所述实际阻抗值为容性阻抗,则通过增大或减小所述至少一个可调电容的电容值和/或至少一个可调电感的电感值,来减小或增大所述实际阻抗值的容性分量。

[0021]

可选的,所述阻抗调节电路与所述接地结构相互并联;所述阻抗调节电路包括至少一个可调电容,或者至少一个可调电感,或者电性连接的至少一个可调电容和至少一个可调电感;

[0022]

所述将所述实际阻抗值与预设的标准阻抗值进行比较,并根据比较结果调节所述阻抗调节电路,以使所述实际阻抗值与预设的标准阻抗值一致,具体包括:

[0023]

若所述实际阻抗值为感性阻抗,则通过增大至少一个可调电感的电感值,和/或减小所述至少一个可调电容的电容值,来增大所述实际阻抗值的感性分量;通过减小至少一个可调电感的电感值,和/或增大所述至少一个可调电容的电容值,来减小所述实际阻抗值的感性分量;

[0024]

若所述实际阻抗值为容性阻抗,则通过减小至少一个可调电感的电感值,和/或增大所述至少一个可调电容的电容值,来增大所述实际阻抗值的容性分量;通过增大至少一个可调电感的电感值,和/或减小所述至少一个可调电容的电容值,来减小所述实际阻抗值的容性分量。

[0025]

本发明实施例的有益效果:

[0026]

本发明实施例提供的半导体工艺设备及其阻抗调节方法的技术方案中,通过增设阻抗调节电路,该阻抗调节电路用于调节阻抗匹配器的输出端与接地结构的接地端之间的实际阻抗值,以使其与预设的标准阻抗值一致。这样,可以使不同腔室间的腔室阻抗一致,从而可以在同一设计和工艺条件下,确保不同腔室间的工艺性能匹配。

附图说明

[0027]

图1为静电卡盘的结构图;

[0028]

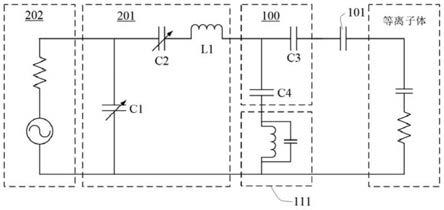

图2为现有的半导体工艺设备的射频回路的等效电路图;

[0029]

图3为本发明第一实施例提供的半导体工艺设备的射频回路的等效电路图;

[0030]

图4为本发明第一实施例提供的半导体工艺设备的结构图;

[0031]

图5为本发明第二实施例提供的半导体工艺设备的射频回路的等效电路图;

[0032]

图6为本发明第二实施例提供的半导体工艺设备的局部结构图;

[0033]

图7为本发明第三实施例提供的阻抗调节方法的流程框图。

具体实施方式

[0034]

为使本领域的技术人员更好地理解本发明的技术方案,下面结合附图对本发明实施例提供的半导体工艺设备及其阻抗调节方法进行详细描述。

[0035]

请一并参阅图1和图2,半导体工艺设备包括工艺腔室、阻抗匹配器201和射频电源202,该工艺腔室中设置有卡盘装置,该卡盘装置例如为静电卡盘100,具体可以包括基座109和设置在该基座109上的介质层104,其中,该介质层104用于承载被加工工件(例如晶圆101),且介质层104中设置有射频电极107和静电电极(图中未示出),该介质层104用于将包覆其中的射频电极107和静电电极(图中未示出)与外界电绝缘,并且介质层104中的射频电极107通过阻抗匹配器201与射频电源202电连接;基座109通过接地结构111接地,以使部分射频能量能够通过地回路返回射频电源,从而形成如图2所示的射频回路。另外,基座109中还可以设置冷却管路,用以通过与晶圆101进行热交换来控制晶圆101的温度。当然,在实际应用中,卡盘装置还可以采用其他任意结构,本发明实施例没有特别的限制。

[0036]

半导体工艺通常都在真空环境下进行,工艺腔室的压力很低,在这种情况下,晶圆和静电卡盘的传热效率很低。为了实现较好的热传导,通常会通过背吹管路向晶圆与静电卡盘之间通入一定压力的背吹气体,压力的大小例如为4torr-20torr。为了实现较好的匀气效果,静电卡盘的介质层104的上表面可以布置一定数量的沟槽和凸点(均未在图中示出),这样有助于背吹气体的扩散,从而可以提高背吹气体在晶圆与静电卡盘之间的分布均匀性,进而实现气体的匀热。

[0037]

如图2所示,阻抗匹配器201包括阻抗可调元件,例如该阻抗可调元件包括两个可调电容c1、c2和电感l1,当等离子体的阻抗发生变化时,通过调节两个可调电容c1、c2的电容值,可以实现射频阻抗匹配,从而可保证射频电源202的功率能够最大化的加载到工艺腔室。但是,在射频电极107与晶圆101之间以及在射频电极107与基座109之间分别形成了电容c3和电容c4。c3的两极极板分别为rf电极107和晶圆101,中间的介质层为104。基座109通过接地结构111接地,该接地结构例如为接地线缆、波纹管轴或者其他接地件、接地机械结构,但是,无论采用什么样的接地结构,都可能在接地结构111上存在分布电感和分布电容,而这些分布电感和分布电容对于不同的工艺腔室来说是不同的,而且无法通过阻抗匹配器实现不同腔室间的阻抗一致,腔室间的阻抗差异可能会导致耦合到等离子体的射频效率发生改变,同时影响到晶圆表面上形成的负偏压,最终导致不同腔室所沉积的薄膜的工艺参数存在差异。对于某些对腔室阻抗的变化非常敏感的工艺,例如,在使用物理气相沉积设备进行ta金属的沉积工艺时,对静电卡盘的接地阻抗非常的敏感,当接地阻抗发生变化时,即

使利用阻抗匹配器已经完成阻抗匹配,也无法达到工艺要求。而且,在工艺腔室被制造完成后,由接地结构111引起的分布电感和分布电容已经存在,很难调整。

[0038]

为了解决上述问题,如图3和图4所示,本发明第一实施例提供一种半导体工艺设备,包括工艺腔室400、阻抗匹配器201和射频电源202,工艺腔室400中设置有卡盘装置,以卡盘装置为静电卡盘100为例,其包括基座109和设置在该基座109上,用于承载被加工工件(例如为晶圆101)的介质层104,该介质层104中的射频电极107通过阻抗匹配器201与射频电源202电连接;基座109通过接地结构111接地。并且,半导体工艺设备还包括阻抗调节电路300,该阻抗调节电路300一端与基座109的电连接,另一端接地,例如,如图4所示,阻抗调节电路300集成在接地结构111中,并与接地结构111相互串联,这样,阻抗调节电路300可以直接补偿接地结构111自身存在的分布电感和分布电容,以调节阻抗匹配器201的输出端(图4中示出的位置a)与接地结构111的接地端(图4中示出的位置b)之间的实际阻抗值,以使其与预设的标准阻抗值一致。需要说明的是,实际阻抗值为包含实部与虚部的复数,这里,实际阻抗值与标准阻抗值一致,是指复数的实部与虚部均一致。

[0039]

在一些实施例中,阻抗调节电路300包括至少一个可调电容,或者至少一个可调电感,或者电性连接的至少一个可调电容和至少一个可调电感。例如,如图3所示,阻抗调节电路300包括一个可调电感l2和一个可调电容c5,二者相互串联,并且可调电感l2和可调电容c5与接地结构111相互串联。

[0040]

在实际应用中,当本实施例提供的工艺腔室完成制造之后,可以对未投入使用的工艺腔室的上述实际阻抗值进行检测,具体可以使用阻抗分析仪,将其两个探测端分别连接至阻抗匹配器201的输出端(图4中示出的位置a)与接地结构111的接地端(图4中示出的位置b),以检测阻抗匹配器201的输出端与接地结构111的接地端之间的实际阻抗值。然后,将该实际阻抗值与预设的标准阻抗值进行比较,若实际阻抗值与标准阻抗值一致,则无需进行调节操作;若实际阻抗值与标准阻抗值不一致,则根据实际阻抗值与标准阻抗值的差值调节阻抗调节电路300,直至上述实际阻抗值与预设的标准阻抗值一致。

[0041]

具体来说,若实际阻抗值为感性阻抗,则通过增大或减小至少一个可调电容的电容值和/或至少一个可调电感的电感值,来增大或减小实际阻抗值的感性分量;若实际阻抗值为容性阻抗,则通过增大或减小至少一个可调电容的电容值和/或至少一个可调电感的电感值,来减小或增大实际阻抗值的容性分量。

[0042]

在一些实施例中,上述标准阻抗值的获得方式可以包括以下步骤:

[0043]

根据预设的工艺要求选定一标准腔室,例如可以选择一台经过验证可以满足工艺要求的工艺腔室作为标准腔室;

[0044]

在上述标准腔室未进行工艺(例如等离子体腔室处于未起辉状态)时,检测该标准腔室的阻抗匹配器的输出端与接地结构的接地端之间的实际阻抗值,并将其用作标准阻抗值。

[0045]

需要说明的是,在本实施例中,阻抗调节电路300包括一个可调电感l2和一个可调电容c5,但是,本发明实施例并不局限于此,在实际应用中,可以根据工艺腔室的具体情况自由设计阻抗调节电路300,例如,当实际阻抗值与标准阻抗值的差值范围较小时,仅依靠微调即可达到腔室间的腔室阻抗一致,在这种情况下,仅单独设置可调电感或者可调电容即可;反之,当实际阻抗值与标准阻抗值的差值范围较大时,可以同时设置可调电感或者可

调电容。另外,可调电感和可调电容可以相互串联,或者也可以相互并联,或者还可以混联。

[0046]

本发明实施例提供的半导体工艺设备增设了阻抗调节电路300,该阻抗调节电路300用于调节阻抗匹配器201的输出端与接地结构111的接地端之间的实际阻抗值,以使其与预设的标准阻抗值一致。这样,可以使不同腔室间的腔室阻抗一致,从而可以在同一设计和工艺条件下,确保不同腔室间的工艺性能匹配。

[0047]

请一并参阅图5和图6,本发明第二实施例提供的半导体工艺设备,其与上述第一实施例相比,同样包括工艺腔室400

’

、阻抗匹配器201和射频电源202,并且,还包括阻抗调节电路300

’

。这些部件的结构和功能与上述第一实施例相同,在此不再赘述。下面仅对本实施例提供的半导体工艺设备与上述第一实施例的区别进行详细描述。

[0048]

具体地,阻抗调节电路300

’

与接地结构111相互并联。这种连接方式可以在不改变接地结构111的情况下实现阻抗调节电路300

’

的安装,从而可以解决因射频回路中接地结构111的接地部件较多、阻抗调节电路300

’

与接地结构111串接困难而导致的安装困难。

[0049]

在一些实施例中,阻抗调节电路300

’

包括至少一个可调电容,或者至少一个可调电感,或者电性连接的至少一个可调电容和至少一个可调电感。例如,如图5所示,阻抗调节电路300

’

包括一个可调电感l2和一个可调电容c5,二者相互并联,并且可调电感l2和可调电容c5与接地结构111相互并联。

[0050]

在实际应用中,当本实施例提供的工艺腔室完成制造之后,可以对未投入使用的工艺腔室的上述实际阻抗值进行检测,具体可以使用阻抗分析仪,将其两个探测端分别连接至阻抗匹配器201的输出端与接地结构111的接地端,以检测阻抗匹配器201的输出端与接地结构111的接地端之间的实际阻抗值。然后,将该实际阻抗值与预设的标准阻抗值进行比较,若实际阻抗值与标准阻抗值一致,则无需进行调节操作;若实际阻抗值与标准阻抗值不一致,则根据实际阻抗值与标准阻抗值的差值调节阻抗调节电路300

’

,直至上述实际阻抗值与预设的标准阻抗值一致。

[0051]

具体来说,若实际阻抗值为感性阻抗,则通过增大至少一个可调电感的电感值,和/或减小至少一个可调电容的电容值,来增大实际阻抗值的感性分量;通过减小至少一个可调电感的电感值,和/或增大至少一个可调电容的电容值,来减小实际阻抗值的感性分量;若实际阻抗值为容性阻抗,则通过减小至少一个可调电感的电感值,和/或增大至少一个可调电容的电容值,来增大实际阻抗值的容性分量;通过增大至少一个可调电感的电感值,和/或减小至少一个可调电容的电容值,来减小实际阻抗值的容性分量。

[0052]

本实施例提供的半导体工艺设备的其他结构和功能与上述第一实施例相同,在此不再赘述。

[0053]

请参阅图7,本发明第三实施例还提供一种阻抗调节方法,其应用于本发明上述各个实施例提供的半导体工艺设备,且包括以下步骤:

[0054]

s1、在工艺腔室使用之前,检测阻抗匹配器的输出端与接地结构的接地端之间的实际阻抗值;

[0055]

s2、将实际阻抗值与预设的标准阻抗值进行比较,并根据比较结果调节阻抗调节电路,以使上述实际阻抗值与预设的标准阻抗值一致。

[0056]

在一些实施例中,上述检测是在工艺腔室完成制造之后,且在投入使用之前进行的,由于完成制造的工艺腔室,其接地结构111引起的分布电感和分布电容通常是固定的,

因此,可以确保在对该工艺腔室的阻抗调节完成,并投入使用之后,腔室间的阻抗一致。

[0057]

在一些实施例中,上述标准阻抗值的获得方法包括:

[0058]

根据预设的工艺要求选定一标准腔室;

[0059]

在上述标准腔室未进行工艺时,检测标准腔室的阻抗匹配器的输出端与接地结构的接地端之间的实际阻抗值,并将其用作标准阻抗值。

[0060]

这样,可以使其他的新的工艺腔室的实际阻抗值均与该标准阻抗值一致,从而保证腔室间的阻抗一致,同时又能够使各个腔室的相关工艺指标均满足要求。

[0061]

以上述第一实施例采用的阻抗调节电路300为例,该阻抗调节电路300包括至少一个可调电容,或者至少一个可调电感,或者电性连接的至少一个可调电容和至少一个可调电感。例如,如图3所示,阻抗调节电路300包括一个可调电感l2和一个可调电容c5,二者相互串联,并且可调电感l2和可调电容c5与接地结构111相互串联。

[0062]

当本实施例提供的工艺腔室完成制造之后,可以对未投入使用的工艺腔室的上述实际阻抗值进行检测,具体可以使用阻抗分析仪,将其两个探测端分别连接至阻抗匹配器201的输出端(图4中示出的位置a)与接地结构111的接地端(图4中示出的位置b),以检测阻抗匹配器201的输出端与接地结构111的接地端之间的实际阻抗值。然后,将该实际阻抗值与预设的标准阻抗值进行比较,若实际阻抗值与标准阻抗值一致,则无需进行调节操作;若实际阻抗值与标准阻抗值不一致,则根据实际阻抗值与标准阻抗值的差值调节阻抗调节电路300,直至上述实际阻抗值与预设的标准阻抗值一致。

[0063]

具体来说,若实际阻抗值为感性阻抗,则通过增大或减小至少一个可调电容的电容值和/或至少一个可调电感的电感值,来增大或减小实际阻抗值的感性分量;若实际阻抗值为容性阻抗,则通过增大或减小至少一个可调电容的电容值和/或至少一个可调电感的电感值,来减小或增大实际阻抗值的容性分量。

[0064]

以上述第二实施例采用的阻抗调节电路300

’

为例,阻抗调节电路300

’

包括至少一个可调电容,或者至少一个可调电感,或者电性连接的至少一个可调电容和至少一个可调电感。例如,如图5所示,阻抗调节电路300

’

包括一个可调电感l2和一个可调电容c5,二者相互并联,并且可调电感l2和可调电容c5与接地结构111相互并联。

[0065]

在这种情况下,若实际阻抗值为感性阻抗,则通过增大至少一个可调电感的电感值,和/或减小至少一个可调电容的电容值,来增大实际阻抗值的感性分量;通过减小至少一个可调电感的电感值,和/或增大至少一个可调电容的电容值,来减小实际阻抗值的感性分量;若实际阻抗值为容性阻抗,则通过减小至少一个可调电感的电感值,和/或增大至少一个可调电容的电容值,来增大实际阻抗值的容性分量;通过增大至少一个可调电感的电感值,和/或减小至少一个可调电容的电容值,来减小实际阻抗值的容性分量。

[0066]

上述半导体工艺设备例如为物理气相沉积设备、刻蚀设备、化学气相沉积设备以及离子注入设备等等。

[0067]

可以理解的是,以上实施方式仅仅是为了说明本发明的原理而采用的示例性实施方式,然而本发明并不局限于此。对于本领域内的普通技术人员而言,在不脱离本发明的精神和实质的情况下,可以做出各种变型和改进,这些变型和改进也视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1