一种避免基板上阴极断裂的制程方法与流程

[0001]

本发明涉及硅基micro oled微显示生产制造领域,特别涉及一种避免基板上阴极断裂的制程方法。

背景技术:

[0002]

随着目前市场对显示器件的多样性及高性能性的需求扩大,极大的推动着显示技术的发展。基于面板结合半导体技术的硅基micro oled技术也在飞速发展。硅基micro oled微显示器件区别于常规利用非晶硅、微晶硅或低温多晶硅薄膜晶体管为背板的amoled器件,它以单晶硅芯片为基底,像素尺寸为传统显示器件的1/10,精细度远远高于传统器件。基于其技术优势和广阔的应用市场,它有望在消费电子领域掀起近眼显示的新浪潮。

[0003]

在目前的硅基micro oled微型显示器件的造过程中,在进行阳极刻蚀时,因为阳极本身的厚度及干法刻蚀的过刻深度,造成了一定的段差,此部分段差在经过oled后,会造成后续蒸镀阴极搭接不良即阴极断裂,进而造成基板的良率低下。

技术实现要素:

[0004]

本发明提出一种避免基板上阴极断裂的制程方法,该避免基板上阴极断裂的制程方法缩短工艺流程并避免阴极断裂。

[0005]

为达到上述目的,本发明的技术方案是这样实现的:

[0006]

一种避免基板上阴极断裂的制程方法,所述避免基板上阴极断裂的制程方法包括:在带有cmos电路的硅基晶圆上铺设用于形成pdl层的成膜得到第一基板;在所述第一基板的硅基晶圆上涂敷光刻胶后将已涂敷光刻胶的硅基晶圆进行曝光显影得到第二基板;对所述第二基板的硅基晶圆进行干法蚀刻得到包含有pdl层和曝光显影后光刻胶的第三基板;将所述第三基板上的曝光显影后的光刻胶清洗去除得到第四基板;对所述第四基板进行阳极镀膜得到第五基板;对所述第五基板进行研磨,以去除所述pdl层上的阳极镀膜,以使得处于所述pdl层间隙中的阳极镀膜与所述pdl层高度相同。

[0007]

优选地,在得到第一基板之前,所述避免基板上阴极断裂的制程方法包括:将带有cmos电路的硅基晶圆进行清洗。

[0008]

优选地,所述在带有cmos电路的硅基晶圆上铺设用于形成pdl层的成膜得到第一基板包括:在带有cmos电路的硅基晶圆上采用化学气相沉积法沉积sin膜层得到第一基板。

[0009]

优选地,所述对所述第四基板进行阳极镀膜被配置为采用物理气相沉积法。

[0010]

优选地,所述对所述第五基板进行研磨被配置为采用化学机械研磨法。

[0011]

相对于现有技术,本发明先进行像素定义层图形化,再进行孔内填充阳极工艺,最后研磨,有效的避免阳极和像素定义层之间较大的段差及角度对后续蒸镀阴极搭接造成的不良。另一方面,可以缩减工艺制程,降低了工艺难度,避免了因阳极和像素定义层之间的套刻精度而造成的良率问题,提高了阳极和像素定义层的良率,节约成本。

[0012]

本发明的其它特征和优点将在随后的具体实施方式部分予以详细说明。

附图说明

[0013]

构成本发明的一部分的附图用来提供对本发明的进一步理解,本发明的示意性实施方式及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中:

[0014]

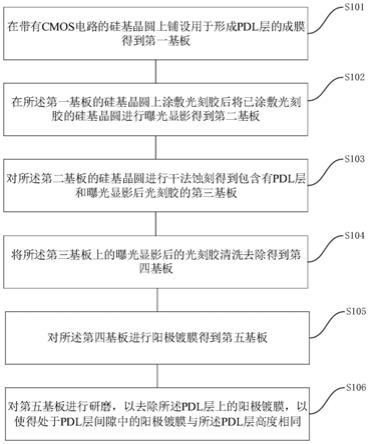

图1为本发明的避免基板上阴极断裂的制程方法的流程图;

[0015]

图2为本发明的第一基板的结构示意图;

[0016]

图3为本发明的第二基板的结构示意图;

[0017]

图4为本发明的第三基板的结构示意图;

[0018]

图5为本发明的第四基板的结构示意图;

[0019]

图6为本发明的第五基板的结构示意图;以及

[0020]

图7为本发明的最终制得的基板的结构示意图。

[0021]

附图标记说明:

[0022]

1、sin膜层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

2、晶圆

[0023]

3、光刻胶

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

4、阳极

具体实施方式

[0024]

以下结合附图对本发明的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明,并不用于限制本发明。

[0025]

图1是本发明的一种避免基板上阴极断裂的制程方法,所述避免基板上阴极断裂的制程方法包括:

[0026]

s101,在带有cmos电路的硅基晶圆2上铺设用于形成pdl层的成膜得到第一基板,所述第一基板的结构如图2所示。

[0027]

其中,在带有cmos电路的硅基晶圆2上采用化学气相沉积法(cvd,chemical vapour deposition)沉积sin膜层1得到第一基板。

[0028]

s102,在所述第一基板的硅基晶圆2上涂敷光刻胶3后将已涂敷光刻胶3的硅基晶圆2进行曝光显影得到第二基板,所述第二基板的结构如图3所示。

[0029]

s103,对所述第二基板的硅基晶圆2进行干法蚀刻得到包含有pdl层和曝光显影后光刻胶3的第三基板,所述第三基板的结构如图4所示。

[0030]

s104,将所述第三基板上的曝光显影后的光刻胶3清洗去除得到第四基板,所述第四基板的结构如图5所示。

[0031]

s105,对所述第四基板进行阳极4镀膜得到第五基板,所述第五基板的结构如图6所示。

[0032]

s106,对所述第五基板进行研磨,以去除所述pdl层上的阳极4镀膜,以使得处于所述pdl层间隙中的阳极4镀膜与所述pdl层高度相同。

[0033]

优选地,在步骤s101之前,所述避免基板上阴极断裂的制程方法包括:将带有cmos电路的硅基晶圆2进行清洗。

[0034]

优选地,所述对所述第四基板进行阳极4镀膜被配置为采用物理气相沉积法pvd(physical vapor deposition)。

[0035]

优选地,所述对所述第五基板进行研磨被配置为采用化学机械研磨法(cmp,chemical mechanical polish)。

[0036]

综上所述,在执行完s106后的基板为最终所需的结构,如图7所示,阳极4嵌入在pdl层(像素定义层)的空隙之间,并且pdl层与阳极4的高度相同,可以有效的避免以上两者之间形成较大的段差,以及刻蚀后形成的角度问题,蒸镀后阴极不会断裂。另一方面,简化了工艺流程,降低了工艺难度,避免了因阳极4和像素定义层之间的套刻精度而造成的良率问题,提高了阳极4和像素定义层的良率,节约成本。现有技术中,阳极4和像素定义层的传统制程工艺为pvd成膜、黄光图形化定义、干法刻蚀、去胶清洗、cvd成膜、黄光图形化定义、干法刻蚀、去胶清洗,整个工艺具有8个步骤,较为繁琐,本发明修改为6步,减少了工艺流程。解决阳极4和像素定义层的段差而造成的阴极断裂问题。

[0037]

以上所述仅为本发明的较佳实施方式而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1