半导体装置、储层计算系统以及半导体装置的制造方法与流程

1.本公开涉及半导体装置、储层计算系统以及半导体装置的制造方法。

背景技术:

2.为了提供一种利用人工智能(artificial intelligence)的先进的信息处理服务,正在开发一种面向ai的计算系统。正在开发通过采用受生物体的神经模型启发的神经模态计算来实现这样的系统的动作。其中,由于储层计算能够进行时间序列信息处理,所以作为提高动画识别、预测等ai的技术被期待。在储层计算系统中,使用被称为储层电路的包含非线性特性不同的多个非线性元件的网络型的电路。

3.专利文献1:日本特开平8-213561号公报

4.专利文献2:日本特开2011-238909号公报

5.专利文献3:日本特表2015-529006号公报

6.非专利文献1:extended abstracts of the 2019international conference on solid state devices and materials,nagoya,2019,pp195-196

7.难以以较高的集成度配置非线性特性不同的多个非线性元件。

技术实现要素:

8.本公开的目的在于提供一种能够以较高的集成度配置非线性特性不同的多个非线性元件的半导体装置、储层计算系统以及半导体装置的制造方法。

9.根据本公开的一个方式,提供一种半导体装置,具有:多个隧道二极管,分别具备第一导电型的第一半导体区域和设置在上述第一半导体区域上且具有纳米线的形状的第二导电型的第二半导体区域;绝缘膜,覆盖上述第二半导体区域的侧面;多个第一电极,分别与上述第一半导体区域连接;以及多个第二电极,分别与上述第二半导体区域连接,上述第二电极具有第一面,上述第一面隔着上述绝缘膜与上述第二半导体区域的侧面对置,在上述多个隧道二极管之间,上述第二半导体区域的直径不同。

10.根据本公开,能够以较高的集成度配置非线性特性不同的多个非线性元件。

附图说明

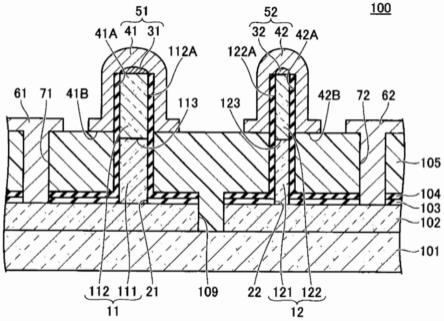

11.图1是表示第一实施方式的半导体装置的剖视图。

12.图2是表示动作时的第一实施方式的半导体装置的剖视图。

13.图3是表示纳米线的电压-电流特性的图。

14.图4是表示第一实施方式的半导体装置的制造方法的剖视图(其1)。

15.图5是表示第一实施方式的半导体装置的制造方法的剖视图(其2)。

16.图6是表示第一实施方式的半导体装置的制造方法的剖视图(其3)。

17.图7是表示第一实施方式的半导体装置的制造方法的剖视图(其4)。

18.图8是表示第一实施方式的半导体装置的制造方法的剖视图(其5)。

19.图9是表示第一实施方式的半导体装置的制造方法的剖视图(其6)。

20.图10是表示第一实施方式的半导体装置的制造方法的剖视图(其7)。

21.图11是表示第一实施方式的半导体装置的制造方法的剖视图(其8)。

22.图12是表示第一实施方式的半导体装置的制造方法的剖视图(其9)。

23.图13是表示具备直径不同的各种第二半导体区域的纳米线的电压-电流特性的图。

24.图14是表示具备掺杂浓度不同的各种第二半导体区域的纳米线的电压-电流特性的图。

25.图15是表示第二实施方式的储层电路的电路图。

26.图16是表示第二实施方式的储层电路的剖视图。

27.图17是表示第二实施方式的变形例的储层电路的电路图。

28.图18是表示第三实施方式的储层电路的电路图。

29.图19是表示第三实施方式的储层电路的剖视图。

30.图20是表示第四实施方式的储层计算系统的框图。

具体实施方式

31.以下,参照附图对本公开的实施方式进行具体说明。此外,在本说明书以及附图中,具有通过对于具有实质相同的功能结构的构成要素,标注相同的附图标记,省略重复的说明的情况。

32.(第一实施方式)

33.对第一实施方式进行说明。第一实施方式涉及具备具有纳米线的形状的半导体区域的半导体装置。图1是表示第一实施方式的半导体装置的剖视图。

34.如图1所示,在第一实施方式的半导体装置100中,在基板101上形成有n型半导体层102,在n型半导体层102上形成有绝缘膜103。在绝缘膜103上,形成有到达n型半导体层102的开口部21和开口部22。例如,基板101是半绝缘性(semi-insulating:si)-gaas(111)b基板,n型半导体层102是厚度为100nm~300nm的n型gaas层。例如,绝缘膜103是厚度为40nm~60nm的氮化硅膜,开口部21和开口部22的直径为40nm~200nm。开口部21的直径大于开口部22的直径。

35.半导体装置100具有通过开口部21向基板101的上方生长的第一纳米线11和通过开口部22向基板101的上方生长的第二纳米线12。例如,第一纳米线11以及第二纳米线12的直径为40nm~200nm。第一纳米线11比第二纳米线12粗。n型半导体层102通过元件分离槽109被分离为与第一纳米线11连接的区域和与第二纳米线12连接的区域。

36.第一纳米线11具有n型的第一半导体区域111和p型的第二半导体区域112。第一半导体区域111设置在n型半导体层102上,向上方延伸。第二半导体区域112设置在第一半导体区域111上,向上方延伸。在第二半导体区域112上形成有金属膜31。金属膜31例如是直径为40nm~200nm的金(au)膜。

37.第二纳米线12具有n型的第一半导体区域121和p型的第二半导体区域122。第一半导体区域121设置在n型半导体层102上,向上方延伸。第二半导体区域122设置在第一半导体区域121上,向上方延伸。在第二半导体区域122上形成有金属膜32。金属膜32例如是直径

为40nm~200nm的金(au)膜。

38.第二半导体区域112和第二半导体区域122具有纳米线的形状。第一半导体区域111和第一半导体区域121也可以具有纳米线的形状。例如,第一半导体区域111和第一半导体区域121是n型inas的纳米线,第二半导体区域112和第二半导体区域122是p型gaas

1-x

sb

x

的纳米线。gaas

1-x

sb

x

的sb组成比x优选为0.8以上,sb组成比x也可以为1.0。n型的第一半导体区域111和p型的第二半导体区域112相互隧道接合,n型的第一半导体区域121和p型的第二半导体区域122相互隧道接合。第一纳米线11以及第二纳米线12是隧道二极管的一个例子。

39.第一半导体区域111和第一半导体区域121的高度(长度)例如是0.5μm~0.7μm,第一半导体区域111的高度和第一半导体区域121的高度也可以相等。第二半导体区域112和第二半导体区域122的高度(长度)例如是1.0μm~1.5μm,第二半导体区域112的高度和第二半导体区域122的高度也可以相等。第一纳米线11以及第二纳米线12的高度(长度)例如是1.5μm~2.0μm,第一纳米线11的高度和第二纳米线12的高度也可以相等。

40.形成有覆盖第一纳米线11的侧面以及第二纳米线12的侧面的绝缘膜104。绝缘膜104例如是厚度为10nm~30nm的氧化铝膜或者氧化铪膜。这里所说的厚度是与第二半导体区域112、122的侧面112a、122a垂直的方向上的厚度。绝缘膜104也形成在绝缘膜103上。

41.在绝缘膜104上形成有有机绝缘膜105。有机绝缘膜105例如是苯并环丁烯(bcb)的膜。有机绝缘膜105的上表面位于比第一半导体区域111与第二半导体区域112的接合界面113以及第一半导体区域121与第二半导体区域122的接合界面123靠上方。

42.在有机绝缘膜105上,形成有与金属膜31接触的金属膜41以及与金属膜32接触的金属膜42。金属膜41和金属膜42例如是铂(pt)膜和铂(pt)膜上的金(au)膜的层叠膜。金属膜41具有隔着绝缘膜104与第二半导体区域112的侧面112a对置的面41a。金属膜42具有隔着绝缘膜104与第二半导体区域122的侧面122a对置的面42a。例如,金属膜41的下表面41b以及金属膜42的下表面42b位于比第一半导体区域111与第二半导体区域112的接合界面113以及第一半导体区域121与第二半导体区域122的接合界面123靠上方。金属膜31和金属膜41包含于阳极电极51,阳极电极51与第二半导体区域112欧姆接触。金属膜32和金属膜42包含于阳极电极52,阳极电极52与第二半导体区域122欧姆接触。阳极电极51和阳极电极52是第二电极的一个例子。面41a和面42a是第一面的一个例子。

43.在有机绝缘膜105、绝缘膜104以及绝缘膜103形成有开口部71和开口部72,其中,该开口部71到达与n型半导体层102的第一半导体区域111连接的区域,该开口部72到达与n型半导体层102的第一半导体区域121连接的区域。在有机绝缘膜105上,形成有通过开口部71与n型半导体层102接触的阴极电极61以及通过开口部72与n型半导体层102接触的阴极电极62。金属膜41和金属膜42例如是金锗(auge)膜和金锗膜上的金(au)膜的层叠膜。阴极电极61和阴极电极62是第一电极的一个例子。

44.在这里,对半导体装置100的作用进行说明。图2是表示动作时的第一实施方式的半导体装置100的剖视图。图3是表示第一纳米线11以及第二纳米线12的电压-电流特性的图。

45.若在阳极电极51与阴极电极61之间施加正向的电压,则如图2所示,由于来自金属膜41的电场的影响,在第二半导体区域112的侧面112a的附近形成耗尽层114。同样地,若在

阳极电极52与阴极电极62之间施加正向的电压,则如图2所示,由于来自金属膜42的电场的影响,在第二半导体区域122的侧面122a的附近形成耗尽层124。若正向的电压的大小为相同程度,则耗尽层114和耗尽层124的厚度为相同程度。在半导体装置100中,第二半导体区域112的直径大于第二半导体区域122的直径。因此,若耗尽层114和耗尽层124的厚度为相同程度,则耗尽层114在径向上占据第二半导体区域112的比例与耗尽层124在径向上占据第二半导体区域122的比例相比变小。因此,如图3所示,第一纳米线11的电压-电流特性和第二纳米线12的电压-电流特性不同。换句话说,在第一纳米线11与第二纳米线12之间,非线性特性不同。例如,第一纳米线11作为江崎二极管发挥作用,示出包含负性电阻成分的s字形特性,与此相对第二纳米线12示出简单的整流特性。

46.绝缘膜104的厚度优选为10nm以上且30nm以下,更为优选为10nm以上且20nm以下。在绝缘膜104过薄的情况下,存在无法充分地确保第二半导体区域112和金属膜41之间的绝缘性以及第二半导体区域122和金属膜42之间的绝缘性的担忧。在绝缘膜104过厚的情况下,存在不能够充分地形成耗尽层114和耗尽层124的担忧。

47.接下来,对半导体装置100的制造方法进行说明。图4~图12是表示第一实施方式的半导体装置100的制造方法的剖视图。

48.首先,如图4所示,在基板101上形成n型半导体层102。n型半导体层102例如能够通过有机金属化学气相生长(metal organic chemical vapor deposition:mocvd)法来生长。接下来,在n型半导体层102上形成绝缘膜103。

49.之后,如图5所示,在绝缘膜103上形成开口部21和开口部22。开口部21和开口部22例如能够通过利用光刻形成掩模并使用掩模蚀刻绝缘膜103来形成。开口部21和开口部22的直径为40nm~200nm,开口部21的直径大于开口部22的直径。接着,作为纳米线的催化剂,在开口部21内,形成例如圆板状的金属膜31,并在开口部22内,形成例如圆板状的金属膜32。作为金属膜31和金属膜32的材料,例如使用金(au)。像这样,得到具备基板101、n型半导体层102、绝缘膜103、金属膜31以及金属膜32的晶体生长用的基板。形成有开口部21和开口部22的绝缘膜103是生长掩模的一个例子。

50.接下来,如图6所示,使由n型的gaas构成且具有纳米线的形状的第一半导体区域111和第一半导体区域121在基板101的上方生长。使第一半导体区域111从开口部21的内侧生长,第一半导体区域121从开口部22的内侧生长。第一半导体区域111和第一半导体区域121例如能够通过mocvd法来生长。例如,生长温度为400℃~450℃,第一半导体区域111和第一半导体区域121的高度(长度)为0.5μm~0.7μm。例如,ga的原料使用三乙基镓(tega),as的原料使用胂(ash3)。另外,n型杂质的原料使用硫化氢(h2s),作为n型杂质掺杂硫黄(s)。s浓度例如为1

×

10

18

cm

-3

~1

×

10

20

cm

-3

。第一半导体区域111和第一半导体区域121的组成相互相等,第一半导体区域111和第一半导体区域121所包含的n型杂质的浓度也相互相等。

51.进一步,同样地如图6所示,使由p型的gaassb构成且具有纳米线的形状的第二半导体区域112和第二半导体区域122在基板101的上方生长。使第二半导体区域112在第一半导体区域111上生长,第二半导体区域122在第一半导体区域121上生长。第二半导体区域112和第二半导体区域122能够与第一半导体区域111和第一半导体区域121相同地通过mocvd法来生长。例如,生长温度为400℃~450℃,第二半导体区域112和第二半导体区域122的高度(长度)为1.0μm~1.5μm。例如,ga的原料使用三乙基镓(tega),as的原料使用胂

(ash3),sb的原料使用三甲基锑(tmsb)。另外,p型杂质的原料使用二乙基锌(dezn),作为p型杂质掺杂zn。zn浓度例如为1

×

10

18

cm

-3

~1

×

10

20

cm

-3

。第二半导体区域112和第二半导体区域122的组成相互相等,第二半导体区域112和第二半导体区域122所包含的p型杂质的浓度也相互相等。

52.其结果是,得到具备第一半导体区域111和第二半导体区域112的第一纳米线11、以及具备第一半导体区域121和第二半导体区域122的第二纳米线12。第一纳米线11的直径大于第二纳米线12的直径。

53.接下来,如图7所示,形成绝缘膜104,该绝缘膜104覆盖第一纳米线11、第二纳米线12以及绝缘膜103。作为绝缘膜104,例如形成厚度为10nm~30nm,优选为10nm~20nm的氧化铝膜或者氧化铪膜。绝缘膜104例如能够通过原子层堆积(atomic layer deposition:ald)法来形成。

54.之后,如图8所示,在绝缘膜104、绝缘膜103以及n型半导体层102形成元件分离槽109。元件分离槽109形成为将n型半导体层102分离为与第一纳米线11连接的区域和与第二纳米线12连接的区域。元件分离槽109例如能够通过利用光刻形成掩模并使用掩模蚀刻绝缘膜104、绝缘膜103以及n型半导体层102来形成。

55.接着,如图9所示,填埋元件分离槽109,并且在绝缘膜104上形成有机绝缘膜105。有机绝缘膜105优选以其上表面的整体位于比金属膜31和金属膜32的顶部靠上方的程度的厚度来形成。作为有机绝缘膜105,例如形成bcb膜。

56.接下来,如图10所示,将有机绝缘膜105干式蚀刻到其上表面位于比第一纳米线11以及第二纳米线12的顶部靠下方300nm左右的程度的厚度。在干式蚀刻中,例如能够使用四氟化碳(cf4)和氧(o2)的混合气体。利用有机绝缘膜105与绝缘膜104之间的蚀刻速率之差,也去除绝缘膜104的覆盖金属膜31和金属膜32的部分。当在对有机绝缘膜105进行干式蚀刻时无法充分地去除绝缘膜104的覆盖金属膜31和金属膜32的部分的情况下,也可以在对有机绝缘膜105进行干式蚀刻后通过例如使用氩(ar)离子的离子溅射来去除绝缘膜104的覆盖金属膜31和金属膜32的部分。

57.之后,如图11所示,在有机绝缘膜105上,形成与金属膜31接触的金属膜41和与金属膜32接触的金属膜42。作为金属膜31和金属膜32,例如形成铂(pt)膜和铂膜上的金(au)膜的层叠膜。金属膜31和金属膜41包含于阳极电极51,金属膜32和金属膜42包含于阳极电极52。

58.接着,如图12所示,在有机绝缘膜105、绝缘膜104以及绝缘膜103形成开口部71和开口部72,其中,该开口部71到达n型半导体层102的与第一半导体区域111连接的区域,该开口部72到达n型半导体层102的与第一半导体区域121连接的区域。开口部71和开口部72例如能够通过利用光刻形成掩模并使用掩模蚀刻有机绝缘膜105、绝缘膜104以及绝缘膜103来形成。绝缘膜104以及绝缘膜103也可以通过例如使用氩(ar)离子的离子溅射来去除。在形成开口部71和开口部72后,在有机绝缘膜105上,形成通过开口部71与n型半导体层102接触的阴极电极61和通过开口部72与n型半导体层102接触的阴极电极62。作为金属膜41和金属膜42,例如,形成金锗(auge)膜和金锗膜上的金(au)膜的层叠膜。

59.像这样,能够制造第一实施方式的半导体装置100。

60.根据该方法,能够简便地制造以高集成度配置电压-电流特性不同的多个纳米线

(第一纳米线11以及第二纳米线12)的半导体装置100。因此,能够以高集成度配置非线性特性不同的多个非线性元件。

61.在第一实施方式中,在基板101的上方仅设置有第一纳米线11以及第二纳米线12,但也可以设置更多的纳米线。

62.第一半导体区域111和第一半导体区域121无需具有纳米线的形状,但第一半导体区域111和第一半导体区域121具有纳米线的形状容易形成具有纳米线的形状的第二半导体区域112和第二半导体区域122。

63.如上述那样,第一纳米线11以及第二纳米线12的电压-电流特性根据第二半导体区域112和第二半导体区域122的直径而变化。在这里,对第二半导体区域的直径和电压-电流特性的关系进行说明。图13是表示具备直径不同的各种第二半导体区域的纳米线的电压-电流特性的图。在图13中,示出以5

×

10

17

cm

-3

的浓度掺杂p型杂质,且具有具备20nm~200nm的直径d的第二半导体区域的纳米线的电压-电流特性。通过使用正向电流从微安培级迁移至纳米安培级的直径区域,能够使正向隧道电流较大地变化,能够集中准备多种非线性性元件。从该观点考虑,在图13所示的例子中,优选直径为60nm~200nm左右。

64.第一纳米线11以及第二纳米线12的电压-电流特性不仅根据第二半导体区域112和第二半导体区域122的直径而变化,也根据第二半导体区域112和第二半导体区域122所包含的p型杂质的掺杂浓度(以下,有称为掺杂浓度的情况)而变化。在这里,对掺杂浓度和电压-电流特性的关系进行说明。图14是表示具备掺杂浓度不同的各种第二半导体区域的纳米线的电压-电流特性的图。在图14中,示出直径为60nm,且具有具备1

×

10

17

cm

-3

~5

×

10

18

cm

-3

的掺杂浓度ρ的第二半导体区域的纳米线的电压-电流特性。如上述那样,通过使用正向电流从微安培级迁移至纳米安培级的直径区域,能够使正向隧道电流较大地变化,能够集中准备多种非线性性元件。从该观点考虑,在图14所示的例子中,优选掺杂浓度为5

×

10

17

cm

-3

~5

×

10

18

cm

-3

左右。

65.本技术发明人等为了使图13以及图14所示的关系更加一般化而进行了深入研究。其结果是,发现了在第二半导体区域的直径d(cm)以及掺杂浓度ρ(cm

-3

)满足下述的式(1)的情况下,使用具备直径不同的第二半导体区域的多个纳米线,可有效地获得多种非线性元件。

66.1.8

×

107≤d2×

ρ≤2

×

108……

式(1)

67.此外,当第二半导体区域的直径在高度方向上变化的情况下,例如在第二半导体区域的直径越靠近基板侧越大的情况下,式(1)中的直径d是第二半导体区域的上表面的直径。

68.(第二实施方式)

69.对第二实施方式进行说明。第二实施方式涉及具备非线性特性不同的多个纳米线的储层电路。储层电路是半导体装置的一个例子。图15以及图16是表示第二实施方式的储层电路的图。图15是表示多个纳米线的连接关系的电路图,图16是表示多个纳米线的连接关系的剖视图。在图16中,省略了绝缘膜等部分结构。

70.如图16所示,第二实施方式的储层电路200具有基板101、n型半导体层102、多个纳米线20、布线233、布线234、布线235、布线236、输入端子231以及输出端子232。

71.纳米线20具有n型的第一半导体区域201和p型的第二半导体区域202。第一半导体

区域201设置在n型半导体层102上,向上方延伸。第二半导体区域202设置在第一半导体区域201上,向上方延伸。在多个纳米线20之间,直径不同。无需在所有的纳米线20之间直径不同,也可以包含直径相等的纳米线20。n型半导体层102按每条纳米线20元件分离。

72.如图15所示,例如,多个纳米线20在相互正交的2个方向(x方向、y方向)上等间隔地配置。即,在俯视时,多个纳米线20在基板101的上方配置成格子状。例如,输入端子231以及输出端子232与由在x方向上排列的多个纳米线20构成的行的数量相同数目地设置。布线233连接输入端子231和在x方向上排列的多个纳米线20中的位于一端的纳米线20的第二半导体区域202。布线234连接输出端子232和与在x方向上排列的多个纳米线20中的位于另一端的纳米线20的第一半导体区域201连接的n型半导体层102。布线235在x方向上相邻的两个纳米线20之间连接与一个第一半导体区域201连接的n型半导体层102和另一个第二半导体区域202。布线236在y方向上相邻的两个纳米线20之间连接一个第二半导体区域202和另一个第二半导体区域202。

73.布线233的一部分以及布线236的一部分作为阳极电极发挥作用,布线234的一部分作为阴极电极发挥作用。布线235的一部分作为阳极电极发挥作用,其他部分作为阴极电极发挥作用。布线233、235以及236的作为阳极电极发挥作用的部分与第一实施方式中的金属膜41和金属膜42相同,构成为具有隔着绝缘膜204与第二半导体区域202的侧面对置的面。

74.根据第二实施方式,非线性特性不同的多个纳米线20连接成网络状。因此,得到以较高的集成度包含具备多种非线性特性的多个非线性元件的储层电路200。另外,由于在多个纳米线20之间,即使材料以及组成相同,如果直径不同则非线性特性也不同,所以能够无需复杂的处理地制造。

75.在图15中图示出6

×

6的36个纳米线20,但优选设置有更多的纳米线20。

76.(第二实施方式的变形例)

77.对第二实施方式的变形例进行说明。变形例在多个纳米线20之间的连接关系的点与第二实施方式不同。图17是表示第二实施方式的变形例的储层电路的图。图17是表示多个纳米线的连接关系的电路图。

78.如图17所示,在变形例的储层电路200a中,在x方向上相邻的纳米线20的对的一部分未设置布线235。另外,在y方向上相邻的纳米线20的对的一部分未设置布线236。

79.其他结构与第二实施方式相同。

80.根据变形例的储层电路200a,与第二实施方式的储层电路200相比,能够提高非线性元件的网络的不规则性。

81.在第二实施方式或者其变形例中,经由布线多个第二半导体区域连接、或第一半导体区域与第二半导体区域连接,但也可以经由布线多个第一半导体区域连接。

82.(第三实施方式)

83.对第三实施方式进行说明。第三实施方式涉及具备非线性特性不同的多个纳米线,且包含可变加权电路的储层电路。储层电路是半导体装置的一个例子。图18以及图19是表示第三实施方式的储层电路的图。图18是表示多个纳米线的连接关系的电路图,图19是表示多个纳米线的连接关系的剖视图。在图19中,省略绝缘膜等部分结构。

84.如图19所示,第三实施方式的储层电路300具有基板101、n型半导体层102、多个纳

米线20、布线233、布线234、布线235、布线236、布线237、可变加权电路238、输入端子231以及输出端子232。基板101、n型半导体层102、多个纳米线20、布线233、布线235以及布线236与第二实施方式同样地构成。

85.可变加权电路238包含氧化物忆阻器239,该氧化物忆阻器239按由在x方向上排列的多个纳米线20构成的每一行来设置。布线234连接氧化物忆阻器239的一个端部和n型半导体层102,其中,该n型半导体层102与在x方向上排列的多个纳米线20中的位于另一端的纳米线20的第一半导体区域201连接。布线237连接输出端子232和n型半导体层102,其中,该n型半导体层102连接氧化物忆阻器239的另一个端部。氧化物忆阻器239是模拟存储器的一个例子。

86.其他结构与第二实施方式相同。

87.在第三实施方式的储层电路300中,氧化物忆阻器239的电阻根据通过布线234从多个纳米线20输出的电流(信号的强度)而变化,可变加权电路238保持权重信息。第三实施方式的储层电路300相当于储层计算系统中的集成到线性读出的设备。

88.(第四实施方式)

89.对第四实施方式进行说明。第四实施方式涉及具备储层电路的储层计算系统。图20是表示第四实施方式的储层计算系统的框图。

90.如图20所示,第四实施方式的储层计算系统400具有输入电路401、储层电路402以及输出电路403。储层电路402包含读出加权部404。储层计算系统400也可以还具有学习数据电路405。作为储层电路402,也可以使用储层电路200或者储层电路300。

91.在学习储层计算系统400时,从学习数据电路405向读出加权部404输入学习数据(教师数据),并调整读出加权部404,以进行适当的加权。读出加权部404是模拟存储器的一个例子。

92.在利用储层计算系统400时,从储层电路402切断学习数据电路405。而且,从输入电路401向储层电路402输入数据,在储层电路402中,由读出加权部404对所输入的数据进行加权等运算处理。从输出电路403输出储层电路402中的运算处理的结果。

93.根据第四实施方式,能够以较高的集成度配置作为储层计算系统400所包含的多个非线性元件的纳米线。

94.以上,对优选的实施方式等进行了详细叙述,但并不限于上述的实施方式等,能够在不脱离权利要求书所记载的范围内,对上述的实施方式等施加各种变形以及置换。

95.附图标记说明

96.11、12、20

…

纳米线;21、22

…

开口部;31、32、41、42

…

金属膜;41a、42a

…

面;51、52

…

阳极电极;61、62

…

阴极电极;100

…

半导体装置;103、104、204、绝缘膜;111、112、121、122、201、202

…

半导体区域;112a、122a

…

侧面;113、123

…

接合界面;114、124

…

耗尽层;200、200a、300

…

储层电路;231

…

输入端子;232

…

输出端子;233、234、235、236、237

…

布线;238

…

可变加权电路;239

…

氧化物忆阻器;400

…

储层计算系统;401

…

输入电路;402

…

储层电路;403

…

输出电路;404

…

读出加权部;405

…

学习数据电路。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1