封装载板及应用其的芯片封装结构的制作方法

1.本发明涉及一种封装载板及应用其的芯片封装结构,特别是涉及一种应用在覆晶封装的封装载板及应用其的芯片封装结构。

背景技术:

2.现有的集成电路芯片封装组件通常包括集成电路芯片以及封装基板,且集成电路芯片是设置在一封装基板上。封装基板具有内连线路结构以及位于其底部的一锡球阵列。封装基板的内连线路结构包括多个接地导电孔(ground via)以及电源导电孔(power via),以建立对集成电路芯片的供电路径。锡球阵列包括多个锡球,以作为外部接点。当集成电路芯片设置在封装基板上时,集成电路芯片可通过封装基板的内连线路结构以及锡球阵列,以电连接到电路板。

3.然而,随着集成电路封装组件的功能增多,且工作速度变快,集成电路封装组件的功率损耗也越来越大。若内连线路结构所建立的供电路径设计不良,可能导致高速或高功耗的集成电路封装组件的操作速度不如预期,或者因电压过低而失效。

4.进一步而言,当集成电路芯片封装组件运作时,可能需要在短时间内由低功率状态切换到高功率状态,因此对于供电电压稳定度的要求更高。目前,现有的集成电路芯片封装组件,如:大型系统单芯片(system on chip, soc),运作时,可能需要在短时间内急遽增加工作电流。由于内连线路结构会有寄生电感或寄生阻抗,电流瞬时变化量的增加及寄生电感会导致瞬间电压下降,而影响的电源完整性(power integrity),并导致电路可能因电压过低而失效。

5.因此,如何设计供电路径,以在不增加尺寸的情况下,有效地提升集成电路芯片封装组件在运作时的电源完整性,仍为该项事业所欲解决的重要课题之一。

技术实现要素:

6.本发明所要解决的技术问题在于,针对现有技术的不足提供一种封装载板及应用其的芯片封装结构,以提升芯片封装结构在运作时的电源完整性。

7.为了解决上述的技术问题,本发明所采用的其中一技术方案是提供一种封装载板,其包括:层压板、焊垫阵列、多个接地导电结构以及多个电源导电结构。层压板至少包括一第一线路层、第二线路层与第三线路层。第一线路层位于层压板的最外侧,且第二线路层位于第一线路层与第三线路层之间。焊垫阵列电连接第一线路层,且包括多个电源焊垫组与多个接地焊垫组。多个接地导电结构在第一方向上排成一第一行。至少一接地导电结构包括由第一线路层延伸至第二线路层的两个第一接地导电柱以及由第二线路层延伸至第三线路层的一第二接地导电柱。两个第一接地导电柱以及第二接地导电柱沿着第一方向排列,且第二接地导电柱的位置是位于两个第一接地导电柱的位置之间。多个电源导电结构在第一方向上排成第二行。至少一电源导电结构包括由第一线路层延伸至第二线路层的两个第一电源导电柱以及由第二线路层延伸至第三线路层的一第二电源导电柱。两个第一电

源导电柱以及第二电源导电柱沿着第一方向排列,且第二电源导电柱的位置是位于两个第二电源导电柱的位置之间。第一行中的每一个接地导电结构的位置与第二行中的每一个电源导电结构的位置在一第二方向上相互错开。

8.为了解决上述的技术问题,本发明所采用的另外再一技术方案是提供一种芯片封装结构,其包括芯片以及上述的封装载板。芯片具有位于其底部的多个接点,并通过多个接点设置在封装载板上,且多个接点对应于封装载板的焊垫阵列。

9.本发明的其中一有益效果在于,本发明所提供的封装载板及应用其的芯片封装结构,其能通过“第一行(或第一列)中的至少一接地导电结构包括两个第一接地导电柱以及一第二接地导电柱,两个第一接地导电柱以及第二接地导电柱沿着第一方向排列,且第二接地导电柱的位置是位于两个第一接地导电柱的位置之间”、“第二行(或第二列)中的至少一电源导电结构包括两个第一电源导电柱以及一第二电源导电柱,两个第一电源导电柱以及第二电源导电柱沿着第一方向排列,且第二电源导电柱的位置是位于两个第二电源导电柱的位置之间"以及“第一行中的每一个接地导电结构的位置与第二行中的每一个电源导电结构的位置在第二方向上相互错开”的技术方案,可最大化芯片封装结构供电路径的密度,从而提升电源完整性。

10.为使能更进一步了解本发明的特征及技术内容,请参阅以下有关本发明的详细说明与图式,然而所提供的图式仅用于提供参考与说明,并非用来对本发明加以限制。

附图说明

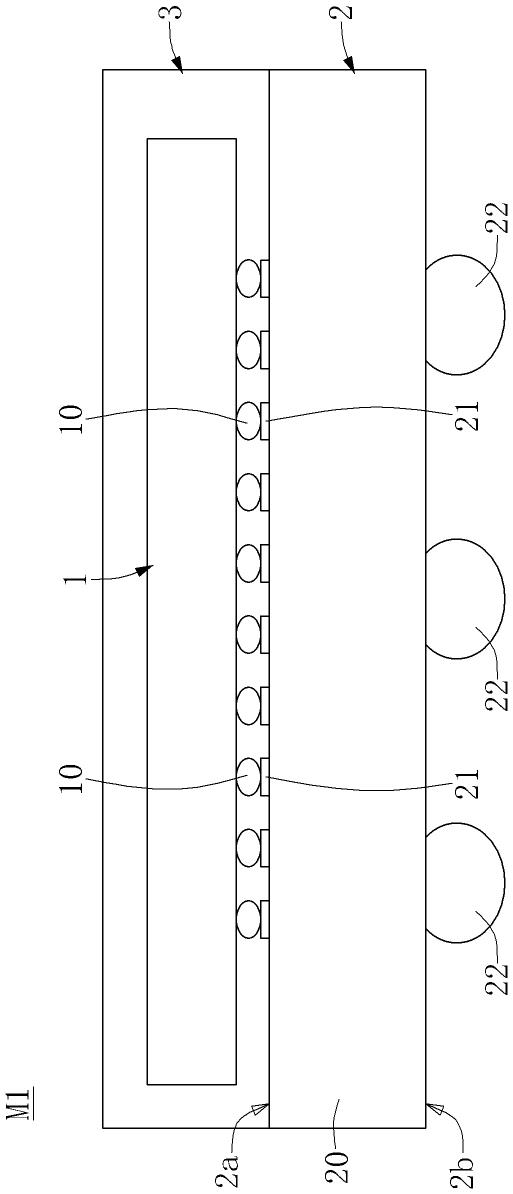

11.图1为本发明实施例的芯片封装结构的示意图。

12.图2为本发明实施例的封装载板的俯视示意图。

13.图3为图2的iii部分的局部放大示意图。

14.图4为图3的vi-vi剖面的剖面示意图。

15.图5为图3的v-v剖面的剖面示意图。

16.图6为图3的vi-vi剖面的剖面示意图。

17.图7为本发明另一实施例的封装载板的局部俯视示意图。

具体实施方式

18.以下是通过特定的具体实施例来说明本发明所公开有关“封装载板及应用其的芯片封装结构”的实施方式,本领域技术人员可由本说明书所公开的内容了解本发明的优点与效果。本发明可通过其他不同的具体实施例加以施行或应用,本说明书中的各项细节也可基于不同观点与应用,在不背离本发明的构思下进行各种修改与变更。另外,本发明的附图仅为简单示意说明,并非依实际尺寸的描绘,事先声明。以下的实施方式将进一步详细说明本发明的相关技术内容,但所公开的内容并非用以限制本发明的保护范围。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。

19.请参阅图1,其为本发明实施例的芯片封装结构的局部示意图。本实施例的芯片封装结构m1包括芯片1、封装载板2以及封装层3。芯片1设置在封装载板2上,且封装层3覆盖芯片1以及封装载板2。

20.芯片1例如是片上系统(system on chip, soc),且可适用于在高频下操作。在本发明实施例中,芯片1是以覆晶方式设置在封装载板2上。据此,芯片1具有位于其底部的多个接点10,而使芯片1可通过多个接点10设置在封装载板2上,并与封装载板2电连接。芯片1通过封装载板2内布设的电路,可电连接于另一电路板。

21.请参照图1与图2,图2为本发明实施例的封装载板的俯视示意图。本发明实施例的封装载板2具有一组装侧2a以及一底侧2b。封装载板2在组装侧2a定义出至少一芯片设置区a1。当芯片1被设置在封装载板2上时,是位于芯片设置区a1内。

22.另外,封装载板2至少包括一层压板20、一焊垫阵列21以及一球栅阵列22。焊垫阵列21与球栅阵列22分别位于层压板20的两相反侧,也就是分别位于封装载板2的组装侧2a与底侧2b。

23.请参照图3至图5,图3为图2的iii部分的局部放大示意图,图4为图3的vi-vi剖面的剖面示意图,且图5为图3的v-v剖面的剖面示意图。层压板20包括交替堆栈的多层线路层201~204与多层绝缘层(未标号)。也就是说,每两层线路层201~204之间通过绝缘层相互分隔。在本实施例中,线路层201~204共有四层,其包括第一线路层201、第二线路层202、第三线路层203以及第四线路层204。然而,本发明实施例的线路层201~204的数量并不限制于此。

24.第一线路层201与第四线路层204都位于层压板20的最外侧,且分别位于层压板20的两相反侧。进一步而言,第一线路层201是位于封装载板2的组装侧2a,而第四线路层204是位于封装载板2的底侧2b。另外,第二线路层202与第三线路层203位于层压板20内部。在本发明实施例中,第二线路层202是位于第一线路层201与第三线路层203之间,而第三线路层203是位于第二线路层202与第四线路层204之间。

25.请配合参照图2与图3,焊垫阵列21位于层压板20的组装侧2a,且电连接第一线路层201。焊垫阵列21包括多个电源焊垫组21p与多个接地焊垫组21g,且多个电源焊垫组21p与多个接地焊垫组21g是位于芯片设置区a1内的一中央区域a10。每一电源焊垫组21p包括多个电源焊垫210p,而每一接地焊垫组21g包括多个接地焊垫210g。

26.另外,如图4与图5所示,球栅阵列22是位于封装载板2的底侧2b,并电连接于第四线路层204,以使芯片封装结构m1可再组装于另一电路板上。球栅阵列22包括多个接地焊球22g以及多个电源焊球22p。

27.在本发明实施例中,本实施例的封装载板2还包括位于层压板20内的多个接地导电结构23以及多个电源导电结构24,以电连接位于层压板20两相反侧的焊垫阵列21与球栅阵列22,并形成多条供电路径。本发明实施例中,通过改善供电路径的设计,来提升芯片封装结构m1运作时的电源完整性以及电压稳定性。

28.进一步而言,焊垫阵列21中的多个电源焊垫210p是分别通过对应的多个电源导电结构24,而分别电连接至球栅阵列22中对应的电源焊球22p。相似地,焊垫阵列21中的多个接地焊垫210g是分别通过对应的多个接地导电结构23,而分别电连接至球栅阵列22中对应的接地焊球22g。然而,球栅阵列22中的电源焊球22p与接地焊球22g的配置方式并不限制于本发明所提供的实施例。

29.请参照图3,多个接地导电结构23在一第一方向d1上排成一第一行(column)。至少其中一个接地导电结构23包括两个第一接地导电柱231以及一第二接地导电柱232。须说明

的是,第一线路层201还可进一步包括多个电源迹线201p(power traces),用以使电源焊垫组21p之中的多个电源焊垫210p以及多个电源导电结构24彼此电连接,以及多个接地迹线201g(ground traces)使接地焊垫组21g中的多个接地焊垫210g以及多个接地导电结构23彼此电连接。另外,位于组装侧2a的焊垫阵列21还包括位于芯片设置区a1内的多个信号焊垫组(图未示),且信号焊垫组是位于中央区域a10之外。本发明主要是改善封装载板2内的供电路径,因此并不限制信号焊垫组的配置。

30.请参照图4,每一个第一接地导电柱231会由第一线路层201延伸至第二线路层202,而每一第二接地导电柱232会由第二线路层202延伸至第三线路层203。也就是说,每一个接地导电结构23是用以形成由多个接地焊垫组21g延伸至层压板20底侧2b的接地路径。

31.在本发明实施例中,两个第一接地导电柱231以及第二接地导电柱232是沿着第一方向d1排列,且第二接地导电柱232的位置是位于两个第一接地导电柱231的位置之间。在俯视方向上,两个第一接地导电柱231的中心连线会通过第二接地导电柱232,且大致平行于第一方向d1。在一实施例中,同一个接地导电结构23中的第一接地导电柱231的边缘会尽可能地紧邻于第二接地导电柱232的边缘,以提高封装载板2内的接地导电结构23的密度。此外,在本实施例中,每一个第二接地导电柱232的一横截面积大于每一第一接地导电柱231的一横截面积。

32.另外,请参照图3,每一个接地焊垫组21g会排列在第一行中任两相邻的第一接地导电柱231之间。因此,任两相邻的第一接地导电柱231之间会设置多个接地焊垫210g。只要接地焊垫组21g中的两相邻的接地焊垫210g之间的间距不小于预定值,可以使任两相邻的第一接地导电柱231之间所设置的接地焊垫210g的数量最大化。进一步而言,接地焊垫210g的数量可以根据两相邻的第一接地导电柱231之间的间距以及两相邻的接地焊垫210g之间的最小间距来调整。

33.须说明的是,本发明所述的“导电柱之间的间距”都是指两相邻导电柱中的其中一个导电柱中心,至另一个导电柱中心之间的直线距离。另外,本发明所述的“焊垫间距”或者“焊垫之间的间距”都是指两相邻焊垫中的其中一个焊垫中心,至另一个焊垫中心之间的直线距离。

34.另外,由于制程条件的限制,针对不同规格的封装载板2,接地焊垫210g、电源焊垫210p、第一接地导电柱231、第二接地导电柱232、第一电源导电柱241、第二电源导电柱242的尺寸以及间距有特定的要求。因此,虽然接地焊垫210g、电源焊垫210p、第一接地导电柱231、第二接地导电柱232、第一电源导电柱241、第二电源导电柱242的数量越多越能提升电源完整性,但实际上仍受限于上述特定要求。

35.请参照图4,假设第一行中任两相邻的第一接地导电柱231之间的间距为s1,每一第一接地导电柱231的直径为r1,且两个接地焊垫210g在第二方向d2之间的间距至少大于d1,则每一个接地焊垫组中,在第一方向d1上,于两相邻的第一接地导电柱231之间最多可设置的接地焊垫210g的数量为n1,则s1、r1、d1以及n1满足下列关系式:(s1-r1)/d1》n1,其中n1为正整数。

36.举例而言,在第一行中,任两相邻的第一接地导电柱231之间的间距s1约280μm,每一第一接地导电柱231的直径r1约100μm,且两个焊垫在第二方向d2之间的间距d1至少大于80μm,则每一个接地焊垫组21g中,在第二方向d2上最多可设置2个接地焊垫210g。进一步而

言,在本实施例中,每一个接地焊垫组21g中的多个接地焊垫210g排列成一2

×

2阵列,但本发明不以此为限。在其他实施例中,若两相邻的第一接地导电柱231之间的间距增加,每一接地焊垫组21g的接地焊垫210g的数量也可以增加。

37.请参照图3,其中一个接地焊垫组21g是位于两相邻的接地导电结构23之间,且在层压板20的厚度方向上与第二接地导电柱232完全不重叠。另一个接地焊垫组21g的多个接地焊垫210g则在厚度方向上至少部分重叠于第二接地导电柱232。

38.请参照图3与图5,相似地,多个电源导电结构24在第一方向d1上排成一第二行。至少一电源导电结构24包括两个第一电源导电柱241以及一第二电源导电柱242。每一个第一电源导电柱241是由第一线路层201延伸至第二线路层202,而每一第二电源导电柱242是由第二线路层202延伸至第三线路层203。在本实施例中,两个第一电源导电柱241以及第一电源导电柱241也是沿着第一方向d1排列,且第二电源导电柱242的位置是位于两个第一电源导电柱241之间。

39.也就是说,在俯视方向上,两个第一电源导电柱241的中心连线会通过第二电源导电柱242,且大致平行于第一方向d1。此外,每一第二电源导电柱242的一横截面积大于每一第一电源导电柱241的一横截面积。在一实施例中,同一个电源导电结构24中的第一电源导电柱241的边缘会尽可能地紧邻于第二电源导电柱242的边缘,以提高封装载板2内的电源导电结构24的密度。

40.请参照图3,在本实施例中,第一行中的每一个接地导电结构23的位置,与第二行中的每一个电源导电结构24的位置会在第二方向d2上相互错开。也就是说,位置最靠近的两个接地导电结构23以及电源导电结构24并不会沿着第二方向d2相互对齐。详细而言,在本实施例中,位置最靠近的第一接地导电柱231与第一电源导电柱241会在第二方向d2上相互对齐。然而,第二接地导电柱232的中心点与最靠近其的第二电源导电柱242的中心点的连线会与第一方向d1之间不平行而形成一夹角。 在一实施例中,第二电源导电柱242的边缘与最靠近的第二接地导电柱232的边缘之间的最短距离至少35μm,且第一行与第二行之间的行距h为至少160μm。

41.请参照图3,每一个电源焊垫组21p会排列在第二行中任两相邻的第一电源导电柱241之间。也就是说,只要两相邻的电源焊垫210p之间的间距不小于预定值,可以使任两相邻的第一电源导电柱241之间所设置的电源焊垫210p的数量最大化。进一步而言,电源焊垫210p的数量可以根据两相邻的第一电源导电柱241之间的间距以及两相邻的电源焊垫210p之间的最小间距来调整。

42.请参照图3,假设第二行中任两相邻的第一电源导电柱241之间的间距为s2,每一第一电源导电柱241的直径为r2,且两个电源焊垫210p之间在第一方向d1上的间距至少大于d2,则每一个电源焊垫组中,在第一方向d1上,于两相邻的第一电源导电柱241之间最多可设置的电源焊垫210p的数量为n2,则s2、r2、d2以及n2满足下列关系式:(s2-r2)/d2》n2,其中n2为正整数。

43.在本实施例中,每一个电源焊垫组21p的多个电源焊垫210p排列成一2

×

2阵列,但本发明不以此为限。在其他实施例中,若两相邻的第一电源导电柱241之间的间距增加,每一电源焊垫组21p的电源焊垫210p的数量也可以增加。

44.请参照图3与图5,其中一个电源焊垫组21p是位于两相邻的电源导电结构24之间,

且在层压板20的厚度方向上与第二电源导电柱242完全不重叠。另一个电源焊垫组21p的多个电源焊垫210p则在厚度方向上至少部分重叠于第二电源导电柱242。

45.通过上述配置方式,针对不同规格的封装载板2,接地焊垫210g、电源焊垫210p、多个接地导电结构23与多个电源导电结构24的设置既可符合特定条件,又能形成密度较高的供电路径。

46.请参照图3与图6,其中图6为图3的vi-vi剖面的剖面示意图。在本实施例中,多个接地焊垫组21g会与多个电源焊垫组21p是沿着第二方向d2交替排列成多列。如图6所示,在第二方向d2上,多个接地焊垫210g会与多个电源焊垫210p交替排成至少一列(row)。详细而言,在每一列中,每两个接地焊垫210g与每两个电源焊垫210p交替排列。也就是说,每两个接地焊垫210g之间设置两个电源焊垫210p,且每两个电源焊垫210p之间会设置两个接地焊垫210g,但本发明不以此例为限。在其他实施例中,在每一列中,也可以是每三个接地焊垫210g与每三个电源焊垫210p交替排列。

47.另外,请参照图3,同一个接地焊垫组21g中的两个接地焊垫210g之间的间距d1,会小于分别属于两相邻的接地焊垫组21g中的两个最靠近的接地焊垫210g之间的间距d1’。相似地,同一个电源焊垫组21p中的两个电源焊垫210p之间的间距d2,会小于分别属于两相邻的电源焊垫组21p中的两个最靠近的电源焊垫210p之间的间距d2’。

48.在本发明中,多个接地导电结构23与多个电源导电结构24相互交错设置,可以使对应的电源焊垫组21p、电源导电结构24、接地焊垫组21g以及接地导电结构23所形成的电流回路(current loop)的面积缩减,从而大幅减少寄生电感。由于寄生电感降低,可以进一步减少因为寄生电感以及电流瞬时变化过大而产生的电压变化,从而提升电源完整性(power integrity)。

49.值得一提的是,利用本发明实施例电源焊垫组21p、接地焊垫组21g、电源导电结构24与接地导电结构23的配置方式,可以最大化接地焊垫210g、电源焊垫210p、第一电源导电柱241、第二电源导电柱242、第一接地导电柱231与第二接地导电柱232的密度。因此,当芯片通过封装载板2而电连接至另一电路板运作,封装载板2可对于芯片内部的任意组件提供相对较短的供电路径,从而降低阻抗。

50.参阅图7,显示本发明另一实施例的封装载板的局部俯视示意图。在图7的实施例中,与图3的实施例相同或相似的组件具有相同的标号,且相同的部分不再赘述。另外,图7的封装载板2’省略第一线路层201。

51.本实施例的封装载板2’的多个接地导电结构23是在第二方向d2上排成一第一列,而多个电源导电结构24是在第二方向d2上排成一第二列。第一列中的每一接地导电结构23的位置与第二列中的每一电源导电结构24的位置在第一方向d1相互错开。详细而言,最靠近的第二接地导电柱232与第二电源导电柱242的中心点连线与第一方向d1不平行而形成夹角。

52.与前一实施例相似,在俯视方向上,每一个接地焊垫组21g会排列在第一列中任两相邻的第一接地导电柱231之间,而每一个电源焊垫组21p会排列在第二列中任两相邻的第一电源导电柱241之间。

53.在第一列中,任两相邻的第一接地导电柱231之间的间距较大,因此在任两相邻的第一接地导电柱231之间的接地焊垫组21g可具有更多接地焊垫210g。据此,只要任两个焊

垫(如:两个接地焊垫210g、两个电源焊垫210p或者接地焊垫210g与电源焊垫210p)在第一方向d1(或者第二方向)之间的间距符合封装载板2的规范,接地焊垫组21g中的接地焊垫210g的数量以及电源焊垫组21p中的电源焊垫210p的数量在本发明中并不限制。

54.在第一列中,假设任两相邻的第一接地导电柱231之间的在第二方向d2的间距为s1’,每一第一接地导电柱231的直径为r1,且两个接地焊垫210g在第二方向d2之间的间距至少大于d1”,则每一个接地焊垫组中,在第二方向d2上最多可设置的接地焊垫210g的数量为n1,则s1’、r1、d1’以及n1满足下列关系式:(s1

’‑

r1)/d1”》n1,其中n1为正整数。

55.举例而言,在第一列中,任两相邻的第一接地导电柱231之间的间距s1’约450μm,每一第一接地导电柱231的直径r1约100μm,且两个焊垫在第二方向d2之间的间距d1”至少大于80μm,则每一个接地焊垫组21g中,在第二方向d2上最多可设置4个接地焊垫210g。

56.如图7所示,每一个接地焊垫组21g的多个接地焊垫210g可排列成一4

×

3阵列,但本发明不以此为限。相似地,在第二列中,每一个电源焊垫组21p的多个电源焊垫210p可在任两相邻的第一电源导电柱241之间排列成一4

×

3阵列。

57.另外,值得注意的是,虽然本实施例的第二接地导电柱232的直径与图2的实施例中的第二接地导电柱232的直径不同,但通过使多个接地导电结构23与多个电源导电结构交错排列,再将接地焊垫组21g设置在任两相邻的第一接地导电柱231之间以及将电源焊垫组21p设置在两相邻的第一电源导电柱241之间,即可最大化供电路径的密度,从而提升芯片封装结构m1运作时的电源完整性。

[0058] [实施例的有益效果]本发明的其中一有益效果在于,本发明所提供的封装载板2(2’)及应用其的芯片封装结构m1,其能通过“第一行(或第一列)中的至少一接地导电结构23包括两个第一接地导电柱231以及一第二接地导电柱232,两个第一接地导电柱231以及第二接地导电柱232沿着第一方向d1排列,且第二接地导电柱232的位置是位于两个第一接地导电柱231的位置之间”、“第二行(或第二列)中的至少一电源导电结构24包括两个第一电源导电柱241以及一第二电源导电柱242,两个第一电源导电柱241以及第二电源导电柱242沿着第一方向d1排列,且第二电源导电柱242的位置是位于两个第二电源导电柱242的位置之间"以及“第一行中的每一个接地导电结构23的位置与第二行中的每一个电源导电结构24的位置在第二方向d2上相互错开”的技术方案,可最大化芯片封装结构m1供电路径的密度,从而提升电源完整性。

[0059]

更进一步来说,每一接地焊垫组21g排列在第一行中任两相邻的第一接地导电柱231之间,且每一电源焊垫组21p排列在第二行中任两相邻的第一电源导电柱241之间,还可以最大化接地焊垫210g以及电源焊垫210p的数量,而提高接地焊垫210g与电源焊垫210p的分布密度。

[0060]

以上所公开的内容仅为本发明的优选可行实施例,并非因此局限本发明的申请专利范围,所以凡是运用本发明说明书及图式内容所做的等效技术变化,均包含于本发明的申请专利范围内。

[0061]

符号说明m1:芯片封装结构1:芯片

10:接点2, 2’:封装载板2a:组装侧2b:底侧a1:芯片设置区a10:中央区域20:层压板201:第一线路层201p:电源迹线201g:接地迹线202:第二线路层203:第三线路层204:第四线路层21:焊垫阵列21g:接地焊垫组210g:接地焊垫21p:电源焊垫组210p:电源焊垫22:球栅阵列22g:接地焊球22p:电源焊球23:接地导电结构231:第一接地导电柱232:第二接地导电柱24:电源导电结构241:第一电源导电柱242:第二电源导电柱3:封装层d1:第一方向d2:第二方向h:行距s1,s1’:第一接地导电柱间距s2:第一电源导电柱间距d1, d1’, d1”:接地焊垫间距d2, d2’:电源焊垫间距r1:第一接地导电柱直径r2:第一电源导电柱直径

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1