显示装置的制作方法

1.实施例针对一种显示装置。更具体地,实施例针对一种包括屏蔽图案的显示装置。

背景技术:

2.到目前为止,传统的阴极射线管(crt)已经在就性能和价格而言具有许多优点的显示装置中广泛使用。然而,具有诸如小型化或克服crt的缺点的便携性的优点并且具有诸如小型化、重量减小和低功耗的优点的显示装置已经引起了关注。例如,等离子体显示器、液晶显示器、有机发光显示器等正在引起关注。

3.已经尝试减小显示装置的边框区域。例如,已经开发了无边框显示装置、包括凹口的显示装置等。存在于边框区域中的布线可以被重新设置以减小边框区域。

技术实现要素:

4.实施例提供了一种包括屏蔽图案的显示装置。

5.根据示例实施例,一种显示装置包括:显示面板;驱动电路,该驱动电路将驱动信号提供到显示面板并且包括至少一个驱动晶体管;以及时钟信号布线,该时钟信号布线将时钟信号提供到驱动电路。驱动电路包括有源图案、栅图案、源图案和屏蔽图案,栅图案在平面图中与有源图案重叠,源图案的主表面平面被布置在与其中布置有有源图案的层不同的层中,源图案电连接到有源图案,屏蔽图案被布置在栅图案与时钟信号布线之间并且被施加有恒定电压,并且时钟信号布线在平面图中与栅图案重叠并且被布置在源图案上。

6.在实施例中,屏蔽图案可以被布置在源图案的主表面平面下。

7.在实施例中,屏蔽图案在平面图中可以和栅图案与时钟信号布线重叠的整个区域完全重叠。

8.在实施例中,显示装置可以进一步包括:连接布线,该连接布线与时钟信号布线被布置在同一层中,并且该连接布线将恒定电压传输到屏蔽图案。

9.在实施例中,显示装置可以进一步包括:连接布线,该连接布线被布置在屏蔽图案与时钟信号布线之间,并且该连接布线将恒定电压传输到屏蔽图案。

10.在实施例中,连接布线在平面图中可以不与时钟信号布线和栅图案中的每一个重叠。

11.在实施例中,栅图案可以包括第一子栅图案和第二子栅图案。

12.在实施例中,第一子栅图案和第二子栅图案可以被布置在源图案的主表面平面下。

13.在实施例中,第一子栅图案和第二子栅图案在平面图中可以与屏蔽图案重叠。

14.在实施例中,第一子栅图案和第二子栅图案中的仅一个在平面图中可以与屏蔽图案重叠。

15.在实施例中,第一子栅图案和第二子栅图案可以被布置在同一层中。

16.在实施例中,驱动电路可以进一步包括:被布置在第一子栅图案与第二子栅图案

之间并且电连接到有源图案的漏图案。

17.在实施例中,第一子栅图案和第二子栅图案中的仅一个在平面图中可以与屏蔽图案重叠。

18.在实施例中,屏蔽图案可以包括第一子屏蔽图案和第二子屏蔽图案。

19.在实施例中,第一子栅图案和第二子栅图案在平面图中可以分别与第一子屏蔽图案和第二子屏蔽图案重叠。

20.在实施例中,屏蔽图案可以被布置在源图案上。

21.在实施例中,驱动电路可以包括p型晶体管。

22.在实施例中,驱动电路可以包括n型晶体管。

23.在实施例中,驱动电路可以包括双栅晶体管。

24.根据实施例的显示装置可以包括:显示面板、将驱动信号提供到显示面板并且包括至少一个驱动晶体管的驱动电路以及用于将时钟信号提供到驱动电路的时钟信号布线,驱动电路包括有源图案、与有源图案重叠的栅图案、与有源图案被布置在不同的层中并且电连接到有源图案的源图案以及被布置在栅图案与被施加有恒定电压的时钟信号布线之间的屏蔽图案,并且时钟信号布线与栅图案重叠并且被设置在源图案上。因此,可以减小显示装置的边框区域。此外,可以有效地防止可能在栅图案与时钟信号布线之间发生的耦合现象。

25.要理解,前面的一般描述和下面的详细描述两者都是示例性和说明性的,并且旨在提供对所要求保护的本发明的进一步说明。

附图说明

26.通过以下结合附图的详细描述,将更清楚地理解本发明的实施例的各方面。

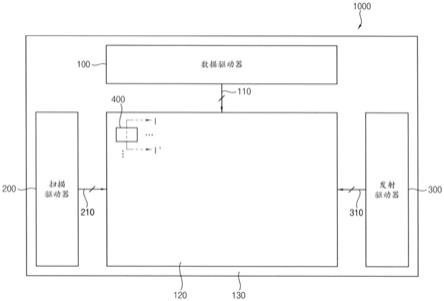

27.图1是图示根据本发明的实施例的显示装置的平面图。

28.图2是图示扫描驱动器的结构的实施例的示意图。

29.图3是图示内置在扫描移位寄存器中的扫描驱动电路的实施例的示意图。

30.图4是图示发射驱动器的结构的实施例的示意图。

31.图5是图示内置在发射移位寄存器中的发射驱动电路的实施例的示意图。

32.图6是沿图1的线i

‑

i’截取的截面图。

33.图7是图示驱动晶体管的实施例的平面图。

34.图8是沿图7的线ii

‑

ii’截取的截面图。

35.图9是图示驱动晶体管的另一实施例的平面图。

36.图10是沿图9的线iii

‑

iii’截取的截面图。

37.图11是图示驱动晶体管的又一实施例的平面图。

38.图12是沿图11的线iv

‑

iv’截取的截面图。

39.图13是图示驱动电路双栅晶体管的又一实施例的平面图。

40.图14是沿图13的线v

‑

v’截取的截面图。

41.图15是图示驱动电路双栅晶体管的另一实施例的平面图。

42.图16是沿图15的线vi

‑

vi’截取的截面图。

43.图17是图示驱动电路双栅晶体管的又一实施例的平面图。

44.图18是沿图17的线vii

‑

vii’截取的截面图。

45.图19是图示驱动电路双栅晶体管的又一实施例的平面图。

46.图20是沿图19的线viii

‑

viii’截取的截面图。

47.图21是图示驱动晶体管的另一实施例的平面图。

48.图22是沿图21的线ix

‑

ix’截取的截面图。

具体实施方式

49.在下文中,将参考其中示出了实施例的附图来描述根据本发明的实施例的显示装置。相同或相似的附图标记可以用于附图中的相同或相似的元件。

50.本发明可以具有各种修改并且可以以不同的形式体现,并且将参考附图详细地说明实施例。然而,本发明可以以不同的形式体现,并且不应被解释为限于本文所阐述的实施例。相反,应该包括本发明的精神和技术范围中包括的所有修改、等同物和替代物。

51.在附图中,为了图示的清楚,夸大了结构的尺寸。将理解,尽管术语“第一”、“第二”等在本文中可以用于描述各种元件,但是这些元件不应受这些术语的限制。这些术语仅用于将一个元件与另一元件区分开。因此,在不脱离本发明的教导的情况下,第一元件可以被称作第二元件。类似地,第二元件可以被称作第一元件。如本文所使用的,单数形式旨在也包括复数形式,除非上下文另外明确指示。

52.将理解,尽管术语“第一”、“第二”、“第三”等在本文中可以用于描述各种元件、组件、区域、层和/或部分,但是这些元件、组件、区域、层和/或部分不应受这些术语限制。这些术语仅用于将一个元件、组件、区域、层或部分与另一元件、组件、区域、层或部分区分开。因此,在不脱离本文的教导的情况下,下面讨论的第一元件、组件、区域、层或部分可以被称作第二元件、组件、区域、层或部分。本文使用的术语仅是为了描述特定实施例的目的,而不旨在限制。如本文所使用的,单数形式“一”和“该”旨在包括包含“至少一个”的复数形式,除非上下文另外明确指示。在说明书和权利要求书中,为了其含义和解释的目的,术语“和/或”旨在包括术语“和”和“或”的任何组合。例如,“a和/或b”可以被理解为意味着“a、b或者a和b”。术语“和”和“或”可以在结合或分离的含义下使用,并且可以被理解为等同于“和/或”。

53.为了其含义和解释的目的,短语

“…

中的至少一个”旨在包括“从

…

的组中选择的至少一个”的含义。例如,“a和b中的至少一个”可以被理解为意味着“a、b或者a和b”。当在元件列表之后时,术语

“…

中的至少一个”修饰整个元件列表而不修饰该列表中的个别元件。

54.将进一步理解,当在本说明书中使用时,术语“包括”和/或“包含”指定所述特征、数字、步骤、操作、元件、部件或其组合的存在,但不排除一个或多个其它特征、数字、步骤、操作、元件、部件或其组合的存在或添加。

55.还将理解,当层、膜、区域、板等被称为在另一部件“上”或“上方”时,它可以“直接”在该另一部件“上”或者也可以存在中间层。还将理解,当层、膜、区域、板等被称为在另一部件“下”或“下方”时,它可以“直接”在该另一部件“下”或者也可以存在中间层。当元件被称为被布置在另一元件“上”时,它可以被布置在该另一元件下。

56.为了便于描述,空间相对术语“下方”、“下面”、“下部”、“上方”、“上部”等在本文中可以用于描述如附图中所图示的一个元件或组件与另一元件或组件之间的关系。将理解,除了附图中所描绘的定向之外,空间相对术语旨在包括设备在使用或操作中的不同定向。

例如,在附图中图示的设备被翻转的情况下,位于另一设备“下方”或“下面”的设备可以被放置在另一设备“上方”。因此,说明性术语“下方”可以包括下部位置和上部位置两者。设备也可以定向在其他方向上,并且因此,空间相对术语可以取决于定向而被不同地解释。

57.除非另外定义,否则在本文中使用的所有术语(包括技术术语和科学术语)具有与本公开所属领域的技术人员通常理解的含义相同的含义。将进一步理解,诸如在常用字典中定义的那些术语应被解释为具有与它们在相关领域的上下文中的含义一致的含义,并且将不以理想化或过度正式的含义来解释,除非在说明书中明确定义。

58.图1是图示根据本发明的实施例的显示装置的平面图,图2是图示扫描驱动器的结构的实施例的示意图(图2是平面图),图3是图示内置在扫描移位寄存器中的扫描驱动电路的实施例的示意图,图4是图示发射驱动器的结构的实施例的示意图(图4是平面图),图5是图示内置在发射移位寄存器中的发射驱动电路的实施例的示意图,并且图6是沿图1的线i

‑

i’截取的截面图。

59.参考图1至图6,显示装置1000可以包括包含多个像素400的显示面板120和用于驱动显示面板120的驱动电路130。驱动电路130可以包括将数据信号110提供到多个像素400的数据驱动器100、将扫描信号210提供到多个像素400的扫描驱动器200和将发射信号310提供到多个像素400的发射驱动器300。

60.显示面板120可以包括连接到多条数据布线和多条扫描布线的多个像素400。像素400可以被以矩阵形式设置在显示面板120的整个区域之上。然而,这是示例性的,并且其中像素400根据本发明被设置的设置不限于此。每个像素400可以包括至少两个晶体管、至少一个电容器和有机发光二极管580。显示面板120可以是有机发光显示面板。像素400可以是适合于低频驱动以降低功耗的混合氧化物多晶(hop)像素。hop像素可以包括至少一个低温多晶硅(ltps)pmos晶体管和至少一个氧化物nmos晶体管。然而,这是示例性的,并且本发明不限于此。

61.在图1中,图示了扫描驱动器200和发射驱动器300分别位于显示面板120的两侧,但是这是示例性的,并且本发明不限于此。在另一实施例中,例如,可以改变扫描驱动器200和发射驱动器300的位置。另外,扫描驱动器200和发射驱动器300两者都可以被定位在显示面板120的同一侧。

62.如图2中所图示,扫描驱动器200可以包括多个扫描移位寄存器220和连接到多个扫描移位寄存器220的多条时钟信号布线clk。在实施例中,多条时钟信号布线clk在平面图中可以被布置为与扫描移位寄存器220重叠。当多条时钟信号布线clk在平面图中被布置为与多个扫描移位寄存器220重叠时,可以减小显示装置1000的边框区域。

63.扫描移位寄存器220可以包括扫描驱动电路10。在实施例中,扫描驱动电路10可以包括第一扫描驱动晶体管t1至第八扫描驱动晶体管t8以及第一电容器c1和第二电容器c2。耦合现象可能发生在未直接施加有作为栅导通信号的多个时钟信号clk1和clk2并且未直接施加有作为栅导通信号的恒定电压(即,第一恒定电压vgh、第二恒定电压vgl)的一些扫描驱动晶体管t2、t4、t6和t7中。当耦合现象发生时,故障可能发生在扫描输出中。结果,显示装置1000的性能可能劣化。在图3中的扫描驱动电路10中,时钟信号clk1作为栅导通信号被施加到第三扫描驱动晶体管t3,时钟信号clk2作为栅导通信号被施加到第一扫描驱动晶体管t1和第五扫描驱动晶体管t5,第二恒定电压vgl可以作为栅导通信号被施加到第八扫

描驱动晶体管t8,并且输出信号scan与第n扫描移位寄存器220的输出信号out<n>相对应。这里,n是自然数。输出信号out<n

‑

1>至out<n+2>分别与第n

‑

1扫描移位寄存器220至第n+2扫描移位寄存器220的输出信号相对应。

64.图3的扫描驱动电路10被图示为包括p型晶体管,但是本发明不限于此。在另一实施例中,扫描驱动电路10可以包括n型晶体管。

65.如图4中所图示,发射驱动器300可以包括多个发射移位寄存器320和连接到多个发射移位寄存器320的多条时钟信号布线clk。在实施例中,多条时钟信号布线clk在平面图中可以被布置为与多个发射移位寄存器320重叠。当多条时钟信号布线clk在平面图中被布置为与多个发射移位寄存器320重叠时,可以减小显示装置1000的边框区域。

66.发射移位寄存器320可以包括发射驱动电路20。在实施例中,发射驱动电路20可以包括第九发射驱动晶体管t9至第二十发射驱动晶体管t20以及第三电容器至第五电容器c3、c4、c5。耦合现象可能发生在未直接施加有作为栅导通信号的多个时钟信号clk1和clk3并且未直接施加有作为栅导通信号的恒定电压(即,第一恒定电压vgh、第二恒定电压vgl)的一些发射驱动晶体管t9、t10、t13、t14、t17、t18、t20中。在图5中的发射驱动电路20中,时钟信号clk1可以作为栅导通信号被施加到第十五发射驱动晶体管t15和第十九发射驱动晶体管t19,时钟信号clk3可以作为栅导通信号被施加到第十六发射驱动晶体管t16,第二恒定电压vgl可以作为栅导通信号被施加到第十一发射驱动晶体管t11和第十二发射驱动晶体管t12,并且输出信号em与第n发射移位寄存器320的输出信号out1<n>相对应。输出信号out1<n

‑

1>至out1<n+2>分别与第n

‑

1发射移位寄存器320至第n+2发射移位寄存器320的输出信号相对应。

67.图5的发射驱动电路20被图示为包括p型晶体管,但是本发明不限于此。在另一实施例中,发射驱动电路20可以包括n型晶体管。

68.如图6中所图示,显示面板120可以包括基板510、缓冲层515、栅绝缘层520、显示面板晶体管598、第一层间绝缘层530、第二层间绝缘层535、电容电极536、第一通孔绝缘层540、连接电极556、第二通孔绝缘层550、像素限定层560和有机发光二极管580。显示面板晶体管598可以包括有源图案591、源图案594、漏图案595和栅图案596。有机发光二极管580可以包括下电极555、中间层565和上电极570。

69.基板510可以包括诸如石英、合成石英、氟化钙、掺氟石英、钠钙玻璃、无碱玻璃、聚对苯二甲酸乙二醇酯(pet)、聚萘二甲酸乙二醇酯(pen)、聚酰亚胺等的各种材料,或者由其形成。

70.缓冲层515可以被布置在基板510上。缓冲层515可以防止金属原子或杂质从基板510扩散到像素400。缓冲层515可以通过在用于形成有源图案591的结晶工艺期间控制热传递速率来获得基本均匀的有源图案591。另外,当基板510的顶表面不均匀时,缓冲层515可以用于改善基板510的顶表面的平坦度。两个或更多个缓冲层515可以根据基板510的类型被提供在基板510上。可替代地,缓冲层515可以不被布置在基板510上。也就是说,可以省略缓冲层515。在实施例中,缓冲层515可以包括有机材料或无机材料。例如,缓冲层515可以具有包括诸如氧化硅、氮化硅或氮氧化硅的无机绝缘材料或者由诸如氧化硅、氮化硅或氮氧化硅的无机绝缘材料形成的单层或多层结构。

71.有源图案591可以被布置在缓冲层515上。有源图案591可以包括金属氧化物半导

体、无机半导体或有机半导体等。有源图案591可以包括沟道区、源区和漏区。

72.栅绝缘层520可以被布置在缓冲层515上。栅绝缘层520可以覆盖缓冲层515上的有源图案591,并且具有平坦的顶表面而不会在有源图案591周围形成台阶。可选地,栅绝缘层520可以被布置在缓冲层515上,以沿有源图案591的轮廓具有基本相同的厚度。栅绝缘层520可以包括硅化合物、金属氧化物等。例如,栅绝缘层520可以包括氧化硅(sio)、氮化硅(sin)、氮氧化硅(sion)、碳氧化硅(sioc)、碳氮化硅(sicn)、氧化铝(alo)、氮化铝(aln)、氧化钽(tao)、氧化铪(hfo)、氧化锆(zro)、氧化钛(tio)等。在实施例中,栅绝缘层520可以具有包括多个绝缘层的多层结构。绝缘层可以具有不同的材料和不同的厚度。这些可以单独使用或彼此结合使用。

73.栅图案596可以被布置在栅绝缘层520上。栅图案596可以被布置在栅绝缘层520的有源图案591位于其下方的一部分上。栅图案596可以包括金属、合金、金属氮化物、导电金属氧化物、透明导电材料等。例如,栅图案596可以由铝(al)、铂(pt)、钯(pd)、银(ag)、镁(mg)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、钙(ca)、钼(mo)、钛(ti)、钨(w)和铜(cu)中的一种或多种材料形成,并且可以形成为单层或多层。

74.第一层间绝缘层530可以被布置在栅绝缘层520上。第一层间绝缘层530可以覆盖栅绝缘层520上的栅图案596,并且可以具有平坦的顶表面而不会在栅绝缘层520周围形成台阶。可选地,第一层间绝缘层530可以被布置在栅绝缘层520上,以沿栅图案596的轮廓具有基本相同的厚度。第一层间绝缘层530可以包括硅化合物、金属氧化物等。例如,第一层间绝缘层530可以包括氧化硅(sio)、氮化硅(sin)、氮氧化硅(sion)、碳氧化硅(sioc)、碳氮化硅(sicn)、氧化铝(alo)、氮化铝(aln)、氧化钽(tao)、氧化铪(hfo)、氧化锆(zro)、氧化钛(tio)等。在实施例中,第一层间绝缘层530可以具有包括多个绝缘层的多层结构。绝缘层可以具有不同的材料和不同的厚度。这些可以单独使用或彼此结合使用。

75.电容电极536可以被布置在第一层间绝缘层530上。电容电极536可以被布置在第一层间绝缘层530的栅图案596位于其下方的一部分上。电容电极536可以包括金属、合金、金属氮化物、导电金属氧化物、透明导电材料等。例如,电容电极536可以包括铝(al)、铂(pt)、钯(pd)、银(ag)、镁(mg)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、钙(ca)、钼(mo)、钛(ti)、钨(w)和铜(cu)中的一种或多种材料或者由其形成,并且可以形成为单层或多层。

76.第二层间绝缘层535可以覆盖第一层间绝缘层530上的电容电极536,并且可以具有平坦的顶表面而不会在电容电极536周围形成台阶。可选地,第二层间绝缘层535可以被布置在第一层间绝缘层530上,以沿电容电极536的轮廓具有基本相同的厚度。第二层间绝缘层535可以包括硅化合物、金属氧化物等。例如,第二层间绝缘层535可以包括氧化硅(sio)、氮化硅(sin)、氮氧化硅(sion)、碳氧化硅(sioc)、碳氮化硅(sicn)、氧化铝(alo)、氮化铝(aln)、氧化钽(tao)、氧化铪(hfo)、氧化锆(zro)、氧化钛(tio)等。在实施例中,第二层间绝缘层535可以具有包括多个绝缘层的多层结构。绝缘层可以具有不同的材料和不同的厚度。这些可以单独使用或彼此结合使用。

77.源图案594和漏图案595可以被布置在第二层间绝缘层535上。源图案594可以通过穿过第一层间绝缘层530、第二层间绝缘层535和栅绝缘层520的接触孔连接到有源图案591的源区。在实施例中,源图案594和有源图案591的源区可以构成源电极。漏图案595可以通过穿过第一层间绝缘层530、第二层间绝缘层535和栅绝缘层520的接触孔连接到有源图案

591的漏区。在实施例中,漏图案595和有源图案591的漏区可以构成漏电极。源图案594和漏图案595可以包括金属、合金、金属氮化物、导电金属氧化物、透明导电材料等。例如,源图案594和漏图案595可以包括铝(al)、铂(pt)、钯(pd)、银(ag)、镁(mg)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、钙(ca)、钼(mo)、钛(ti)、钨(w)和铜(cu)中的一种或多种材料或者由其形成,并且可以形成为单层或多层。

78.第一通孔绝缘层540可以被布置在第二层间绝缘层535上,并且可以覆盖源图案594和漏图案595。第一通孔绝缘层540可以被布置为具有相对厚的厚度以充分覆盖源图案594和漏图案595,并且在这种情况下,第一通孔绝缘层540可以具有基本平坦的顶表面。为了实现第一通孔绝缘层540的这种平坦的顶表面,平坦化工艺可以被添加到第一通孔绝缘层540。可选地,第一通孔绝缘层540可以覆盖源图案594和漏图案595,并且可以沿源图案594和漏图案595的轮廓被以均匀的厚度布置。第一通孔绝缘层540可以由有机材料或无机材料制成。在实施例中,第一通孔绝缘层540可以由诸如丙烯酸、苯并环丁烯(bcb)、聚酰亚胺或六甲基二硅氧烷(hmdso)的有机材料形成。

79.连接电极556可以被布置在第一通孔绝缘层540上。连接电极556可以通过穿过第一通孔绝缘层540的接触孔连接到源图案594或漏图案595。连接电极556可以包括金属、合金、金属氮化物、导电金属氧化物、透明导电材料等。例如,连接电极556可以由铝(al)、铂(pt)、钯(pd)、银(ag)、镁(mg)、金(au)、镍(ni)、钕(nd)、铱(ir)、铬(cr)、钙(ca)、钼(mo)、钛(ti)、钨(w)和铜(cu)中的一种或多种材料形成,并且可以形成为单层或多层。

80.第二通孔绝缘层550可以被布置在第一通孔绝缘层540上并且可以覆盖连接电极556。第二通孔绝缘层550可以被布置为具有相对厚的厚度以充分覆盖连接电极556,并且在这种情况下,第二通孔绝缘层550可以具有基本平坦的顶表面。为了实现第二通孔绝缘层550的这种平坦的顶表面,平坦化工艺可以被添加到第二通孔绝缘层550。可选地,第二通孔绝缘层550可以覆盖连接电极556,并且可以沿连接电极556的轮廓被以均匀的厚度布置。第二通孔绝缘层550可以由有机材料或无机材料制成。在实施例中,第二通孔绝缘层550可以包括与第一通孔绝缘层540基本相同或相似的材料。

81.下电极555可以被布置在第二通孔绝缘层550上。下电极555可以包括透明电极、反射电极或透反射电极。下电极555可以通过穿过第二通孔绝缘层550的接触孔连接到连接电极556。在实施例中,下电极555可以是阳电极和阴电极中的一个。

82.暴露下电极555的上表面的一部分的像素限定层560可以被布置在第二通孔绝缘层550上。像素限定层560可以包括有机材料。

83.中间层565可以被布置在其中上表面的一部分被像素限定层560暴露的下电极555上。中间层565可以具有其中空穴注入层、空穴传输层、发光层、电子传输层、电子注入层等以单个或复杂结构堆叠的结构。

84.上电极570可以被布置在中间层565上。上电极570可以包括半透明电极或反射电极。在一个实施例中,上电极570可以是阴电极和阳电极中的一个。

85.图7是图示驱动晶体管的实施例的平面图,并且图8是沿图7的线ii

‑

ii’截取的截面图。

86.参考图7和图8,图7的晶体管可以是被布置在图1的扫描驱动器200或发射驱动器300中的晶体管。图7的晶体管可以与图3的扫描驱动电路10和图5的发射驱动电路20中的晶

体管之中的未直接施加有作为导通信号的时钟信号并且未直接施加有作为导通信号的恒定电压(例如,第一恒定电压vgh、第二恒定电压vgl)的晶体管相对应。在实施例中,图7的晶体管可以与图3的第二扫描驱动晶体管t2、第四扫描驱动晶体管t4、第六扫描驱动晶体管t6和第七扫描驱动晶体管t7中的一个相对应。在实施例中,图7的晶体管可以与图5的第九发射驱动晶体管t9、第十发射驱动晶体管t10、第十三发射驱动晶体管t13、第十四发射驱动晶体管t14、第十七发射驱动晶体管t17、第十八发射驱动晶体管t18和第二十发射驱动晶体管t20中的一个相对应。这对于图9、图11、图13、图15、图17、图19和图21的晶体管来说可以是相同的。

87.驱动电路130可以包括基板510、缓冲层515、栅绝缘层520、驱动晶体管528a、第一层间绝缘层530、第二层间绝缘层535、第一通孔绝缘层540、第二通孔绝缘层550、屏蔽图案527和时钟信号布线545。驱动晶体管528a可以包括有源图案521、源图案524、漏图案525和栅图案526。在实施例中,源图案524和有源图案521的源区可以构成源电极,并且漏图案525和有源图案521的漏区可以构成漏电极。

88.第二层间绝缘层535可以覆盖被布置在第一层间绝缘层530上的屏蔽图案527,并且可以具有平坦的顶表面而不会在其周围形成台阶。可选地,第二层间绝缘层535可以被布置在第一层间绝缘层530上,以沿屏蔽图案527的轮廓具有基本相同的厚度。

89.时钟信号布线545可以被布置在第一通孔绝缘层540上。时钟信号可以通过时钟信号布线545被供应到图2的扫描移位寄存器220和图4的发射移位寄存器320。在实施例中,时钟信号布线545可以与图6的连接电极556被布置在同一层中。时钟信号布线545可以由与图6的连接电极556相同的材料同时形成。在实施例中,时钟信号布线545可以被布置在源图案524和漏图案525上。时钟信号布线545在平面图中可以被布置为与栅图案526重叠。由于时钟信号布线545和栅图案526在平面图中被布置为彼此重叠,因此寄生电容可能发生在时钟信号布线545与栅图案526之间。耦合现象可能由于寄生电容而发生在时钟信号布线545与栅图案526之间。当耦合现象发生时,可能引起扫描驱动器200和发射驱动器300的故障。耦合现象可能在扫描信号和发射信号中引起故障现象。由于故障现象的发生,可能发生短路,这可能增加功耗。根据本发明,可以布置屏蔽图案527以防止这种耦合现象。

90.屏蔽图案527可以被布置在第一层间绝缘层530上。在实施例中,屏蔽图案527可以与图6的电容电极536被布置在同一层中。屏蔽图案527可以由与图6的电容电极536相同的材料同时形成。

91.屏蔽图案527可以被布置在源图案524与漏图案525之间,以便在平面图中不与源图案524和漏图案525中的任何一个重叠。屏蔽图案527可以被布置在栅图案526与时钟信号布线545之间。屏蔽图案527在平面图中可以被布置为与栅图案526和时钟信号布线545重叠。恒定电压(例如,第一恒定电压vgh、第二恒定电压vgl)可以被施加到屏蔽图案527。由于恒定电压具有恒定的极性和大小,因此施加有恒定电压的屏蔽图案527可以通过被定位在栅图案526与时钟信号布线545之间来屏蔽栅图案526和时钟信号布线545。由于屏蔽图案527屏蔽了栅图案526和时钟信号布线545,因此可以有效地防止可能在栅图案526与时钟信号布线545之间发生的耦合现象。

92.第二通孔绝缘层550可以被布置在时钟信号布线545上。第二通孔绝缘层550可以包括有机材料或无机材料或者由有机材料或无机材料制成。在实施例中,第一通孔绝缘层

540可以由诸如丙烯酸、苯并环丁烯(bcb)、聚酰亚胺或六甲基二硅氧烷(hmdso)的有机材料形成。

93.图9是图示驱动晶体管的另一实施例的平面图,并且图10是沿图9的线iii

‑

iii’截取的截面图。

94.参考图9和图10,驱动电路130可以包括基板510、缓冲层515、栅绝缘层520、驱动晶体管的有源图案521和栅图案526、第一层间绝缘层530、第二层间绝缘层535、第一通孔绝缘层540、第二通孔绝缘层550、屏蔽图案527、时钟信号布线545和连接布线546。有源图案521可以在导通时电接触源图案524和漏图案525。

95.在实施例中,连接布线546可以与时钟信号布线545被布置在同一层中。连接布线546可以被布置为与时钟信号布线545间隔开。连接布线546可以通过穿过第一通孔绝缘层540和第二层间绝缘层535的接触孔连接到屏蔽图案527。恒定电压(例如,第一恒定电压vgh、第二恒定电压vgl)可以被施加到连接布线546。施加到连接布线546的恒定电压可以通过接触孔传输到屏蔽图案527。屏蔽图案527可以通过使用恒定电压来有效地防止时钟信号布线545与栅图案526之间的耦合现象。连接布线546可以与时钟信号布线545被布置在同一层中。连接布线546可以由与时钟信号布线545相同的材料同时形成。在实施例中,连接布线546和时钟信号布线545可以被布置在源图案524上。

96.图11是图示驱动晶体管的又一实施例的平面图,并且图12是沿图11的线iv

‑

iv’截取的截面图。

97.参考图11和图12,驱动电路130可以包括基板510、缓冲层515、栅绝缘层520、驱动晶体管的有源图案521和栅图案526、第一层间绝缘层530、第二层间绝缘层535、第一通孔绝缘层540、第二通孔绝缘层550、屏蔽图案527、时钟信号布线545和连接布线547。有源图案521可以在导通时电接触源图案524和漏图案525。

98.栅图案526在平面图中可以与有源图案521部分重叠,并且可以被布置在栅绝缘层520上。屏蔽图案527在平面图中可以与栅图案526部分重叠,并且可以被布置在第一层间绝缘层530上。屏蔽图案527可以被布置在时钟信号布线545与栅图案526之间,以防止时钟信号布线545与栅图案526之间的耦合现象。时钟信号布线545在平面图中可以被布置为在栅图案526和屏蔽图案527重叠的范围内与屏蔽图案527重叠。

99.连接布线547可以被布置在第二层间绝缘层535上。连接布线547可以通过穿过第二层间绝缘层535的接触孔连接到屏蔽图案527。恒定电压(例如,第一恒定电压vgh、第二恒定电压vgl)可以被施加到连接布线547。施加到连接布线547的恒定电压可以通过接触孔传输到屏蔽图案527。屏蔽图案527可以通过使用恒定电压来有效地防止时钟信号布线545与栅图案526之间的耦合现象。

100.在实施例中,连接布线547可以与源图案524和漏图案525被布置在同一层中。连接布线547可以包括与源图案524和漏图案525相同的材料或者由与源图案524和漏图案525相同的材料形成。在实施例中,时钟信号布线545可以被布置在源图案524、漏图案525和连接布线547上。

101.图13是图示驱动电路双栅晶体管的又一实施例的平面图,并且图14是沿图13的线v

‑

v’截取的截面图。

102.参考图13和图14,驱动电路130可以包括基板510、缓冲层515、栅绝缘层520、驱动

晶体管528b、第一层间绝缘层530、第二层间绝缘层535、第一通孔绝缘层540、第二通孔绝缘层550、屏蔽图案527和时钟信号布线545。驱动晶体管528b可以包括有源图案521、源图案524、漏图案525和栅图案526。

103.栅图案526可以被布置在栅绝缘层520上。栅图案526可以是包括第一子栅图案526a和第二子栅图案526b的双栅极。第一子栅图案526a和第二子栅图案526b在平面图中可以被布置在源图案524与漏图案525之间。在实施例中,屏蔽图案527可以屏蔽第一子栅图案526a和第二子栅图案526b两者以防止耦合现象。进一步,屏蔽图案527可以被布置在源图案524和漏图案525的主表面平面(其被布置在第二层间绝缘层535上)下。时钟信号布线545可以被布置在源图案524和漏图案525上。

104.屏蔽图案527在平面图中可以被布置为与第一子栅图案526a和第二子栅图案526b重叠。屏蔽图案527可以防止第一子栅图案526a和第二子栅图案526b与时钟信号布线545之间的耦合现象。

105.图15是图示驱动电路双栅晶体管的另一实施例的平面图,并且图16是沿图15的线vi

‑

vi’截取的截面图。

106.如图15和图16中所图示,屏蔽图案527在平面图中可以与第一子栅图案526a和第二子栅图案526b中的一个重叠。

107.图17是图示驱动电路双栅晶体管的又一实施例的平面图,并且图18是沿图17的线vii

‑

vii’截取的截面图。

108.参考图17和图18,驱动电路130可以包括基板510、缓冲层515、栅绝缘层520、驱动晶体管528c、第一层间绝缘层530、第二层间绝缘层535、第一通孔绝缘层540、第二通孔绝缘层550、屏蔽图案527和时钟信号布线545。驱动晶体管528c可以包括有源图案521、源图案524、漏图案525和栅图案526。源图案524可以包括第一子源图案524a和第二子源图案524b。

109.栅图案526可以被布置在栅绝缘层520上。栅图案526可以是包括第一子栅图案526a和第二子栅图案526b的双栅极。第一子栅图案526a和第二子栅图案526b可以被布置在第一子源图案524a与第二子源图案524b之间。

110.屏蔽图案527可以被布置在第一层间绝缘层530上。屏蔽图案527可以包括第一子屏蔽图案527a和第二子屏蔽图案527b。屏蔽图案527在平面图中可以被布置为与栅图案526重叠。在实施例中,第一子屏蔽图案527a在平面图中可以被布置为与第一子栅图案526a重叠,并且第二子屏蔽图案527b在平面图中可以被布置为与第二子栅图案526b重叠。这样,可以有效地防止时钟信号布线545与第一子栅图案526a和第二子栅图案526b中的每一个之间的耦合现象。

111.第一子源图案524a、第二子源图案524b和漏图案525可以被布置在第二层间绝缘层535上。第一子源图案524a和第二子源图案524b可以通过穿过栅绝缘层520、第一层间绝缘层530和第二层间绝缘层535的接触孔连接到有源图案521的第一源区和第二源区。漏图案525可以通过穿过栅绝缘层520、第一层间绝缘层530和第二层间绝缘层535的接触孔连接到有源图案521的漏区。在实施例中,时钟信号布线545可以被布置在第一子源图案524a和第二子源图案524b以及漏图案525上。

112.图19是图示驱动电路双栅晶体管的又一实施例的平面图,并且图20是沿图19的线viii

‑

viii’截取的截面图。

113.如图19和图20中所图示,屏蔽图案527在平面图中可以与第一子栅图案526a和第二子栅图案526b中的一个重叠。

114.图21是图示驱动晶体管的另一实施例的平面图,并且图22是沿图21的线ix

‑

ix’截取的截面图。

115.参考图21和图22,驱动电路130可以包括基板510、缓冲层515、栅绝缘层520、驱动晶体管528a、第一层间绝缘层530、第二层间绝缘层535、第一通孔绝缘层540、第二通孔绝缘层550、时钟信号布线548和屏蔽图案549。驱动晶体管528a可以包括有源图案521、源图案524、漏图案525和栅图案526。

116.屏蔽图案549可以被布置在第一通孔绝缘层540上。屏蔽图案549在平面图中可以被布置为与栅图案526重叠。屏蔽图案549在平面图中可以不与源图案524和漏图案525重叠。恒定电压(例如,第一恒定电压vgh、第二恒定电压vgl)可以被施加到屏蔽图案549。当恒定电压被施加到屏蔽图案549时,屏蔽图案549可以屏蔽栅图案526。在实施例中,屏蔽图案549可以与图10的连接布线546被布置在同一层中。也就是说,屏蔽图案549可以被布置在源图案524和漏图案525上。

117.时钟信号布线548可以被布置在第二通孔绝缘层550上。时钟信号布线548可以被布置在屏蔽图案549上。时钟信号可以流过时钟信号布线548。由于屏蔽图案549在平面图中被布置为与栅图案526重叠,因此可以有效地防止栅图案526与时钟信号布线548之间的耦合现象。屏蔽图案549可以包括金属、合金、金属氮化物、导电金属氧化物、透明导电材料等。这些可以单独使用或彼此结合使用。

118.本发明构思可以被应用于显示装置和包括该显示装置的电子装置。例如,本发明构思可以被应用于智能电话、蜂窝电话、视频电话、智能平板、智能手表、平板pc、汽车导航系统、电视、计算机监视器、便携式计算机、头戴式显示装置、mp3播放器等。

119.前述内容是对实施例的说明,并且不应被解释为对实施例的限制。尽管已经描述了实施例,但是本领域技术人员将容易理解,在本质上不脱离本发明构思的新颖教导和优点的情况下,可以在实施例中进行许多修改。因此,所有这些修改旨在包括在如权利要求中限定的本发明构思的范围内。因此,要理解,前述内容是对实施例的说明,并且不应被解释为限于所公开的示例实施例,并且对所公开的示例实施例以及其他示例实施例的修改旨在包括在所附权利要求的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1