高电子迁移率晶体管及其制作方法与流程

1.本发明涉及半导体技术领域,特别是涉及一种高电子迁移率晶体管(high electron mobility transistor,hemt)结构及其制作方法。

背景技术:

2.高电子迁移率晶体管为一种新兴的场效晶体管,其利用接合不同能隙的半导体材料而在异质结(heterojunction)处形成位能阱(potential well),可汇聚电子而形成二维电子气层(two-dimensional electron gas,2deg)作为元件电流的通道区。iii-v族半导体化合物之中的氮化镓(gan)系列化合物由于具有宽能隙(band gap)、高击穿电压、高键结力与热稳定性,以及独特的自发极化(spontaneous polarization)和压电极化(piezoelectric polarization)特性,可在未掺杂的状况下即形成高电子浓度及高电子迁移率的二维电子气层,达到高切换速度及响应频率,因此已逐渐取代硅基晶体管,广泛应用在功率转换器、低噪声放大器、射频(rf)或毫米波(mmw)等技术领域中。

3.目前业界常用的增强型(enhancement mode)gan高电子迁移率晶体管,主要具有一p型氮化镓/氮化铝镓/氮化镓(p-gan/algan/gan)异质堆叠结构,其中p-gan层被设计为半导体栅极,并且与设置在其上方的一栅极电极电连接。在无偏压(bias voltage)的情况下,p-gan层本身之内建电压(built-in voltage)可拉升algan和gan之间的能带从而空乏了二维电子气层,从而实现晶体管的常闭(normally-off)操作。然而,现有的增强型高电子迁移率晶体管仍遭遇一些问题,例如操作晶体管时,栅极电极于p-gan栅极层内造成的电场会在p-gan层的侧壁形成寄生晶体管(parasitic transistor),成为栅极漏电途径,导致晶体管效能下降并对元件可靠度造成不良影响。

技术实现要素:

4.为了克服上述问题,本发明提供了一种增强型高电子迁移率晶体管及其制作方法,其主要在半导体栅极层和栅极电极之间设置一金属栅极层,并使金属栅极层的侧壁往远离半导体栅极层的侧壁的方向退缩,由此降低了操作晶体管时半导体栅极层的侧壁的电场强度,进而改善了由于寄生晶体管造成栅极漏电流。

5.本发明一实施例提供了一种高电子迁移率晶体管的制作方法,步骤包括提供一基底,接着形成一缓冲层于该基底上、一通道层于该缓冲层上、一势垒层于该通道层上,以及一半导体栅极层于该势垒层上。然后,在该半导体栅极层上形成一金属栅极层,并形成一间隙壁于该金属栅极层的侧壁上。以该金属栅极层及该间隙壁为掩模来蚀刻半导体栅极层,然后形成一钝化层覆盖该势垒层、该半导体栅极层以及该金属栅极层。接着,在该钝化层中形成一开口以暴露出该金属栅极层,再形成一栅极电极于该钝化层上并直接接触该金属栅极层。

6.本发明另一实施例提供了一种高电子迁移率晶体管的制作方法,步骤包括提供一基底,接着形成一缓冲层于该基底上、一通道层于该缓冲层上、一势垒层于该通道层上,以

及一半导体栅极层于该势垒层上。然后,在该半导体栅极层上形成一金属栅极层以及一虚设栅极于该金属栅极层上,并形成一间隙壁于该金属栅极层以及该虚设栅极的侧壁上。以该虚设栅极及该间隙壁为掩模来蚀刻半导体栅极层,然后形成一钝化层覆盖该势垒层、该半导体栅极层以及该虚设栅极。接着,在该钝化层中形成一开口以暴露出该虚设栅极,再移除该虚设栅极并暴露出该金属栅极层。后续,形成一栅极电极于该钝化层上并直接接触该金属栅极层。

7.本发明又另一实施例提供了一种高电子迁移率晶体管,包括一基底、一缓冲层设于该基底上、一通道层设于该缓冲层上、一势垒层设于该通道层上、一半导体栅极层设于该势垒层上、一金属栅极层设于该半导体栅极层上,以及一栅极电极设于该金属栅极层上,其中该半导体栅极层位于该金属栅极层两侧的部分包括一凹陷顶面。

附图说明

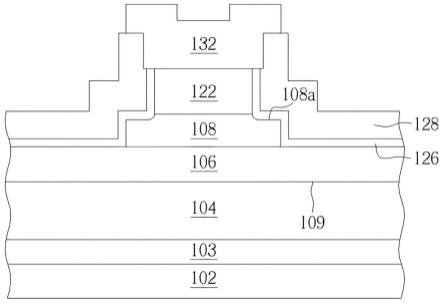

8.图1至图5为本发明第一实施例的高电子迁移率晶体管的制作方法步骤示意图;

9.图6为图5所示第一实施例的高电子迁移率晶体管的一变化型的示意图;

10.图7至图12为本发明第二实施例的高电子迁移率晶体管的制作方法步骤示意图;

11.图13为图12所示第一实施例的高电子迁移率晶体管的一变化型的示意图。

12.主要元件符号说明

13.102 基底

14.103 缓冲层

15.104 通道层

16.106 势垒层

17.108 半导体栅极层

18.108a 凹陷顶面

19.109 接面

20.122 金属栅极层

21.124 间隙壁

22.126 绝缘层

23.128 钝化层

24.130 开口

25.132 栅极电极

26.202 基底

27.203 缓冲层

28.204 通道层

29.206 势垒层

30.208 半导体栅极层

31.208a 凹陷顶面

32.209 接面

33.222 金属栅极层

34.223 虚设栅极

35.224 间隙壁

36.226 绝缘层

37.228 钝化层

38.230 开口

39.232 栅极电极

40.232a 第一部分

41.232b 第二部分

42.232c 第三部分

43.t1 厚度

44.t2 厚度

45.t3 厚度

46.t4 厚度

47.t5 厚度

48.t6 厚度

49.t7 厚度

50.w1 宽度

51.w2 宽度

具体实施方式

52.为使熟悉本发明所属技术领域的一般技术者能更进一步了解本发明,下文特列举本发明的优选实施例,并配合所附的附图,详细说明本发明的构成内容及所欲达成的功效。需知悉的是,以下所举实施例可以在不脱离本揭露的精神下,将数个不同实施例中的特征进行替换、重组、混合以完成其他实施例。

53.图1至图5所绘示为根据本发明第一实施例的高电子迁移率晶体管(hemt)的制作方法步骤示意图。请参考图1,首先提供一基底102,接着于基底102上形成一外延叠层,由下(靠近基底102)而上(远离基底)依序包括缓冲层103、通道层104、势垒层106,以及半导体栅极层108。然后,再于半导体栅极层108上形成金属栅极层122。根据本发明一实施例,缓冲层103、通道层104势垒层106,以及半导体栅极层108可通过异质外延成长(heteroepitaxy growth)制作工艺形成在基底102上。适用的异质外延成长技术例如分子束外延(molecule beam epitaxy,mbe)、金属有机化学气相沉积(metal-organic chemical vapor deposition,mocvd)、氢化物气相沉积(hydride vapor phase deposition,hvpe),但不限于此。

54.基底102可包括硅基底、碳化硅(sic)基底、蓝宝石(sapphire)基底、氮化镓基底、氮化铝基底,或由其他适合的材料所形成的基底。缓冲层103、通道层104,势垒层106,以及半导体栅极层108的材料分别可包括iii-v族半导体化合物材料,例如分别可包括氮化镓(gan)、氮化铝镓(algan)、渐变氮化铝镓(graded algan)、氮化铝铟(alinn)、氮化铟镓(ingan)、氮化铝镓铟(algainn)、含掺杂氮化镓(doped gan)、氮化铝(aln),或上述的组合,但不限于此。根据本发明一实施例,缓冲层103的材料可包括氮化铝镓(algan),通道层104的材料可包括氮化镓(gan),势垒层106的材料可包括氮化铝镓(algan)。势垒层106与通道

层104的接面109附近形成有二维电子气层(图未示),为高电子迁移率晶体管导通(on-state)时的一平面电流通道。

55.半导体栅极层108的材料可根据高电子迁移率晶体管的应用类型来选择具有n导电型(negative conductive type)或p导电型(positive conductive type),利用其内建电压(built-in voltage)来拉升能带而空乏(deplete)其正下方的二维电子气层,实现常闭(normally-off)操作。根据本发明一实施例,半导体栅极层108的材料可包含镁(mg)、铁(fe)或其他合适掺杂的p型氮化镓(p-gan),但不限于此。

56.可通过设计通道层104、势垒层106,以及半导体栅极层108的厚度进而调整二维电子气层的电子分布及迁移率以获得期望的效能。根据本发明一实施例,通道层104厚度t1介于大约5nm至400nm之间,势垒层106厚度t2介于大约10nm至14nm之间,半导体栅极层108厚度t3介于大约70nm至90nm之间,但不限于此。

57.可通过例如化学气相沉积(cvd)、物理气相沉积(pvd),或原子层沉积(ald)制作工艺在半导体栅极层108上形成一导电层(图未示),接着利用图案化制作工艺(例如光刻暨蚀刻制作工艺)来图案化导电层而获得金属栅极层122。如图1所示,金属栅极层122可具有厚度t4。

58.值得注意的是,在图案化导电层的过程中,半导体栅极层108自金属栅极层122暴露出来的部分也会被蚀刻损失部分厚度,因此会具有略低于金属栅极层122底面的凹陷顶面108a。换言之,半导体栅极层108被金属栅极层122覆盖住的顶面以及自金属栅极层122暴露出来的顶面不共平面。

59.金属栅极层122可包括金属或金属化合物材料,例如金(au)、钨(w)、钴(co)、镍(ni)、钛(ti)、钼(mo)、铜(cu)、铝(al)、钽(ta)、钯(pd)、铂(pt)、上述金属的化合物、复合层或合金,但不限于此。根据本发明一实施例,金属栅极层122材料可包括氮化钛(tin),且较佳与半导体栅极层108形成萧基接触(schottky contact)而提供整流功能。根据本发明一实施例,金属栅极层122上可包括一硬掩模层(图未示),例如一氮化硅(sin)层。

60.请参考图2,接着于金属栅极层122的侧壁上形成间隙壁124,然后以金属栅极层122及间隙壁124为掩模对半导体栅极层108进行蚀刻直到暴露出势垒层106,以图案化半导体栅极层108。间隙壁124可通过现有的自对准间隙壁制作工艺(self-aligned spacer process)获得,例如先形成一间隙壁材料层(图未示)全面性地覆盖半导体栅极层108表面和金属栅极层122的侧壁和顶面,然后进行一各向异性蚀刻制作工艺移除半导体栅极层108表面和金属栅极层122顶面的间隙壁材料层,并使间隙壁材料层剩余在金属栅极层122侧壁,获得间隙壁124。需特别说明的是,金属栅极层122需具有足够的厚度t4以具有足够的侧壁高度来顺利进行自对准间隙壁制作工艺。因此,在同时考虑不过度提高栅极电阻的情况下,金属栅极层122的厚度t4较佳约是半导体栅极层108的厚度t3的1倍至1.5倍。根据本发明一实施例,半导体栅极层108的厚度t3可介于大约70nm至90nm之间,金属栅极层122的厚度t4则可介于大约120nm至140nm之间。

61.请参考图3,接着移除间隙壁124,然后形成绝缘层126以及钝化层128全面性地覆盖住势垒层106表面、半导体栅极层108侧壁及自金属栅极层122暴露出来的凹陷顶面108a,以及金属栅极层122侧壁和顶面。绝缘层126以及钝化层128的材料分别可包括绝缘材料,例如但不限于氮化铝(aln)、氧化铝(al2o3)、氮化硼(bn)、氮化硅(si3n4)、氧化硅(sio2)、氧化

锆(zro2)、氧化铪(hfo2)、氧化镧(la2o3)、氧化镏(lu2o3)、氧化镧镏(laluo3)、高介电常数(high-k)介电材料或其他适合的绝缘材料。通过绝缘层126及钝化层128的材料的搭配,可降低高电子迁移率晶体管的漏电流并提升击穿电压和输出功率。根据本发明一实施例,绝缘层126的材料可包括氧化铝(al2o3),钝化层128的材料可包括氧化硅(sio2)。

62.请参考图4,接着进行一图案化制作工艺,例如光刻暨蚀刻制作工艺,以于金属栅极层122正上方的绝缘层126和钝化层128中形成开口130暴露出金属栅极层122表面。如图4所示,开口130的宽度w1可略大于金属栅极层122的宽度,或者在其他实施例中可选择开口130的宽度w1大致上等于或略小于金属栅极层122的宽度。值得注意的是,金属栅极层122两侧的绝缘层126和钝化层128可于制作开口130的蚀刻步骤中用作蚀刻缓冲层,确保当开口130的宽度w1大于金属栅极层122的宽度或者开口130与金属栅极层122之间发生对准偏移时,不会蚀刻到下方的半导体栅极层108而造成损坏。

63.请参考图5,接着于钝化层128上形成栅极电极132并使栅极电极132通过开口130直接接触金属栅极层122。栅极电极132可包括金属材料,例如金(au)、钨(w)、钴(co)、镍(ni)、钛(ti)、钼(mo)、铜(cu)、铝(al)、钽(ta)、钯(pd)、铂(pt)、上述金属的化合物、复合层或合金,但不限于此。根据本发明一实施例,栅极电极132材料可包括铝(al)、铜(cu),或铝铜合金。如图5所示,本发明第一实施例提供的高电子迁移率晶体管包括一基底102、一缓冲层103设于基底102上、一通道层104设于缓冲层103上、一势垒层106设于通道层104上、一半导体栅极层108设于势垒层106上、一金属栅极层122设于半导体栅极层108上,以及一栅极电极132设于金属栅极层122上并直接接触金属栅极层122,其中半导体栅极层108位于金属栅极层122两侧的部分包括一凹陷顶面108a。高电子迁移率晶体管还包括一绝缘层126以及一钝化层128沿着势垒层106表面、半导体栅极层108侧壁、半导体栅极层108的凹陷顶面108a、金属栅极层122侧壁,以及栅极电极132侧壁覆盖。本发明提供的高电子迁移率晶体管在操作时栅极偏压(gate bias voltage)是通过栅极电极132和金属栅极层122施加至半导体栅极层108,由于金属栅极层122的侧壁往远离半导体栅极层108的侧壁的退缩,因此降低了半导体栅极层108侧壁的电场强度,达到减少由于寄生晶体管造成的栅极漏电流。

64.图6所绘示为图5所示第一实施例的高电子迁移率晶体管的一变化型,其中相同的元件是以相同的标号进行标示,以利于互相对照。图6的高电子迁移率晶体管在蚀刻半导体栅极层108之后并未移除间隙壁124,而是将保留间隙壁124于金属栅极层122的侧壁和半导体栅极层108的凹陷顶面108a上,接着形成绝缘层126和钝化层128覆盖势垒层106、半导体栅极层108、间隙壁124,以及金属栅极层122。本变化型中,当间隙壁124材料不同于绝缘层126和钝化层128时,间隙壁124可利用蚀刻选择性而在制作开口130(参考图4)的蚀刻步骤中作为蚀刻阻挡层,提供半导体栅极层108更好的保护。

65.图7至图12所绘示为根据本发明第二实施例的高电子迁移率晶体管(hemt)的制作方法步骤示意图。请参考图7,首先提供一基底202,接着于基底202上形成一外延叠层,由下(靠近基底202)而上(远离基底)依序包括缓冲层203、通道层204、势垒层206,以及半导体栅极层208。然后,再于半导体栅极层208上形成金属栅极层222以及一虚设栅极223。基底202、缓冲层203、通道层204、势垒层206、半导体栅极层208,以及金属栅极层222的可选材料请参考前文记载,在此不再重述。势垒层206与通道层204的接面209附近形成有二维电子气层(图未示),为高电子迁移率晶体管导通(on-state)时的一平面电流通道。虚设栅极223的材

料需不同于后续形成的绝缘层226以及钝化层228(参考图9)。根据本发明一实施例,虚设栅极223的材料可包括多晶硅(poly silicon)。

66.金属栅极层222及虚设栅极223的制作方法例如可包括于半导体栅极层108上形成一导电层(图未示)及一多晶硅层(图未示)后,接着利用图案化制作工艺(例如光刻暨蚀刻制作工艺)来同时图案化导电层和多晶硅层,获得金属栅极层222及虚设栅极223。值得注意的是,在图案化导电层和多晶硅层的过程中,半导体栅极层208暴露出来的部分也会被蚀刻损失部分厚度,因此会具有略低于金属栅极层222底面的凹陷顶面208a。换言之,半导体栅极层208被金属栅极层222覆盖住的顶面以及自金属栅极层222暴露出来的顶面不共平面。

67.此外,为了提供足够的侧壁高度以顺利进行自对准间隙壁制作工艺制作出间隙壁224(参考图8),本实施例的金属栅极层222的厚度t6和虚设栅极223的厚度t7的总和较佳大约是半导体栅极层208的厚度t5的1至1.5倍,且为了在后续获得较低的栅极电阻,厚度t6较佳小于厚度t7。例如,根据本发明一实施例,半导体栅极层208的厚度t5可介于大约是70nm至90nm之间,金属栅极层222的厚度t6可介于大约25nm至35nm之间,虚设栅极223的厚度t7可介于大约90nm至110nm之间,但不限于此。

68.请参考图8,接着于金属栅极层222以及虚设栅极223的侧壁上形成间隙壁224,然后以虚设栅极223及间隙壁224为掩模对半导体栅极层208进行蚀刻直到暴露出势垒层206,以图案化半导体栅极层208。

69.请参考图9,接着移除间隙壁224,然后形成绝缘层226和钝化层228全面性地覆盖住势垒层206、半导体栅极层208、金属栅极层222,以及虚设栅极223。绝缘层226和钝化层228的可选材料请参考前文记载,在此不再重述。

70.请参考图10,接着进行一图案化制作工艺,例如光刻暨蚀刻制作工艺,以于虚设栅极223正上方的绝缘层226和钝化层228中形成开口230暴露出虚设栅极223。如图10所示,开口230的宽度w2可略大于虚设栅极223的宽度,或者在其他实施例中可选择开口230的宽度w2大致上等于或略小于虚设栅极223的宽度。

71.请参考图11,接着进行一蚀刻制作工艺,例如湿蚀刻制作工艺,自开口230移除虚设栅极223以暴露出金属栅极层222表面。

72.请参考图12,接着于钝化层228上形成栅极电极232并使栅极电极232通过开口230直接接触金属栅极层222。栅极电极232的可选材料请参考前文记载,在此不再重述。如图12所示,本发明第一实施例提供的高电子迁移率晶体管包括一基底202、一缓冲层203设于基底202上、一通道层204设于缓冲层203上、一势垒层206设于通道层204上、一半导体栅极层208设于势垒层206上、一金属栅极层222设于半导体栅极层208上,以及一栅极电极232设于金属栅极层222上,其中半导体栅极层208位于金属栅极层222两侧的部分包括一凹陷顶面208a。高电子迁移率晶体管还包括一绝缘层226以及一钝化层128沿着势垒层206表面、半导体栅极层208侧壁、半导体栅极层208的凹陷顶面208a、金属栅极层222侧壁,以及栅极电极232侧壁覆盖。值得注意的是,在图12所示实施例中,栅极电极232可包括直接接触金属栅极层222并且由绝缘层226而与钝化层228隔离开的第一部分232a,位于第一部分232a上且与钝化层228直接接触的第二部分232b,以及位于第二部分232b上且横向延伸至覆盖钝化层228部分表面的第三部分232c,其中第一部分232a的侧壁会与金属栅极层222的侧壁在垂直方向上对齐。

73.图13所绘示为图12所示第二实施例的高电子迁移率晶体管的一变化型,其中相同的元件是以相同的标号进行标示,以利于互相对照。图13的高电子迁移率晶体管在蚀刻半导体栅极层208之后并未移除间隙壁224,而是将保留间隙壁224于虚设栅极223和金属栅极层222的侧壁以及半导体栅极层208的凹陷顶面208a上,接着形成绝缘层226和钝化层228覆盖住势垒层206、半导体栅极层208、间隙壁224,以及虚设栅极223。本变化型中,绝缘层226与金属栅极层222之间被间隙壁224隔离开而不直接接触。

74.综上所述,本发明提供的高电子迁移率晶体管及其制作方法,其主要在半导体栅极层和栅极电极之间设置一金属栅极层并使金属栅极层的侧壁往远离半导体栅极层的侧壁的方向退缩,由此降低了操作晶体管时半导体栅极层的侧壁的电场强度,进而改善了由于寄生晶体管造成栅极漏电流。

75.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1