MIS分裂栅GaN基高电子迁移率晶体管及其制备方法

mis分裂栅gan基高电子迁移率晶体管及其制备方法

技术领域

1.本发明涉及晶体管领域,特别涉及一种mis分裂栅gan基高电子迁移率晶体管及其制备方法。

背景技术:

2.众所知周,第三代半导体材料 gan 具有高饱和电子漂移速度、高热导率、耐高温、抗辐射、高临界击穿电压等特点,因此成为高温、高压、高频等极端环境中大功率器件的首选材料。基于gan异质结的高电子迁移率晶体管,该结构利用高电导率二维电子气(2deg)实现强大的电流驱动, 同时保持了氮化物材料的高耐压能力。

3.对于增强型高电子迁移率晶体管器件的研究,目前有多种比较主流的技术方案,有凹槽栅结构、氟离子注入技术、p型栅帽层结构、薄势垒层结构、纳米线沟道结构、cascode级联的方式等。最为广泛的是凹槽栅结构,这种技术工艺相对比较简单,如果不完全刻蚀,阈值电压不高且不稳定,如果完全刻蚀掉势垒层的话,阈值电压对应着比较大的一个数值,并且栅区的工作电压或者说栅区摆幅比较大,这是它的优势。它不足之处在于刻蚀的界面一般比较粗糙,因此沟道下方的载流子的迁移率一般比较低。其次在刻蚀界面上,生长介质层的时候往往会有可靠性问题,现在并不能很好的解决。

4.分裂栅技术是通过在两个栅之间加入阻挡层的方式增加沟道区导通的难度,进而提高器件的阈值电压。但是阻挡层的深度和宽度并不是越大越好,高的阈值电压有可能会带来较低的饱和漏极电流,甚至导致器件不能正常开启,所以需要通过对阻挡层尺寸做渐变,以找到最优的尺寸。

技术实现要素:

5.为了解决上述技术问题,本发明提供一种结构简单、安全可靠的mis分裂栅gan基高电子迁移率晶体管,并提供其制备方法。

6.本发明解决上述问题的技术方案是:一种mis分裂栅gan基高电子迁移率晶体管,包括从下而上依次层叠的硅衬底、ain成核层、algan缓冲层、gan沟道层、algan势垒层,algan势垒层包括从下而上依次层叠的第一algan势垒层、第二algan势垒层、第三algan势垒层,第三algan势垒层上表面设有凹槽且凹槽沿第三algan势垒层伸入第二algan势垒层中,凹槽的槽底和槽壁上设有栅介质层,栅介质层底部设有两个栅极,其中靠近漏极的栅极设有栅场板,两个栅极之间设有阻挡层且阻挡层向下穿过栅介质层延伸至gan沟道层,第三algan势垒层上表面两侧分别设有源极和漏极,源极上设有源场板,第三algan势垒层上表面位于源极和漏极之间设有钝化层。

7.上述mis分裂栅gan基高电子迁移率晶体管,所述第二algan势垒层、第一algan势垒层、第三algan势垒层中铝组分分别为0.03、0.15、0.25, algan缓冲层铝组分与第二algan势垒层铝组分相同。

8.上述mis分裂栅gan基高电子迁移率晶体管,所述algan缓冲层的厚度为1~2μm,gan

沟道层的厚度为10~20nm,第一algan势垒层的厚度为2~10nm,第二algan势垒层的厚度为10nm,第三algan势垒层的厚度为25nm。

9.上述mis分裂栅gan基高电子迁移率晶体管,所述钝化层为sin,厚度为2μm。

10.上述mis分裂栅gan基高电子迁移率晶体管,所述栅介质层为al2o3,厚度为10~20nm。

11.上述mis分裂栅gan基高电子迁移率晶体管,所述阻挡层为sin,宽度为0.2μm,深度为37nm。

12.上述mis分裂栅gan基高电子迁移率晶体管,所述源极和漏极为ti/al/ni/au欧姆接触复合金属层,所述栅极为ni/au肖特基接触复合金属层。

13.一种mis分裂栅gan基高电子迁移率晶体管的制备方法,其特征在于,步骤如下:1)对硅衬底进行热处理和表面氮化;2)在氮化后的硅衬底表面依次生长ain成核层、algan缓冲层、gan沟道层、第一algan势垒层、第二algan势垒层、第三algan势垒层,形成外延片;3)刻蚀形成源极区域、漏极区域以及凹槽栅区域:在第三algan势垒层上,从源极至漏极方向,依次完全刻蚀宽1μm的源极区域,间隔1μm之后刻蚀凹槽栅区域,宽度为1.6μm,深度为30nm,接着间隔15μm刻蚀宽1μm漏极区域;4)在凹槽栅区域沉积栅介质层:采用氧化铝作为栅极介质,在凹槽中沉积厚度为10~20nm的al2o3栅介质层;5)在源极区域和漏极区域沉积欧姆接触金属层,以形成源极和漏极:在暴露的第三algan势垒层上采用电子束蒸发器沉积ti/al/ni/au/四层欧姆接触金属,沉积完毕后利用电感耦合等离子刻蚀系统实现mesa分离,超声清洗氮气,将源、漏窗口以外金属剥离,然后进行30s欧姆接触退火,形成源极和漏极;6)在栅区域沉积金属层形成栅极:用电子束蒸发法沉积ni/au两层金属,退火后形成栅极;7)沉积钝化层:通过等离子体增强化学气相沉积法沉积sin钝化层;8)刻蚀阻挡区,沉积阻挡层:通过反应离子蚀刻去除位于双栅极之间的sin,双栅之间的al2o3栅介质层用氢氟酸除去,然后用等离子干法刻蚀algan势垒层,最后沉积sin阻挡层;9)在栅极沉积栅场板金属,在源极沉积源场板金属;10)再次沉积钝化层:在已形成源漏栅极结构的表面上,光刻获得加厚电极图案,采用电子束蒸发技术加厚电极,完成器件制造。

14.上述mis分裂栅gan基高电子迁移率晶体管的制备方法,所述步骤2)中,采用金属有机化学气相沉积法在硅衬底上外延厚度为1nm的ain成核层,然后外延厚度为2μm的algan缓冲层,其中algan缓冲层铝组分为0.03,在缓冲层之上继续外延gan沟道层,沟道层厚度10~20nm,接着外延第一algan势垒层、第二algan势垒层、第三algan势垒层,第一algan势垒层、第二algan势垒层、第三algan势垒层铝组分分别为0.15、0.03、0.25,厚度分别为2nm、15nm、25nm。

15.本发明的有益效果在于:1、本发明包括位于衬底之上的ain成核层、algan缓冲层、gan沟道层、algan势垒

层,且algan势垒层是由不同铝组分的algan层所组成,从下至上依次为第一algan势垒层、第二algan势垒层、第三algan势垒层,第二algan势垒层和algan缓冲层具有相同的铝组分,完全耗尽第一algan势垒层与第二algan势垒层之间的极化电荷,且凹槽栅底部正处于第二algan势垒层之中,进而降低因刻蚀因素对器件阈值电压稳定性的影响。第三algan势垒层具有最高的铝组分使得在gan沟道层和第二algan势垒层上表面都能产生高浓度的二维电子气。

16.2、本发明采用分裂栅结构,在两个栅之间加入一个阻挡层,通过增加阻挡层的深度和宽度,能够大幅提高器件的阈值电压。

17.3、本发明设有栅场板和源场板,采用场板技术对器件耐高压能力进行优化,从而得到一个高性能增强型mis分裂栅gan基高电子迁移率晶体管。

附图说明

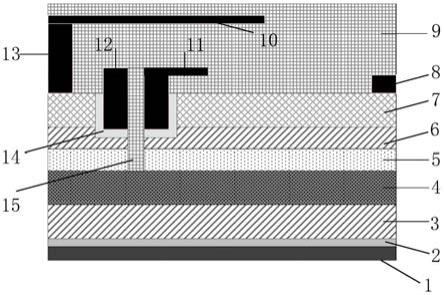

18.图1为本发明mis分裂栅gan基高电子迁移率晶体管的剖面图。

19.图2为本发明实施例提供的mis分裂栅gan基高电子迁移率晶体管的转移特性仿真图。

20.图3为本发明实施例提供的mis分裂栅gan基高电子迁移率晶体管的输出特性仿真图。

21.图4为本发明实施例提供的mis分裂栅gan基高电子迁移率晶体管的击穿特性仿真图。

具体实施方式

22.下面结合附图和实施例对本发明做进一步的说明。

23.如图1所示,一种mis分裂栅gan基高电子迁移率晶体管,包括从下而上依次层叠的硅衬底1、ain成核层2、algan缓冲层3、gan沟道层4、algan势垒层,algan势垒层包括从下而上依次层叠的第一algan势垒层5、第二algan势垒层6、第三algan势垒层7,第三algan势垒层7上表面设有凹槽且凹槽沿第三algan势垒层7伸入第二algan势垒层6中,凹槽的槽底和槽壁上设有栅介质层14,栅介质层14底部设有两个栅极11、12,其中靠近漏极8的栅极11设有栅场板,两个栅极11、12之间设有阻挡层15且阻挡层15向下穿过栅介质层14延伸至gan沟道层4,第三algan势垒层7上表面两侧分别设有源极13和漏极8,源极13上设有源场板10,第三algan势垒层7上表面位于源极13和漏极8之间设有钝化层9。

24.所述第二algan势垒层6、第一algan势垒层5、第三algan势垒层7中铝组分(铝的摩尔比)分别为0.03、0.15、0.25, algan缓冲层3铝组分与第二algan势垒层6铝组分相同。

25.所述algan缓冲层3的厚度为1~2μm,gan沟道层4的厚度为10~20nm,第一algan势垒层5的厚度为2~10nm,第二algan势垒层6的厚度为10nm,第三algan势垒层7的厚度为25nm。

26.所述钝化层为sin,厚度为2μm。

27.所述栅介质层14为al2o3,厚度为10~20nm。

28.所述阻挡层15为sin,宽度为0.2μm,深度为37nm。

29.所述源极13和漏极8为ti/al/ni/au欧姆接触复合金属层,所述栅极为ni/au肖特基接触复合金属层。

30.一种mis分裂栅gan基高电子迁移率晶体管的制备方法,其特征在于,步骤如下:1)对硅衬底1进行热处理和表面氮化。

31.2)在氮化后的硅衬底1表面依次生长ain成核层2、algan缓冲层3、gan沟道层4、第一algan势垒层5、第二algan势垒层6、第三algan势垒层7,形成外延片。

32.采用金属有机化学气相沉积法在硅衬底1上外延厚度为1nm的ain成核层2,然后外延厚度为2μm的algan缓冲层3,其中algan缓冲层3铝组分为0.07,在缓冲层之上继续外延gan沟道层4,沟道层厚度10~20nm,接着外延第一algan势垒层5、第二algan势垒层6、第三algan势垒层7,第一algan势垒层5、第二algan势垒层6、第三algan势垒层7铝组分分别为0.15、0.03、0.25,厚度分别为5nm、15nm、25nm。

33.3)刻蚀形成源极区域、漏极区域以及凹槽栅区域:在第三algan势垒层7上,从源极至漏极方向,依次完全刻蚀宽1μm的源极区域,间隔1μm之后刻蚀凹槽栅区域,宽度为1.6μm,深度为30nm,接着间隔15μm刻蚀宽1μm漏极区域。

34.4)在凹槽栅区域沉积栅介质层14:采用氧化铝作为栅极介质,在凹槽中沉积厚度为10~20nm的al2o3栅介质层14。

35.5)在源极区域和漏极区域沉积欧姆接触金属层,以形成源极13和漏极8:在暴露的第三algan势垒层7上采用电子束蒸发器沉积ti/al/ni/au/四层欧姆接触金属,沉积完毕后利用电感耦合等离子刻蚀系统实现mesa分离,超声清洗氮气,将源、漏窗口以外金属剥离,然后进行30s欧姆接触退火,形成源极13和漏极8。

36.6)在栅区域沉积金属层形成栅极:用电子束蒸发法沉积ni/au两层金属,退火后形成栅极。

37.7)沉积钝化层:通过等离子体增强化学气相沉积法沉积sin钝化层。

38.8)刻蚀阻挡区,沉积阻挡层15:通过反应离子蚀刻去除位于双栅极之间的sin,双栅之间的al2o3栅介质层14用氢氟酸除去,然后用等离子干法刻蚀algan势垒层,最后沉积sin阻挡层15。

39.9)在栅极沉积栅场板金属,在源极13沉积源场板10金属。

40.10)再次沉积钝化层:在已形成源漏栅极结构的表面上,光刻获得加厚电极图案,采用电子束蒸发技术加厚电极,完成器件制造。

41.仿真例1、阈值电压仿真测试在tcad仿真环境中,设定在漏极电压10v的条件下,栅压从

‑

1v扫到30v,如图2所示,阈值电压为8v,相较于其他凹槽栅结构高电子迁移率晶体管的阈值电压有很大的提升。

42.2、输出特性仿真测试在tcad仿真环境中,依次在栅压为7v、8v、9v、10v、11v、12v、13v、14v的条件下,漏极电压从0v扫到40v,如图3所示,在栅压为14v时,最大漏极饱和电流达到0.3a/mm。由此可以看出本发明所提出的结构,随着阈值电压的大幅提高,最大漏极饱和电流并没有受限。

43.3、击穿特性仿真测试在tcad仿真环境中,在本发明所提出的结构上,不加场板,器件的耐压只达到几百伏特,通过栅极场板和源极场板相结合,有效地避免了电场集中,进而器件的耐压能力达到了1400v,如图4所示。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1