晶体管结构及其相关制造方法与流程

1.本发明是涉及一种晶体管结构及其相关制造方法,尤其涉及一种具有可准确控制源极/漏极和接触开口的长度以有效缩小尺寸的晶体管结构及其相关制造方法。

背景技术:

2.因为在1974年,由r.dennard等人所发表的论文中,公开了缩小金属氧化物半导体场效应晶体管(metal

‑

oxide

‑

semiconductor field

‑

effect transistor,(mosfet))的所有尺寸的设计准则,所以如何缩小晶体管的尺寸成为主要的技术需求,其中所述主要的技术需求已改变硅晶圆的线性尺寸的最小特征尺寸从几微米(μm)缩小到几纳米(nm)。所述最小特征尺寸或长度通常称为lamda(λ),是取决于使用光刻光罩技术(photolithographic masking technology)及组件缩小技术的微型化能力(为了简化说明和对照,通过最小化印刷线宽分辨率所测量的也称为λ)。但是另一个限制了组件缩小的难以控制的因素是光刻设备的不足与不准确所造成的错位公差(misalignment tolerance),也就是delta

‑

lamda(δλ)。另外,因为所述错位公差,所以所述晶体管的栅极边缘到源极(或漏极)边缘之间的距离很难做到小于λ和δλ的总和。之后,如果再次需要通过使用所述光刻光罩技术在所述漏极(或源极)上制造一个方形的接触孔以做为未来金属互连到所述漏极(或所述源极)之间的连接,则所述接触孔的每个边的最小尺寸很难做到小于λ。另外,为确保在所述漏极之内的接触孔包含错位公差,所述漏极(具有长方形的外围)的每个边的长度也很难做到小于λ和δλ的总和。然而,缩小晶体管的尺寸对于在一个硅晶圆的一个平面区域之内整合更多的晶体管是必要的,以及分别缩小晶体管的漏极和源极所占的面积是达成上述目标的一个必要且有效的方式,其也有助于减少漏电流和功耗。

3.因此,如何有效的缩小晶体管的尺寸以在所述硅晶圆的所述平面区域之内整合更多的晶体管已成为所述晶体管的设计者所要解决的一个重要问题。

技术实现要素:

4.本发明的一实施例公开一种晶体管的制造方法,其中所述晶体管包含一栅极结构以及一第一导电区。所述制造方法包含在一基底上形成一主动区;在所述主动区上方形成所述栅极结构和一伪屏蔽栅极结构(dummy shield gate structure);形成一第一隔离区以取代所述伪屏蔽栅极结构;在所述主动区上方形成一自对准柱(self

‑

alignment pillar);以及移除所述自对准柱,并且在所述栅极结构和所述第一隔离区之间形成所述第一导电区。

5.在本发明的另一个实施例中,在移除所述自对准柱的步骤之前,所述制造方法另包含在所述第一隔离区上方形成一第二隔离区,其中所述自对准柱位于所述栅极结构和所述第二隔离区之间。

6.在本发明的另一个实施例中,在移除所述自对准柱的步骤之后,所述制造方法另包含在所述栅极结构和所述第一隔离区之间形成一间隔层以定义一接触孔,其中所述接触

孔位于所述第一导电区上方。

7.在本发明的另一个实施例中,所述接触孔的长度小于一最小特征长度(minimum feature length)。

8.在本发明的另一个实施例中,所述基底是一硅基底,以及所述自对准柱是通过选择性外延生长(selective epitaxy growth)形成的一本质硅柱(intrinsic silicon pillar)。

9.本发明的另一实施例公开一种晶体管的制造方法,其中所述晶体管包含一栅极结构以及一第一导电区。所述制造方法包含在一基底上形成一主动区;在所述主动区上形成所述栅极结构;以及形成一自对准柱,其中所述自对准柱是用以在所述第一导电区上方分配一接触孔。

10.在本发明的另一个实施例中,所述制造方法另包含在形成所述自对准柱之前,在所述主动区上形成一隔离区。

11.在本发明的另一个实施例中,所述制造方法另包含移除所述自对准柱,其中所述自对准柱是形成在所述栅极结构和所述隔离区之间;以及在所述栅极结构和所述隔离区之间形成一间隔层以定义一接触孔,其中所述接触孔位于所述第一导电区上方。

12.在本发明的另一个实施例中,所述接触孔的长度小于一最小特征长度。

13.本发明的另一实施例公开一种晶体管的制造方法,其中所述晶体管包含一栅极结构以及一第一导电区。所述制造方法包含在一基底上形成一主动区;在所述主动区上方形成所述栅极结构;在所述栅极结构旁边形成所述第一导电区;以及在所述第一导电区上方定义一接触孔,其中定义所述接触孔是与一光刻(photolithography)工艺无关。

14.在本发明的另一个实施例中,所述第一导电区是形成在所述栅极结构和一隔离区之间,其中所述隔离区在所述主动区上方向上延伸。

15.在本发明的另一个实施例中,所述接触孔是通过形成一间隔层来定义,其中所述间隔层覆盖所述栅极结构的一侧壁以及所述隔离区的一侧壁。

16.在本发明的另一个实施例中,所述接触孔的长度小于一最小特征长度。

17.本发明的另一实施例公开一种晶体管的制造方法,其中所述晶体管包含一栅极结构以及一第一导电区。所述制造方法包含实施一第一光刻工艺,其中所述第一光刻工艺是用以定义所述栅极结构的宽度和一主动区的长度;实施一第二光刻工艺,其中所述第二光刻工艺是用以定义所述栅极结构在所述主动区内的长度,其中所述第二光刻工艺另用以定义所述第一导电区的长度。

18.在本发明的另一个实施例中,通过所述第二光刻工艺定义的所述第一导电区的长度等于或实质上等于一最小特征长度。

19.在本发明的另一个实施例中,通过所述第二光刻工艺定义的所述栅极结构的长度等于或实质上等于一最小特征长度。

20.在本发明的另一个实施例中,通过所述第一光刻工艺定义的所述主动区的长度大约等于一最小特征长度的4倍。

21.本发明的另一实施例公开一种晶体管的制造方法,其中所述晶体管包含一栅极结构以及一第一导电区。所述制造方法包含在一基底上形成一主动区;在所述主动区上形成所述栅极结构;在所述栅极结构旁边形成所述第一导电区;以及在所述第一导电区上方形

成一接触孔,其中所述接触孔的形状不需通过一光刻工艺定义。

22.在本发明的另一个实施例中,所述第一导电区是形成在所述栅极结构和一隔离区之间。

23.在本发明的另一个实施例中,所述接触孔是通过形成一间隔层来定义,其中所述间隔层覆盖所述栅极结构的一侧壁以及所述隔离区的一侧壁。

24.在本发明的另一个实施例中,所述接触孔的长度小于一最小特征长度。

25.本发明的另一实施例公开一种晶体管结构。所述晶体管结构包含一半导体基底、一栅极结构、一信道区、一第一导电区以及一接触孔。所述半导体基底具有一半导体表面。所述栅极结构具有一长度。所述第一导电区电耦接所述通道区。所述接触孔位于所述第一导电区上方。其中所述接触孔的周边被所述第一导电区的外围包围。

26.在本发明的另一个实施例中,所述第一导电区的所述外围是一长方形。

27.在本发明的另一个实施例中,所述接触孔的长度小于一最小特征长度。

28.本发明的另一实施例公开一种晶体管结构。所述晶体管结构包含一半导体基底、一栅极结构、一信道区、一第一导电区以及一接触孔。所述半导体基底具有一半导体表面。所述信道区位于所述栅极结构下方。所述接触孔位于所述第一导电区上方。其中所述接触孔的长度小于一最小特征长度。

29.在本发明的另一个实施例中,在所述栅极结构的一侧壁和所述接触孔的一侧壁之间的一水平距离小于所述最小特征长度,其中所述接触孔的所述侧壁是远离所述栅极结构的侧壁。

30.在本发明的另一个实施例中,在所述栅极结构的一侧壁和所述第一导电区的一侧壁之间的一水平距离大约等于所述最小特征长度,其中所述第一导电区的所述侧壁是远离所述栅极结构的侧壁。

31.本发明的另一实施例公开一种晶体管结构。所述晶体管结构包含一半导体基底、一栅极结构、一信道区、一第一隔离区、一第一间隔层、一第二间隔层、一第一导电区以及第一接触孔。所述半导体基底具有一半导体表面。所述栅极结构具有一长度。所述通道区位于所述半导体表面下方。所述第一隔离区从所述半导体表面向上及向下延伸。第一间隔层覆盖所述栅极结构的一第一侧壁,以及所述第二间隔层覆盖所述第一隔离区的一侧壁。所述第一导电区电耦接所述通道区,且位于所述栅极结构和所述第一隔离区之间。所述第一接触孔形成在所述第一间隔层和所述第二间隔层之间。

32.在本发明的另一个实施例中,所述晶体管结构另包含一覆盖层以及一第一金属区。所述覆盖层覆盖所述栅极结构。所述第一金属区填充在所述第一接触孔内且接触所述第一导电区,所述第一金属区从所述第一导电区向上延伸至一预定位置,其中所述预定位置高于所述覆盖层的顶部。

33.在本发明的另一个实施例中,所述第一金属区的宽度实质上等于所述第一接触孔的长度加上一最小特征长度。

34.在本发明的另一个实施例中,所述晶体管结构另包含一第二隔离区以及一第二导电区。所述第二隔离区从所述半导体表面向上及向下延伸。第二导电区电耦接所述通道区,且位于所述栅极结构和所述第二隔离区之间。

35.在本发明的另一个实施例中,在所述栅极结构的一第二侧壁和所述第二隔离区的

一侧壁之间的一水平距离实质上等于一最小特征长度,其中所述第一隔离区的所述侧壁是远离所述栅极结构的侧壁。

36.在本发明的另一个实施例中,所述晶体管结构另包含一第二接触孔。所述第二接触孔位于所述第二导电区上方,其中所述第二接触孔的长度小于一最小特征长度。

37.在本发明的另一个实施例中,所述晶体管结构另包含一第三间隔层以及一第四间隔层。所述第三间隔层覆盖所述栅极结构的一第二侧壁。所述第四间隔层覆盖所述第二隔离区的一侧壁,其中所述第二接触孔是形成在所述第三间隔层和所述第四间隔层之间。

38.本发明的另一实施例公开一种晶体管结构。所述晶体管结构包含一半导体基底、一栅极结构、一信道区、一第一导电区以及一第一隔离区。所述半导体基底具有一半导体表面。所述栅极结构具有一长度。所述第一导电区电耦接所述通道区。所述第一隔离区位于所述第一导电区旁边。其中所述第一导电区的长度是通过一单一光刻工艺所控制,其中且单一光刻工艺原本是用以定义所述栅极结构的长度。

39.在本发明的另一个实施例中,所述第一导电区的长度等于或实质上等于一最小特征长度。

40.本发明的另一实施例公开一种晶体管结构。所述晶体管结构包含一半导体基底、一栅极结构、一信道区、一第一导电区以及一第一接触孔。所述半导体基底具有一半导体表面。所述栅极结构具有一长度。所述第一导电区电耦接所述通道区。其中所述第一接触孔的周边与一光刻工艺无关。

41.在本发明的另一个实施例中,所述第一接触孔的长度小于一最小特征长度。

42.在本发明的另一个实施例中,所述第一导电区的长度等于或实质上等于所述最小特征长度。

43.在本发明的另一个实施例中,所述第一接触孔位于所述第一导电区上方。

附图说明

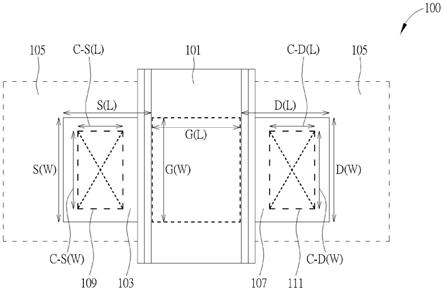

44.图1是本发明一实施例所公开的微型化的金属氧化物半导体场效应晶体管的俯视图。

45.图2a是本发明的另一实施例所公开的一微型化的金属氧化物半导体场效应晶体管的制造方法的流程图。

46.图2b

‑

2f是说明图2a的流程图。

47.图3是说明衬垫氮化层和浅沟槽隔离

‑

第一氧化层的俯视图。

48.图4是图3中沿x轴方向的横截面图。

49.图5是说明金属氧化物半导体场效应晶体管的栅极结构边缘到源极和浅沟槽隔离

‑

第一氧化层之间的边界边缘的对准的光刻错位公差(photolithographic misalignment tolerance,pmt))的示意图。

50.图6是说明可排除光刻错位公差所造成的负面影响的新结构的示意图。

51.图7是说明沉积旋涂介电层的示意图。

52.图8是说明沉积和蚀刻设计良好的栅极光罩层的示意图。

53.图9是说明通过异向性蚀刻技术移除伪屏蔽栅极、氮化层、介电绝缘体、以及对应伪屏蔽栅极的基底的示意图。

54.图10是说明移除栅极光罩层、蚀刻旋涂介电层、沉积第二氧化层以及回蚀所述第二氧化层以形成浅沟槽隔离

‑

第二氧化层的示意图。

55.图11

‑

14是说明真栅极的位置和伪屏蔽栅极的位置之间的关系的示意图。

56.图15是说明沉积以及蚀刻第三氧化层以形成第三氧化间隔层、在基底中形成轻掺杂漏极、沉积以及回蚀氮化层以形成氮化间隔层、以及移除介电绝缘体的示意图。

57.图16是说明利用选择性外延生长技术生成本质硅的示意图。

58.图17是说明沉积以及回蚀化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层、移除本质硅以及形成金属氧化物半导体场效应晶体管的源极和漏极的示意图。

59.图18是说明沉积以及蚀刻氧化间隔层以形成接触孔开口的示意图。

60.图19是说明沉积以及回蚀第一金属层以形成第一金属层互连的示意图。

61.图20是本发明的另一实施例所公开的使用合并的半导体接面和金属导体结构形成源极和漏极,以及形成第一金属层互连的示意图。

62.图21是说明移除栅极光罩层,以及沉积第二氧化层以填满沟槽和水平硅表面上的其他空缺以形成所述浅沟槽隔离

‑

第二氧化层,然后通过化学机械研磨技术平坦化所述浅沟槽隔离

‑

第二氧化层的示意图。

63.图22是说明沉积以及蚀刻第三氧化层以形成第三氧化间隔层、在基底中形成轻掺杂区、沉积以及回蚀氮化层以形成氮化间隔层、以及移除介电绝缘体的示意图。

64.图23是说明利用所述选择性外延生长技术生成本质硅的示意图。

65.图24是说明沉积以及蚀刻氧化间隔层以形成接触孔开口的示意图。

66.图25是说明沉积以及蚀刻第一金属层以形成第一金属层互连的示意图。

67.其中,附图标记说明如下:

68.100

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

金属氧化物半导体场效应晶体管

69.101

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极结构

70.103、1704、2402

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

源极

71.105、1102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

隔离区

72.107、1706、2404

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

漏极

73.109、111

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

接触孔

74.102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

基底

75.302

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

衬垫氧化层

76.304

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

衬垫氮化层

77.306

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

浅沟槽隔离

‑

第一氧化层

78.402

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

介电绝缘体

79.404、602

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极层

80.406、604

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

氮化层

81.702

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

旋涂介电层

82.802

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极光罩层

83.902

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

沟槽

84.1002、2102、sti

‑

oxide

‑2ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

浅沟槽隔离

‑

第二氧化层

85.1502、2202

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三氧化间隔层

86.1504、2204

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

轻掺杂漏极

87.1506、2206

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

氮化间隔层

88.1602、2302

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

本质硅

89.1702、2304

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层

90.1802、2406

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

氧化间隔层

91.1804

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一接触孔

92.1806

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二接触孔

93.1902、2502

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一金属层

94.1904、2504

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

最小空间

95.1906

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一半导体区

96.1908

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一内含金属区

97.1910

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二半导体区

98.1912

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二内含金属区

99.1914

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一氧化保护层

100.1916

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二氧化保护层

101.d(l)、g(l)、s(l)、c

‑

s(l)、c

‑

d(l)

ꢀꢀ

长度

102.d(w)、g(w)、s(w)、c

‑

s(w)、c

‑

d(w)

ꢀꢀ

宽度

103.gebesi、gebedi

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

距离

104.hss

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

水平硅表面

105.dsg

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

伪屏蔽栅极

106.tg、tg2、tg3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

真栅极

107.λ

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

最小特征长度

108.δλ

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

光刻错位公差

109.10

‑

70、202

‑

228

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

步骤

具体实施方式

110.本发明公开一种可准确控制晶体管的源极(或漏极)的线性尺寸的新方法,其中所述尺寸可小至最小特征尺寸lamda(λ),也就是说所述晶体管可不用加上错位公差delta

‑

lamda(δλ)而被印刷或制造在晶圆上(例如硅晶圆)。再者,在所述晶体管漏极(或源极)内可以实现线性尺寸小于λ的接触孔。因此,本发明产生了一种新具有最小特征尺寸的源极和漏极的结构,其中所述最小特征尺寸是从所述晶体管的栅极结构边缘到所述晶体管隔离区边缘旁的源极(或漏极)边缘,且在所述源极和所述漏极上具有线性尺寸小于λ的接触孔。因此,本发明可避免所述光刻光罩技术在形成所述源极和所述漏极时分别所造成的错位公差。

111.请参照图1。图1是本发明一实施例所公开的微型化的金属氧化物半导体场效应晶体管100的俯视图。如图1所示,金属氧化物半导体场效应晶体管100包含:(1)一栅极结构101,其中栅极结构101具有长度g(l)和宽度g(w),(2)在栅极结构101左边的是一源极103,其中源极103具有长度s(l)和宽度s(w),且长度s(l)是从栅极结构101的边缘到一隔离区105的边缘的线性尺寸,(3)在栅极结构101右边的是一漏极107,其中漏极107具有长度d(l)

和宽度d(w),且中长度d(l)是从栅极结构101的边缘到隔离区105的边缘的一线性尺寸,(4)在源极103的中央,是通过自对准技术(self

‑

alignment technology)所形成的接触孔109,其中接触孔109的长度和宽度分别为c

‑

s(l)和c

‑

s(w),(5)同样地,在漏极107的中央,是通过自对准技术所形成的接触孔111,其中接触孔111的长度和宽度分别为c

‑

d(l)和c

‑

d(w)。

112.要形成金属氧化物半导体场效应晶体管100,可利用一第一光刻工艺来定义宽度g(w)和一主动区的伪长度(pseudo length),以及可利用一第二光刻工艺来定义在所述主动区内的长度g(l),其中所述第二光刻工艺更可利用来控制栅极结构101和隔离区105之间的长度s(l),在本发明的一实施例中,通过所述第一光刻工艺所定义的所述主动区的伪长度大约为最小特征长度λ的4倍。在本发明的一实施例中,长度g(l)可以等于或实质上等于最小特征长度λ。当然在其他实施例中,长度g(l)可以大于最小特征长度λ。

113.本发明的第一个特征是长度s(l)和长度d(l)都可根据目标尺寸被准确的设计和定义,其中所述目标尺寸可被制造在晶圆(wafer)的表面上,而且不会被无法避免的光刻错位公差(photolithographic misalignment tolerances,pmt)所影响。

114.本发明的第二个特征是长度s(l)和长度d(l)都可和最小特征长度λ一样小,所述最小特征长度是在一工艺节点所定义的一特定工艺限制(例如,最小特征长度λ在7纳米节点是7纳米,或在28纳米节点是28纳米,或在180纳米节点是180纳米)。

115.本发明的第三个特征是如果长度g(l)是设计为λ,则沿着金属氧化物半导体场效应晶体管100的长度方向的最小尺寸(也就是从源极103的左边缘到漏极107的右边缘之间的距离)可以小到3λ(也就是1λ是长度s(l),1λ是长度d(l),以及1λ是长度g(l))。然后金属氧化物半导体场效应晶体管100沿着所述长度方向的线性尺寸可达到微型化,其他当金属氧化物半导体场效应晶体管100在沿着所述长度方向的线性尺寸不包含隔离区105时,金属氧化物半导体场效应晶体管100在沿着所述长度方向的线性尺寸减小至只有3λ。

116.本发明的第四个特征是长度s(l)和长度d(l)可以创造接触孔109的较窄的长度c

‑

s(l)和接触孔111的较窄的长度c

‑

d(l),而不用受到所述光刻错位公差的限制(因为制造接触孔109和接触孔111的大部分关键光罩步骤被排除了),其他长度s(l)和长度d(l)可被自对准技术(self

‑

alignment technology)所明确定义。再者,第一金属层(metal

‑

1)的沉积互连层可被所述光刻光罩技术(photolithographic masking technique)有效的定义以达到所述第一金属层较窄的宽度(也就是所述接触孔开口和所述光刻错位公差的两倍的总和),其中所述沉积互连层可以充分的填入接触孔109和接触孔111以制造分别连接所述第一金属层到源极103和漏极107天然的金属接触点。

117.如前述的发明,金属氧化物半导体场效应晶体管结构的最小组件长度尺寸(包含隔离区和所述第一金属层的互连)可以被微型化,而不用被无法避免的所述光刻错位公差扩大。

118.请参照图2a

‑

2f、3、4、6

‑

19。图2a是本发明的另一实施例所公开的一微型化的金属氧化物半导体场效应晶体管的制造方法的流程图。其中在图2a中的所述金属氧化物半导体场效应晶体管的制造方法可准确控制所述金属氧化物半导体场效应晶体管的源极和漏极的长度。所述制造方法的详细步骤如下:

119.步骤10:开始;

120.步骤20:在基底102上形成一主动区和一沟槽结构;

121.步骤30:在基底102的水平硅表面(horizontal silicon surface,hss)上形成伪屏蔽栅极(dummy shield gate)和所述金属氧化物半导体场效应晶体管的一真栅极(true gate);

122.步骤40:用隔离区取代所述伪屏蔽栅极以定义所述金属氧化物半导体场效应晶体管的源极/漏极的边界;

123.步骤50:形成所述金属氧化物半导体场效应晶体管的所述源极和所述漏极;

124.步骤60:在所述源极和所述漏极的边界内形成较小的接触孔,以及形成第一金属层互连以通过所述接触孔接触到所述源极或所述漏极;

125.步骤70:结束。

126.请参照图2b和图3、4。步骤20可包含:

127.步骤202:在基底102上形成一衬垫氧化层302以及沉积一衬垫氮化层304;

128.步骤204:定义所述金属氧化物半导体场效应晶体管的主动区,以及移除所述主动区外的部分硅材料以制造所述沟槽结构;

129.步骤206:在所述沟槽结构中沉积一第一氧化层,以及回蚀所述第一氧化层以在水平硅表面hss下方形成一浅沟槽隔离

‑

第一氧化层306(shallow trench isolation

‑

oxide

‑

1,sti

‑

oxide

‑

1);

130.步骤207:移除衬垫氧化层302和衬垫氮化层304,以及在水平硅表面hss上方形成一介电绝缘层402。

131.请参照图2c和图6。步骤30可包含:

132.步骤208:在水平硅表面hss上方沉积一栅极层602和一氮化层604;

133.步骤210:蚀刻栅极层602和氮化层604以形成所述金属氧化物半导体场效应晶体管的真栅极和伪屏蔽栅极,其中所述伪屏蔽栅极到所述真栅极之间具有一所需的线性距离。

134.请参照图2d和图7

‑

10。步骤40可包含:

135.步骤212:沉积一旋涂介电层(spin

‑

on dielectrics,sod)702,然后回蚀旋涂介电层702;

136.步骤214:通过所述光刻光罩技术形成一设计良好的栅极光罩层802;

137.步骤216:利用异向性蚀刻技术(anisotropic etching technique)移除伪屏蔽栅极dsg上的氮化层604,以及移除伪屏蔽栅极dsg、对应伪屏蔽栅极dsg的介电绝缘层402和对应伪屏蔽栅极dsg的基底102;

138.步骤218:移除栅极光罩层802,蚀刻旋涂介电层702,以及沉积一第二氧化层,然后回蚀所述第二氧化层以形成浅沟槽隔离

‑

第二氧化层1002。

139.请参照图2e和图15

‑

17。步骤50可包含:

140.步骤220:沉积以及回蚀一第三氧化层以形成一第三氧化间隔层1502,在基底102中形成轻掺杂漏极(lightly doped drain,ldd)1504,沉积以及回蚀一氮化层以形成一氮化间隔层1506,以及移除介电绝缘层402;

141.步骤222:利用一选择性外延生长(selective epitaxy growth,seg)技术生成一本质硅(intrinsic silicon)1602;

142.步骤224:沉积以及回蚀一化学气相沉积(chemical vapor deposition,cvd)

‑

浅

沟槽隔离

‑

第三氧化层1702,移除本质硅1602,以及形成所述金属氧化物半导体场效应晶体管的源极(n+源极)1704和漏极(n+漏极)1706。

143.请参照图2f和图18、19。步骤60可包含:

144.步骤226:沉积以及蚀刻一氧化间隔层1802以在源极(n+源极)1704和漏极(n+漏极)1706上形成接触孔开口(contact

‑

hole openings);

145.步骤228:沉积以及蚀刻一第一金属层1902以形成所述第一金属层互连。

146.第一部分:利用栅极光罩上添加的伪屏蔽栅极(dummy

‑

shield

‑

gate,dsg)并通过避免所述光刻错位公差以实现从所述栅极的边缘到所述源极和所述隔离区之间的边界边缘的设计距离gebesi。同样地,从所述栅极的边缘到所述漏极和所述隔离区之间的边界边缘也有一设计距离gebedi。

147.以n型金属氧化物半导体场效应晶体管为例,基底102可以是p型基底,前述制造方法的详细说明如下。从步骤20开始,请参照图2b和图3、4。在步骤202中,衬垫氧化层302在基底102的水平硅表面hss上方形成,然后在衬垫氧化层302上方沉积衬垫氮化层304。

148.在步骤204中,所述金属氧化物半导体场效应晶体管的主动区可以被所述光刻光罩技术定义,导致所述主动区外的水平硅表面hss被曝露。因为所述主动区外的水平硅表面hss被曝露,所以可通过所述异向性蚀刻技术移除所述主动区外的部分硅材料以制造所述沟槽结构。

149.在步骤206中,沉积所述第一氧化层以填满所述沟槽结构,然后回蚀所述第一氧化层被以在水平硅表面hss下方形成浅沟槽隔离

‑

第一氧化层306,如图4所示。图4是沿图3所示的x轴方向的横截面图。另外,因为图3是俯视图,所以图3只示出衬垫氮化层304和浅沟槽隔离

‑

第一氧化层306。然后,在步骤207中,在所述主动区上的衬垫氧化层302和衬垫氮化层304被移除,以及在水平硅表面hss上方形成介电绝缘层402(具有高介电常数)。

150.图5是说明以较小尺寸实现栅极与晶体管隔离区之间几何关系的现有技术的示意图。在水平硅表面hss上方形成介电绝缘层402之后,一栅极层404(金属栅极)沉积在介电绝缘层402上方。然后具有良好设计厚度的氮化层406(氮化帽层)沉积在栅极层404上。接着,如图5所示,利用所述光刻光罩技术来定义栅极结构1,其中栅极结构1包含栅极层404和氮化层406以使栅极结构1具有适当金属栅极材料,且所述金属栅极材料可提供金属绝缘体到基板102所需的功函数以实现所述金属氧化物半导体场效应晶体管合适的临界电压。另外,因为浅沟槽隔离

‑

第一氧化层306是形成在水平硅表面hss下方,所以可形成三栅极晶体管(tri

‑

gate fet)结构或鳍式场效应晶体管(fin field

‑

effect transistor,finfet)结构(如图5所示)。

151.在利用所述第一光刻工艺来定义所述主动区的一伪长度和利用所述第二光刻工艺来定义所述主动区的长度g(l)之后,从栅极结构1的边缘到所述金属氧化物半导体场效应晶体管的源极和所述浅沟槽隔离之间的边界边缘的距离(称为gebesi)可被定义(如图5所示)。同理从所述栅极结构的边缘到所述金属氧化物半导体场效应晶体管的漏极和所述浅沟槽隔离之间的边界边缘的距离(称为gebedi)也可被定义。

152.然而,如图5所示,在利用所述光刻光罩技术对准栅极结构1的边缘以及所述金属氧化物半导体场效应晶体管的源极(或所述金属氧化物半导体场效应晶体管的漏极)和浅沟槽隔离

‑

第一氧化层306之间的边界边缘时,会存在一无法避免的不理想因素,称为所述

光刻错位公差。如果沿所述x轴方向所测量的所述光刻错位公差的线性尺寸为δλ,则δλ应与受特定工艺节点可用的设备的光刻分辨率所规定的最小特征尺寸有关。例如,7纳米工艺节点应有的最小特征尺寸λ等于7纳米以及光刻错位公差δλ可为3.5纳米。因此,如果所述金属氧化物半导体场效应晶体管的源极(或所述金属氧化物半导体场效应晶体管的漏极)所想要的实际尺寸被定为λ(例如7纳米),则在现有技术的工艺方法中,所述金属氧化物半导体场效应晶体管的源极(或所述金属氧化物半导体场效应晶体管的漏极)的所需长度必须大于λ和δλ的总和(例如大于10.5纳米)。

153.因此,本发明利用一种新的结构来排除所述光刻错位公差所造成的负面影响。也就是说从所述栅极结构的边缘到所述金属氧化物半导体场效应晶体管的源极和所述浅沟槽隔离之间的边界边缘的距离gebesi(或从所述栅极结构的边缘到所述金属氧化物半导体场效应晶体管的漏极和所述浅沟槽隔离之间的边界边缘的距离gebedi)的任何尺寸都可以被实现,而不需要在沿所述金属氧化物半导体场效应晶体管的长度方向(也就是如图4、5所示的x轴方向)预留额外的尺寸给所述光刻错位公差。

154.在步骤208中,如图6所示,在水平硅表面hss上方形成介电绝缘层402之后,沉积栅极层602和氮化层604。然后在步骤210中,蚀刻栅极层602和氮化层604以形成所述栅极结构(其中栅极层602可以是所述金属氧化物半导体场效应晶体管的栅极结构)。图6所示的新结构和图5所示的结构之间主要的差异在于当所述金属氧化物半导体场效应晶体管的真栅极tg被所述光刻光罩技术定义时,平行于真栅极tg的伪屏蔽栅极dsg也可依需求被定义,以至于目标线性距离(例如λ,在7纳米工艺节点中为7纳米)可存在于伪屏蔽栅极dsg和真栅极tg之间,而不需要保留任何额外的尺寸(也就是δλ)给所述光刻错位公差。被设计在同一光罩上的伪屏蔽栅极dsg和真栅极tg可以同时在覆盖所述主动区的介电绝缘层402的顶部形成。另外,如图6所示,真栅极tg2、tg3是对应于其他金属氧化物半导体场效应晶体管。

155.接下来的步骤是说明如何利用提高至水平硅表面hss上方的隔离区取代伪屏蔽栅极dsg。在步骤212中,如图7所示,沉积旋涂介电层702,然后利用化学机械研磨(chemical mechanical polishing,cmp))技术回蚀旋涂介电层702以使旋涂介电层702的顶部与氮化层604的顶部一样高。

156.在步骤214中,如图8所示,沉积栅极光罩层802,然后通过所述光刻光罩技术蚀刻栅极光罩层802以完成覆盖真栅极tg、tg2、tg3但暴露出伪屏蔽栅极dsg的目标,其中暴露出的伪屏蔽栅极dsg分别在距离gebesi和距离gebedi的长度的中间具有安全的光刻错位公差δλ。

157.为了清楚说明,在图8中,在栅极光罩层802下的真栅极tg与左边的伪屏蔽栅极dsg之间的距离可标记为gebesi,以及在栅极光罩层802下的真栅极tg与右边的伪屏蔽栅极dsg之间的距离可标记为gebedi。因为在用接下来第9

‑

10图所示的隔离区替换伪屏蔽栅极dsg之后,图8中真栅极tg和伪屏蔽栅极dsg之间的距离将会变成从真栅极tg的边缘到所述金属氧化物半导体场效应晶体管的源极(或所述金属氧化物半导体场效应晶体管的漏极)和所述隔离区之间的边界边缘的距离,也就是之前在图5所述的gebesi(或gebedi)。

158.在步骤216中,如图9(a)所示,可利用所述异向性蚀刻技术来蚀刻伪屏蔽栅极dsg和对应伪屏蔽栅极dsg的氮化层604,还可用来蚀刻对应伪屏蔽栅极dsg的介电绝缘层402以到达水平硅表面hss。然后利用所述异向性蚀刻技术来移除位于水平硅表面hss下方的基底

102的硅材料以在水平硅表面hss下方形成一沟槽902,其中沟槽902的深度可以等于浅沟槽隔离

‑

第一氧化层306的底部的深度。因此,如图9(a)所示,分别在创造精准控制的距离gebesi和距离gebedi时避免了所述光刻错位公差。因为通过在同一光罩上的真栅极tg和伪屏蔽栅极dsg良好定义距离gebesi和距离gebedi的长度,所以图1所示的源极的长度s(l)和漏极的长度d(l)都可被良好的定义。也就是说所述单一光刻光罩技术不仅用来定义真栅极tg和伪屏蔽栅极dsg,还可用来控制距离gebesi和距离gebedi的长度。因此,长度s(l)和长度d(l)的尺寸可被准确地控制,甚至可以达到和最小特征尺寸λ一样小的最佳微型化尺寸。因为长度s(l)和长度d(l)可以等于λ,所以长度s(l)和长度d(l)实质上等于真栅极tg(也就是所述栅极结构)的长度。另外,图9(b)是对应图9(a)的俯视图。

159.在步骤218中,如图10(a)所示,移除栅极光罩层802和旋涂介电层702,然后沉积第二氧化层以填满沟槽902和水平硅表面hss的其他空缺,接着所述第二氧化层可被回蚀至和水平硅表面hss一样的表面高度以形成浅沟槽隔离

‑

第二氧化层1002。图10(b)是对应图10(a)的俯视图。

160.因此,暂时形成的伪屏蔽栅极dsg可以被浅沟槽隔离

‑

第二氧化层1002取代以定义所述源极/漏极的边界。然后可利用任何能形成轻掺杂漏极(lightly doped drain,ldd)、围绕真栅极tg的间隔层、所述源极以及所述漏极的现有技术来完成所述金属氧化物半导体场效应晶体管,其中可分别根据被准确控制的距离gebesi和距离gebedi形成所述源极和所述漏极。

161.第二部分:利用伪屏蔽栅极dsg设计原则,通过自适应的伪屏蔽栅极设计来分别达到距离gebesi和距离gebedi的目标长度以用于可变形状的主动区(在一主动区(aa)光罩上)。

162.因为晶体管的一隔离区的形状以及所述隔离区在所述晶体管和邻近晶体管之间的位置可能有相当多种(甚至在上述的实施例中也是如此),以下将描述另一种结构,其是通过扩展上述实施例的原理来设计一种自适应的伪屏蔽栅极。

163.图11是说明一种邻近晶体管的主动区的布置几何条件,其中所述邻近晶体管的主动区的布置几何条件是不同于图6。例如,如图6所示,在真栅极tg、真栅极tg2、真栅极tg3和伪屏蔽栅极dsg沉积之前,邻近晶体管的相邻主动区是相连的。然后可通过伪屏蔽栅极dsg的长度将相连的主动区分割成个别的精确目标距离。但是如图11所示,假设在晶体管的真栅极被定义之前和之后,在所述晶体管的源极(或漏极)上的主动区已经通过隔离区1102与任何其他主动区完全隔离的。因此,如下所述,在此要提出的是如何设计在源极上的主动区以及自适应的伪屏蔽栅极dsg(漏极也是如此)。例如,如果距离gebesi的最后长度定订为λ(或任何其他目标长度l(s)),则对应于距离gebesi的主动区光罩(aa mask)的长度应设计为等于λ和δλ的总和(或长度l(s)和δλ的总和)。然后在栅极光罩上,伪屏蔽栅极dsg可以具有如图11所示的形状,也就是说伪屏蔽栅极dsg的矩形形状的长度等于λ,宽度等于所述主动区的宽度与2δλ之总和(每边分别共享0.5δλ)。另外,在所述源极侧上的真栅极tg和伪屏蔽栅极dsg之间的设计距离仍然正好是距离gebesi的长度(例如λ)。

164.从图11的主动区和栅极的光罩阶段到晶圆阶段所导出的结果将描绘在图12。如图12所示,当真栅极tg被所述光刻光罩技术定义时,伪屏蔽栅极dsg被设计平行于真栅极tg,且伪屏蔽栅极dsg和真栅极tg之间具有一目标距离(例如λ,其中λ在7纳米工艺节点为7纳

米)。经过名义上工艺的结果(也就是没有明显的错位被引入在所述光刻工艺中),伪屏蔽栅极dsg覆盖了距离δλ的所述主动区(对应于所述源极),且真栅极tg和伪屏蔽栅极dsg都被设置在覆盖所述主动区的介电绝缘层402的上方。另外,在真栅极tg和伪屏蔽栅极dsg的上方都有氮化帽层(也就是氮化层604)。

165.如图13所示,如果所述光刻错位公差对真栅极tg和伪屏蔽栅极dsg都造成往所述主动区右边的位移(例如δλ),则接下来的工艺是移除伪屏蔽栅极dsg以实现隔离区sti

‑

oxide

‑

2(也就是浅沟槽隔离

‑

第二氧化层1002),其中隔离区sti

‑

oxide

‑

2的位置恰好是在第一部份的工艺步骤中所描述的原先存在的伪屏蔽栅极dsg的位置。另外,所述接下来的工艺可以使隔离区sti

‑

oxide

‑

2的长度为λ,且隔离区sti

‑

oxide

‑

2可成为所述源极的物理几何形状,其中真栅极tg和所述源极之间的距离gebesi的长度等于λ(因为真栅极tg和伪屏蔽栅极dsg之间的距离被设计为λ)。另一方面,如图14所示,如果所述光刻错位公差对真栅极tg和伪屏蔽栅极dsg都造成往所述主动区左边的位移(例如δλ),则接下来用于移除伪屏蔽栅极dsg和形成隔离区sti

‑

oxide

‑

2的工艺步骤,将会使隔离区sti

‑

oxide

‑

2的长度为λ,以及使真栅极tg和所述源极之间的距离gebesi的长度还是等于λ。

166.当所述光刻错位公差造成沿所述主动区的宽度方向(也就是上下方向)的不良位移时,则自适应的伪屏蔽栅极的设计(所述伪屏蔽栅极的宽度为所述主动区的宽度和2δλ的总和)不会影响所述主动区的几何尺寸。这种使用自适应的伪屏蔽栅极的创新设计总是产生具有长度λ的隔离区sti

‑

oxide

‑

2,并且产生距离gebesi的长度符合设计目标(例如λ)。本发明可以肯定地分别应用于具有各自目标长度的所有不同形状的隔离区、源极和漏极。

167.第三部分:精确定义的源极(或漏极)可通过自对准间隔层使接触孔开口(contact

‑

hole opening)被精确控制以减少接触光罩和开孔工艺的步骤。

168.在公开如何将距离gebesi和距离gebedi最佳地设计与制造成到精确控制的小尺寸(可小至λ)之后,另一个新的发明是如何分别制造具有长度c

‑

s(l)和长度c

‑

d(l)的接触孔开口,其中长度c

‑

s(l)和长度c

‑

d(l)分别小于距离gebesi和距离gebedi。以下将说明两种设计和工艺。

169.a.设计和工艺(i)

170.请继续参照图10(a)并且使用真栅极tg来做以下说明。在步骤220中,如图15(a)所示,沉积以及回蚀所述第三氧化层以形成第三氧化间隔层1502,其中第三氧化间隔层1502覆盖真栅极tg。接着,在基底102中形成轻掺杂区,并且在所述轻掺杂区上执行快速热退火(rapid thermal annealing,rta)以在真栅极tg旁边形成轻掺杂漏极1504。然后沉积以及回蚀所述氮化层以形成氮化间隔层1506,其中氮化间隔层1506覆盖第三氧化间隔层1502。接着移除没有被氮化间隔层1506和第三氧化间隔层1502覆盖的介电绝缘层402。另外,图15(b)是对应图15(a)的俯视图。

171.在步骤222中,如图16(a)所示,通过使用露出的水平硅表面hss作为硅晶种,利用所述选择性外延生长技术只在露出的水平硅表面hss上方生成本质硅1602,并且本质硅1602的高度与氮化层604(在真栅极tg的顶部上方)的顶部一样高。另外,图16(b)是对应图16(a)的俯视图。

172.在步骤224中,如图17(a)所示,沉积化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层1702以填满所有空缺,并且通过化学机械研磨(chemical

‑

mechanical polishing,cmp)技术平

坦化化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层1702以使化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层1702的高度和氮化层604的顶部平齐,其中氮化层604在真栅极tg的顶部上方。接着,移除本质硅1602,以便暴露出对应所述源极和所述漏极的水平硅表面hss,其中对应所述源极和所述漏极的水平硅表面hss被化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层1702和氮化间隔层1506围绕。

173.本质硅1602就像一自对准柱(self

‑

alignment pillar)一样用来围住或封住之后将被配置一接触孔的区域,但所述自对准柱并不受限于硅材料。根据用于所述选择性外延生长技术的晶种的材料,所述自对准柱可以是金属材料或其他半导体材料(例如:碳化硅(sic)、硅锗(sige)、(氮化镓gan)等)。另外,基底102可以是硅基底、碳化硅基底、硅锗基底、或氮化镓基底等。

174.任何能形成所述金属氧化物半导体场效应晶体管的源极(n+源极)1704和漏极(n+漏极)1706的现有技术都可用水平硅表面hss来实现源极1704和漏极1706的平坦面,其中源极(n+源极)1704可以是一第一导电区,以及漏极(n+漏极)1706可以是一第二导电区。另外,如图17(a)所示,一通道区(channel region)存在于轻掺杂漏极1504之间且在水平硅表面hss下方,以及所述通道区可电耦接源极(n+源极)1704和漏极(n+漏极)1706。另外,如图17(a)所示,源极(n+源极)1704是被置放在所述栅极结构(也就是真栅极tg(栅极层602))以及在所述栅极结构左边的浅沟槽隔离

‑

第二氧化层1002和化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层1702之间,其中在所述栅极结构左边的浅沟槽隔离

‑

第二氧化层1002和化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层1702可称为一第一隔离区,以及所述第一隔离区与所述第一导电区(也就是源极(n+源极)1704)相邻。另外,如图17(a)所示,漏极(n+漏极)1706是被置放在所述栅极结构以及在所述栅极结构右边的浅沟槽隔离

‑

第二氧化层1002和化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层1702之间,其中在所述栅极结构右边的浅沟槽隔离

‑

第二氧化层1002和化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层1702可称为一第二隔离区,以及所述第二隔离区与所述第二导电区(也就是漏极(n+漏极)1706)相邻。另外,如图17(a)所示,非常明显地可以知道所述第一隔离区和所述第二隔离区是从水平硅表面hss向上以及向下延伸。另外,图17(b)是对应图17(a)的俯视图。

175.在步骤226中,如图18(a)所示,因为在所述隔离区(也就是所述第一隔离区和所述第二隔离区)上的化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层1702和围绕真栅极tg的氮化间隔层1506比水平硅表面hss高,像是四个侧壁一样,所以设计良好的氧化间隔层1802(称为用于接触孔的氧化间隔层(oxide spacer for contact hole,oxide

‑

sch))可以被制造在四个侧壁外以形成一第一接触孔1804,其中第一接触孔1804的位置是在所述第一导电区(也就是源极(n+源极)1704)上方,并且在源极(n+源极)1704的边界内。同样地,一第二接触孔1806的位置是在所述第二导电区(也就是漏极(n+漏极)1706)上方,并且在漏极(n+漏极)1706的边界内。因此,如图18(a)所示,第一接触孔1804和第二接触孔1806是以一自对准的方式自然的形成,而不需要利用任何蚀刻技术来制造所述接触孔开口,并且通过所述用于接触孔的氧化间隔层的合适设计(具有厚度tosch)使所述接触孔开口的长度可分别小于距离gebesi和距离gebedi的长度。本发明创新的部分是在于所述接触孔开口的位置几乎是在源极1704(或漏极1706)的边界的中央,并且所述接触孔开口的长度可以被设计成小于λ(因为所述接触孔开口的长度=距离gebesi的长度

‑

厚度tosch的2倍。因此例如,如果厚度

tosch=0.2λ,距离gebesi的长度=λ,则所述接触孔开口的长度=0.6λ)。因此,因为所述接触孔开口的长度主要是被氧化间隔层1802的厚度tosch所支配,所以第一接触孔1804(和第二接触孔1806)的周边是与所述光刻光罩技术无关的,并且如图18(b)所示,可以明显看出第一接触孔1804的周边是在所述第一导电区的外围内,以及第二接触孔1806的周边是在所述第二导电区的外围内。

176.另外,如图18(b)所示,因为所述接触孔开口的长度小于λ,所以第一接触孔1804的长度(第二接触孔1806的长度)小于所述栅极结构的长度(因为如图6所示,所述栅极结构的长度等于λ)。另外,如图18(a)所示,因为氧化间隔层1802具有厚度tosch,并且距离gebesi的长度等于所述栅极结构的长度,所以很明显的所述栅极结构的一第一侧壁(位于所述栅极结构的左边)和第一接触孔1804远离所述栅极结构的一侧壁之间的水平距离会小于所述栅极结构的长度(也就是λ)。另外,如图18(a)所示,所述栅极结构的第一侧壁和所述第一导电区(也就是源极1704)远离所述栅极结构的一侧壁之间的水平距离大约等于所述栅极结构的长度。类似地,如图18(a)所示,所述栅极结构的一第二侧壁(位于所述栅极结构的右边)和所述第二隔离区远离所述栅极结构的一侧壁之间的水平距离实质上等于所述栅极结构的长度。

177.另外,如图18(a)所示,位于所述栅极结构左边且靠近所述栅极结构的氧化间隔层1802(也就是一第一间隔层)覆盖所述栅极结构的第一侧壁,以及位于所述栅极结构左边且远离所述栅极结构的氧化间隔层1802(也就是一第二间隔层)覆盖所述第一隔离区的一侧壁,其中第一接触孔1804是在所述第一间隔层和所述第二间隔层之间形成。

178.另外,如图18(a)所示,位于所述栅极结构右边且靠近所述栅极结构(例如一第三间隔层)的氧化间隔层1802覆盖所述栅极结构的一第二侧壁(位于所述栅极结构的右边),位于所述栅极结构右边且离所述栅极结构较远(例如一第四间隔层)的氧化间隔层1802覆盖所述第二隔离区的一侧壁,其中第二接触孔1806是在所述第三间隔层和所述第四间隔层之间形成。

179.另外,如图18(b)所示,显然地第一接触孔1804的周边被所述第一导电区(或源极1704)的外围包围,第一接触孔1804的周边的形状类似所述第一导电区的外围的形状,以及所述第一导电区外围是类似长方形的形状。另外,类似的情况也适用于第二接触孔1806和所述第二导电区(或漏极1706)。

180.根据本发明,自对准接触孔(第一接触孔1804和第二接触孔1806)展示了最小的接触孔长度(其尺寸可小于λ),其比任何现有技术的设计和通过所述光刻光罩技术及复杂蚀刻工艺所制造出来的接触孔开口的长度都还要小。另外,本发明省略了大部分难以控制的因素以及大部分用来定义和制造第一金属层接触(例如分别用于源极1704和漏极1706的第一接触孔1804和第二接触孔1806)的昂贵的光罩和后续钻挖所述接触孔开口的任务。另外,图18(b)是对应图18(a)的俯视图。

181.在步骤228中,如图19所示,在沉积第一金属层1902以填满所述接触孔(第一接触孔1804和第二接触孔1806)后,可以用所述光刻光罩技术来定义第一金属层1902。如图19所示,第一金属层1902必须具有精确控制尺寸的宽度,其中第一金属层1902的宽度必须能完全覆盖所述接触孔开口,并且要预留给任何无法避免的光刻错位公差。也就是说对应源极1704的第一金属层1902的宽度等于所述接触孔开口(在源极1704上)的长度c

‑

s(l)加上2δ

λ,以及对应漏极1706的第一金属层1902的宽度等于所述接触孔开口(在漏极1706上)的长度c

‑

d(l)加上2δλ。如果所述接触孔开口的长度可以控制在0.6λ(其可被控制,因为由前述说明的计算可得知所述接触孔内的氧化间隔层1802的尺寸可被良好控制),则第一金属层1902的宽度可以小至所述接触孔开口的长度和2δλ的总和(如果在本发明一实施例中,δλ=0.5λ(也就是所述栅极结构的长度的一半),所述接触孔开口的长度=0.6λ,则为了在无法避免的光刻错位公差下还能完全覆盖所述接触孔开口,第一金属层1902的宽度可以窄至1.6λ。也就是说为了在无法避免的光刻错位公差下能完全覆盖所述接触孔开口,第一金属层1902的宽度可以等于第一接触孔1804的长度加上所述栅极结构的长度)。根据本发明,窄至1.6λ的第一金属层1902的宽度可以是第一金属层互连的最小宽度之一。另外,在两个最靠近的第一金属层互连之间的一最小空间1904不能小于λ。另外,如图19所示,第一金属层1902(也就是一第一金属区)填充在第一接触孔1804中且接触所述第一导电区(也就是源极1704),其中所述第一金属区从所述第一导电区向上延伸至一预定位置,且所述预定位置是高于氮化层604(也就是所述氮化帽层)的顶部。

182.另外,如图20所示,如果没有用于源极(和/或漏极)的相邻的第一金属层互连,例如,使用合并的半导体接面和金属导体结构(merged semiconductor junction and metal conductor(msmc)structure)(公开于美国专利申请号16/991,044,申请日2020/08/12,在此全文引用),则由伪屏蔽栅极所定义的化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层1702的宽度可被制成和最小特征尺寸λ一样小,而不用被任何相邻的第一金属层互连之间的空间所限制,其中所述源极(和/或漏极)是接地和直接连接到所述金属氧化物半导体场效应晶体管的基底102。另外,如图20所示,所述源极包含一第一半导体区(n+重掺杂半导体区)1906和一第一内含金属区1908,所述漏极包含一第二半导体区(n+重掺杂半导体区)1910和一第二内含金属区1912,其中一第一氧化保护层(oxide guard layer,ogl)1914只覆盖第一内含金属区1908的一侧壁,而没有覆盖第一内含金属区1908的底部,一第二氧化保护层1916(在图20所示的凹槽中)覆盖所述第二内含金属区1912的一侧壁和底部。因此,第一内含金属区1908通过第一内含金属区1908的底部耦接至基底102。

183.本发明重要的优点在于几乎每个关键的尺寸,例如距离gebesi和距离gebedi的长度、所述接触孔开口的长度、和所述第一金属层互连的宽度都可以被精确的控制,而不受不确定的光刻错位公差所影响。如此,基于关键尺寸的一致性,可以确保每个关键的尺寸的重复性、质量和可靠性。

184.b.设计和工艺(ii)

185.上述的原理在接下来的实施例里会继续采用,但不同点在于如何形成所述间隔层和所述接触孔开口。接续图9(a),如图21(a)所示,移除栅极光罩层802,接着沉积所述第二氧化层以填满沟槽902和水平硅表面hss上方的其他空缺以形成一浅沟槽隔离

‑

第二氧化层2102。然后通过所述化学机械研磨技术平坦化浅沟槽隔离

‑

第二氧化层2102以使浅沟槽隔离

‑

第二氧化层2102的顶部和旋涂介电层702的顶部以及氮化层604的顶部平齐,其中氮化层604在真栅极tg上方。另外,图21(b)是对应图21(a)的俯视图。

186.然后如图22(a)所示,移除旋涂介电层702。接着沉积所述第三氧化层,以及利用所述异向性蚀刻技术回蚀所述第三氧化层以形成一第三氧化间隔层2202,其中第三氧化间隔层2202覆盖真栅极tg。然后在基底102中形成轻掺杂区,并且在所述轻掺杂区上执行快速热

退火以在真栅极tg旁边形成所述轻掺杂漏极2204。然后沉积以及回蚀所述氮化层以形成一氮化间隔层2206,其中氮化间隔层2206覆盖第三氧化间隔层2202。接着移除在原先存在的旋涂介电层702之下的介电绝缘层402。另外,图22(b)是对应图22(a)的俯视图。

187.接着如图23(a)所示,通过使用露出的水平硅表面hss区域作为硅晶种,利用所述选择性外延生长技术只在露出的水平硅表面hss上方生成一本质硅2302,其中本质硅2302的高度与氮化层604的顶部平齐,以及氮化层604在真栅极tg的顶部上方。和前述第三部分的段落a不同的是通过所述选择性外延生长的本质硅2302的形状可以更好的被控制,因为本质硅2302的两边被夹在浅沟槽隔离

‑

第二氧化层2102和真栅极tg之间,以及本质硅2302的另外两边面对着所述主动区的崖壁边缘上方的空气,其中所述主动区仍然被介电绝缘层402覆盖并且在相邻的浅沟槽隔离

‑

第一氧化层306(sti

‑

oxide

‑

1)的上方。然后沉积一化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层2304(如图23(b)所示)以填满所有空缺,且通过所述化学机械研磨技术平坦化使化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层2304的顶部和氮化层604(在真栅极tg的顶部上方)的顶部平齐。另外,图23(b)是对应图23(a)的俯视图。

188.另外,如图24(a)所示,移除本质硅2302以曝露出对应一源极(n+源极)2402和对应一漏极(n+漏极)2404区域的水平硅表面hss,其中源极2402和漏极2404被化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层2304的两壁,在浅沟槽隔离

‑

第二氧化层2102上的氮化间隔层2206的一壁,以及围绕真栅极tg的氮化间隔层2206的一壁所围绕。任何能形成所述金属氧化物半导体场效应晶体管的源极2402和漏极2404的现有技术都可用水平硅表面hss来实现源极2402和漏极2404的平坦面。

189.如图24(a)所示,因为化学气相沉积

‑

浅沟槽隔离

‑

第三氧化层2304的两壁,在浅沟槽隔离

‑

第二氧化层2102上的氮化间隔层2206,以及围绕真栅极tg的氮化间隔层2206像是四个侧壁一样都高于水平硅表面hss,所以另一种设计良好的四个氧化间隔层2406(称为用于接触孔的氧化间隔层(oxide spacer for contact hole,oxide

‑

sch)))可被新创造出来以覆盖所述四个侧壁。因此,所述接触孔开口是以自对准的方式自然的形成,而不需要利用任何用来制造所述接触孔开口的蚀刻技术,并且通过用于所述接触孔的氧化间隔层(oxide

‑

sch)的合适设计(具有厚度tosch),所述接触孔开口的长度尺寸可以分别小于距离gebesi和距离gebedi的长度。本发明创新的部分是所述接触孔开口的位置分别是在所述源极和所述漏极的边界的中央,并且所述接触孔开口的长度可以被设计成小于λ(因为接触孔的长度=距离gebesi的长度

‑

2倍厚度tosch。因此例如,如果厚度tosch=0.2λ以及距离gebesi的长度=λ,则接触孔的长度=0.6λ)。根据本发明,所述自对准接触孔展示了最小的接触孔长度(其尺寸可小于λ),其比任何现有技术的设计和通过所述光刻光罩技术及复杂蚀刻工艺所制造出来的接触孔开口的长度都还要小。另外,本发明省略了大部分难以控制的因素以及大部分用来定义和制造所述第一金属层接触的的昂贵的光罩和后续钻挖所述接触孔开口的任务。另外,图24(b)是对应图24(a)的俯视图。

190.图25是说明在沉积一第一金属层2502以填满所述接触孔开口后,利用所述光刻光罩技术定义第一金属层2502的示意图。如图25所示,第一金属层2502必须具有精确控制尺寸的宽度,其中第一金属层2502的宽度必须能完全覆盖所述接触孔开口,并且要预留给任何无法避免的光刻错位公差。也就是说对应所述源极的第一金属层2502的宽度等于所述接触孔开口(在所述源极上)的长度c

‑

s(l)加上2δλ,以及对应所述漏极的第一金属层2502的

宽度等于所述接触孔开口(在所述漏极上)的长度c

‑

d(l)加上2δλ。如果所述接触孔开口的长度可以控制在0.6λ(其可被控制,因为由前述说明的计算可得知所述接触孔内的氧化间隔层2406的尺寸可被良好控制),则第一金属层2502的宽度可以小至所述接触孔开口的长度和2δλ的总和(如果在本发明一实施例中,δλ=0.5λ,所述接触孔开口的长度=0.6λ,则为了在无法避免的光刻错位公差下还能完全覆盖所述接触孔开口,第一金属层2502的宽度可以窄至1.6λ。根据本发明,窄至1.6λ的第一金属层2502的宽度可以是所述第一金属层互连的最小宽度之一。另外,在两个最靠近的第一金属层互连之间的一最小空间2504不能小于λ。另外,本发明重要的优点是几乎每个关键的尺寸,例如距离gebesi和距离gebedi的长度、接触孔开口的长度、和所述第一金属层互连的宽度都可以被精确的控制,而不受不确定的光刻错位公差所影响,如此,基于关键尺寸的一致性,可以确保每个关键的尺寸的重现性、质量和可靠性。

191.综上所述,本发明的实施例所公开的金属氧化物半导体场效应晶体管结构可通过避免光刻错位公差,尤其是关于栅极和源极、栅极和漏极、第一金属层和源极/漏极之间的接触孔开口等之间的几何关系、以及第一金属层互连的宽度与其填满接触孔的自对准方法等的设计与工艺的改善,对未来集成电路的设计带来几项主要的进步:

192.(1)通过排除光刻错位公差所造成的不确定因素以精确的定义分别从所述栅极的两边缘的长度s(l)和长度d(l)。

193.(2)长度s(l)和长度d(l)都可被设计成光刻光罩和工艺分辨率所能允许的最小特征长度λ,从而显着地缩小所述源极和所述漏极的尺寸。如此,可减少所述金属氧化物半导体场效应晶体管的面积和可减少待机与操作电流和功耗,而可据此增进金属氧化物半导体场效应晶体管的操作速度。

194.(3)因为长度s(l)和长度d(l)都可被精确控制,所以通过围绕所述源极和漏极的四个侧壁所创造的间隔层,本发明的自对准技术能精确的制造可控制形状和尺寸并且分别接近所述源极和所述漏极中央的自对准接触孔(self

‑

alignment contact holes,sach)。

195.(4)自对准接触孔的长度可被设计成小于最小特征尺寸λ,例如小至0.6λ或甚至更窄。

196.(5)所述自对准接触孔的其他宽度尺寸可以通过自对准间隔层和良好定义的主动区宽度而被良好的设计;因为所述自对准接触孔的形成是通过间隔层技术,而不是通过具有难以控制的错位公差和接触孔形状的光刻光罩技术来定义接触孔的现有技术来形成,其中所述间隔层技术是取决于运用具有可控厚度的化学薄膜沉积和利用所述异向性蚀刻技术的已发展成熟的技术。本发明的接触孔开口可以被良好的设计和定义(虽然接触孔可能不具有一致的方形接触形状,但接触孔具有良好定义的长方形形状且填充结果实际上取决于所述接触孔较窄的长度尺寸)。

197.(6)排除最具艰难和最昂贵的接触步骤及光罩。

198.(7)从多个接触孔之间完全分离一个方形孔或多个方形孔变成长方形的单一接触孔或单一接触沟槽以改变接触孔的设计;因此所述源极(或所述漏极)的宽度(或长度)可以刚好和所述栅极的宽度(或长度)一样而不会受限于利用狗骨头形状布局(dog

‑

bone layout)以调整所述栅极的宽度和可能具有多个方形接触孔的所述源极(或所述漏极)的宽度之间的尺寸差异。

199.(8)因为具有良好设计的厚度的第一金属层互连的填满成功与否是取决于接触孔的最小尺寸(通常是所述自对准接触(sach)孔的长度),所以所述第一金属层互连可确实填满所有存在的接触孔,从而使现有技术中用于形成接触柱的两个步骤(例如填充钨加上平坦化工艺,也就是现有技术所公开的钨柱工艺和第一金属层嵌入工艺)可以被简化成一个第一金属层沉积工艺。

200.(9)通过上述整合的所述自对准接触孔和所述第一金属层形成工艺以及所述栅极被覆盖在所述氮化帽层之下且被所述间隔层保护(其中所述氮化帽层和所述间隔层都可在所述自对准接触孔外的区域上创造一平坦的平面),所述第一金属层互连可被设计成具有多种布局方式以创建最佳分布的第一金属层互连网。

201.(10)综合上述优点,本发明所公开的金属氧化物半导体场效应晶体管结构可被制造成具有非常小的尺寸,其中所述金属氧化物半导体场效应晶体管结构具有4λ的最小长度尺寸(也就是说包含等于λ的长度s(l),等于λ的长度d(l),等于λ的栅极长度,1/2λ用于左边的隔离,以及1/2λ用于右边的隔离)以及具有2λ的最小宽度尺寸,也就是说可在面积8λ2内实现了一种具有接触孔和分别连接到所述源极和所述漏极的第一金属层互连的世界上最小的单一晶体管。

202.当然,根据设计需求,长度g(l)、长度s(l)或长度d(l)可以大于最小特征长度λ。

203.因为本发明排除了光刻错位公差的不确定性并且采用新的自对准设计和工艺技术,所以本发明的所有优点不仅不受限于应用在单一金属氧化物半导体场效应晶体管,也可应用在互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)电路,例如在面积方面进行了许多优化的功能单元(例如静态随机存取存储器(static random access memory,sram),与非门(nand gate),或非门(nor gate),以及任何逻辑门)都可以通过本发明的设计和制造原则来缩小芯片面积、电流、功耗以及速度,并且具有准确性、可重复性、一致性以及更佳的裕度(margin)。

204.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1