接合用晶片结构及其制造方法与流程

1.本发明涉及一种半导体接合技术,尤其涉及一种接合用晶片结构及其制造方法。

背景技术:

2.外延(epitaxy)是指在晶片上长出新结晶,以形成半导体层的技术。由于以外延工艺所形成的膜层具有纯度高、厚度控制性佳等优点,因此已经广泛应用于射频器件或功率器件的制造中。

3.然而,一般外延成长的晶片或晶锭,因为邻近晶种的外延结构缺陷多、应力大,所以通常舍弃不用,只保留品质较佳的外延结构,导致废弃成本增加。

技术实现要素:

4.本发明是针对一种接合用晶片结构,能降低成本并将品质差的碳化硅晶片转用至接合用基板。

5.本发明另针对一种接合用晶片结构的制造方法,可制作出应用于射频器件或功率器件的外延工艺的接合用晶片结构。

6.根据本发明的实施例,一种接合用晶片结构包括支撑基板、接合层以及碳化硅层。接合层形成在支撑基板的表面,碳化硅层接合在所述接合层上,其中碳化硅层的碳面与接合层直接接触。所述碳化硅层的基面线性差排缺陷(bpd)在1000ea/cm2~20000ea/cm2之间,所述碳化硅层的总厚度变异量(ttv)大于支撑基板的总厚度变异量,所述碳化硅层的直径等于或小于支撑基板的直径。所述接合用晶片结构的ttv小于10μm、弯曲度(bow)小于30μm以及翘曲度(warp)小于60μm。

7.在根据本发明的实施例的接合用晶片结构中,上述接合层的软化点(softening point)在50℃~200℃之间、厚度小于100μm以及均匀度(uniformity)小于10%。

8.在根据本发明的实施例的接合用晶片结构中,上述支撑基板的总厚度变异量小于3μm、弯曲度小于20μm、翘曲度小于40μm以及杨氏模数大于160gpa。

9.在根据本发明的实施例的接合用晶片结构中,上述支撑基板包括单层或多层结构,且上述接合层包括单层或多层结构。

10.在根据本发明的实施例的接合用晶片结构中,上述碳化硅层与上述支撑基板的同圆心率小于1mm。

11.在根据本发明的实施例的接合用晶片结构中,上述接合用晶片结构还可包括外延用碳化硅基板,接合在上述碳化硅层的硅面,其中外延用碳化硅基板的基面线性差排缺陷小于碳化硅层的基面线性差排缺陷,且外延用碳化硅基板的应力小于碳化硅层的应力。

12.在根据本发明的实施例的接合用晶片结构中,上述接合用晶片结构还可包括离子注入区,形成在所述外延用碳化硅基板内,其中离子注入区距离外延用碳化硅基板与碳化硅层的接合面约在1μm以内。

13.在根据本发明的实施例的接合用晶片结构中,上述碳化硅层的厚度小于500μm,且

上述接合用晶片结构的厚度小于2000μm。

14.根据本发明的另一实施例,一种接合用晶片结构的制造方法,包括在一支撑基板的一表面涂布形成一接合层,在所述接合层上接合一碳化硅层的碳面,其中所述碳化硅层的总厚度变异量(ttv)大于支撑基板的总厚度变异量,所述碳化硅层的直径等于或小于支撑基板的直径,所述碳化硅层的基面线性差排缺陷(basal plane dislocation,bpd)在1000ea/cm2~20000ea/cm2之间,所述碳化硅层接合前的弯曲度(bow)大于75μm且翘曲度(warp)大于150μm。然后,磨削上述碳化硅层的硅面,以减少碳化硅层的厚度。对磨削后的碳化硅层的硅面进行抛光,以得到一接合用晶片结构,且所述接合用晶片结构的总厚度变异量小于10μm、弯曲度小于30μm以及翘曲度小于60μm。

15.在根据本发明的另一实施例的制造方法中,在上述接合层上接合碳化硅层的碳面的方法包括:对准支撑基板的平边与碳化硅层的平边。

16.在根据本发明的另一实施例的制造方法中,在上述接合层上接合碳化硅层的碳面的负载为8kgf~10kgf。

17.在根据本发明的另一实施例的制造方法中,在上述接合层上接合碳化硅层的碳面之后,还可包括去除残留的接合层材料以及清洁支撑基板。

18.在根据本发明的另一实施例的制造方法中,上述磨削去除的碳化硅层的厚度在5μm~12μm之间。

19.在根据本发明的另一实施例的制造方法中,接合前的碳化硅层与抛光之后的接合用晶片结构在弯曲度的变化(δbow)大于80μm,且接合前的碳化硅层与抛光之后的接合用晶片结构在翘曲度的变化(δwarp)大于160μm。

20.在根据本发明的另一实施例的制造方法中,涂布形成上述接合层的方式包括:在110℃~130℃的温度旋涂蜡到支撑基板的上述表面。

21.在根据本发明的另一实施例的制造方法中,在磨削碳化硅层的硅面之前,还可包括先测量接合在一起的支撑基板、接合层与碳化硅层的总厚度变异量,若是此总厚度变异量小于10μm则进行后续步骤;反之,若是在10μm以上则包括:移除所述接合层与所述碳化硅层,然后重新进行在所述支撑基板的所述表面涂布形成一接合层的所述步骤。

22.在根据本发明的另一实施例的制造方法中,上述抛光包括粗抛光与细抛光。

23.基于上述,本发明的接合用晶片结构基本上由三层结构构成,其中包含一层低品质(高应力)的碳化硅层,取代一部分原有的支撑基板,这层碳化硅层是外延成长后剔除的废品,将其转用至接合用结构不但能降低支撑基板的材料成品与废弃成本,还能与外延用碳化硅基板直接接合(direct bonding),改善晶片接合的产率(yield)。本发明的接合用晶片结构适合应用于功率(power)器件或射频(rf)器件的工艺。

附图说明

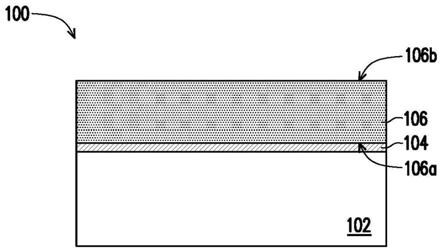

24.图1是依照本发明的第一实施例的一种接合用晶片结构的剖面示意图;

25.图2是依照本发明的第一实施例的另一种接合用晶片结构的剖面示意图;

26.图3是依照本发明的第二实施例的一种接合用晶片结构的制造流程步骤图;

27.图4是第二实施例的步骤s302的立体示意图。

28.附图标记说明

29.100、200:接合用晶片结构

30.102:支撑基板

31.104:接合层

32.106:碳化硅层

33.106a:碳面

34.106b:硅面

35.106c、102a:平边

36.202:外延用碳化硅基板

37.204:离子注入区

38.206:接合面

39.s:距离

40.s300、s302、s304、s306、s308、s310、s312、s314:步骤

具体实施方式

41.以下将参考附图来全面地描述本发明的例示性实施例,但本发明仍可按照多种不同形式来实施,且不应解释为限于本文所述的实施例。为了清楚起见,各区域、部位及层的大小与厚度可不按实际比例绘制。为了方便理解,下述说明中相同的构件将以相同的附图标记来说明。

42.图1是依照本发明的第一实施例的一种接合用晶片结构的剖面示意图。

43.请参照图1,第一实施例的接合用晶片结构100基本上包括一支撑基板102、一接合层104以及一碳化硅层106。支撑基板102是一种刚性高而在加工时不易变形/翘曲/破损的坚固材料构成的基板,例如杨氏模数大于160gpa的材料,较佳是杨氏模数大于180gpa的材料。在一实施例中,支撑基板102的总厚度变异量(ttv)例如小于3μm,较佳是小于1μm;支撑基板102的弯曲度(bow)例如小于20μm,较佳是小于15μm;支撑基板102的翘曲度(warp)例如小于40μm,较佳是小于30μm。举例来说,支撑基板102例如硅基板、蓝宝石基板、陶瓷基板或其组合。换句话说,支撑基板102可为单层或多层结构。接合层104则形成在支撑基板102的表面,其中接合层104的软化点(softening point)例如在50℃~200℃之间,较佳是在80℃~150℃之间;若是接合层104的软化点设定在上述范围,将有利于后续要分离支撑基板102与碳化硅层106时,使用高温即可分离两者。接合层104的厚度例如小于100μm,较佳是在10μm~20μm之间;接合层104的均匀度(uniformity)例如小于10%,较佳是小于5%。举例来说,接合层104的材料可为蜡或固定胶。若是考量到支撑基板102和碳化硅层106在接合期间需调整对位,较佳是使用流动性较大的蜡作为接合层104的材料。然而,本发明并不限此;若是在支撑基板102和碳化硅层106对准精确的情况下,也可使用如uv胶之类的固定胶作为接合层104的材料。而且,接合层104也可为单层或多层结构。

44.请继续参照图1,碳化硅层106接合在接合层104上,亦即碳化硅层106通过接合层104固定在支撑基板102上。碳化硅层106的碳面106a与接合层104直接接触,碳化硅层106的硅面106b则暴露出来,可用于后续与其他外延用基板(未示出)结合。所述碳化硅层106的基面线性差排缺陷(bpd)在1000ea/cm2~20000ea/cm2之间,例如在4000ea/cm2~10000ea/cm2之间,所述碳化硅层106的总厚度变异量(ttv)大于支撑基板102的总厚度变异量,所述碳化

硅层106的直径等于或小于支撑基板102的直径。举例来说,未接合之前的碳化硅层106的ttv例如小于10μm,较佳是小于5μm;但是bow例如大于75μm或者大于100μm,且warp例如大于150μm或者大于200μm。这是因为未接合之前的碳化硅层106是采用邻接晶种的高应力碳化硅晶片,所以bow与warp都比较大。然而,在接合之后的接合用晶片结构100的ttv小于10μm、bow小于30μm以及warp小于60μm,因此可应用于功率(power)器件或射频(rf)器件的外延工艺。在一实施例中,接合用晶片结构100的ttv可小于3μm、bow可小于20μm以及warp可小于40μm。在本实施例中,碳化硅层106的厚度例如小于500μm,较佳是小于400μm;接合用晶片结构100的厚度例如小于2000μm,较佳是小于1000μm。另外,碳化硅层106与支撑基板102的同圆心率例如小于1mm,较佳是小于0.5mm。

45.图2是依照本发明的第一实施例的另一种接合用晶片结构的剖面示意图,其中使用与图1相同的器件符号来表示相同或近似的构件,且相同或近似的构件也可参照图1的相关说明,不再赘述。

46.在图2中,接合用晶片结构200可包括一外延用碳化硅基板202,接合在碳化硅层106的硅面106b,其中外延用碳化硅基板202的基面线性差排缺陷(bpd)小于碳化硅层106的基面线性差排缺陷,且外延用碳化硅基板202的应力小于碳化硅层106的应力。此外,在外延用碳化硅基板202内可形成一离子注入区204(即虚线标示的区域),其中所述离子注入区204是接近于外延用碳化硅基板202与碳化硅层106的接合面206;在一实施例中,离子注入区204与接合面206之间的距离s例如在1μm以内,由于离子注入区204会在外延用碳化硅基板202内产生较脆弱的结构,所以后续能轻易地从离子注入区204分离外延用碳化硅基板202与碳化硅层106。

47.图3是依照本发明的第二实施例的一种接合用晶片结构的制造流程步骤图。

48.请参照图3,先进行步骤s300,在支撑基板的表面涂布形成一接合层,其中接合层的软化点例如在50℃~200℃之间,较佳是在80℃~150℃之间。若是以蜡作为接合层的材料,可在110℃~130℃的温度旋涂液体蜡到支撑基板的表面。支撑基板的杨氏模数例如大于160gpa,较佳是大于180gpa;ttv例如小于3μm,较佳是小于1μm;bow例如小于20μm,较佳是小于15μm;warp例如小于40μm,较佳是小于30μm。支撑基板例如硅基板、蓝宝石基板、陶瓷基板或其组合,且支撑基板可为单层或多层结构。至于接合层的厚度例如小于100μm,较佳是在10μm~20μm之间;均匀度例如小于10%,较佳是小于5%。

49.接着进行步骤s302,在接合层上接合碳化硅层的碳面,其中碳化硅层的ttv大于支撑基板的ttv,碳化硅层的直径等于或小于支撑基板的直径,且碳化硅层的bpd在1000ea/cm2~20000ea/cm2之间,例如在4000ea/cm2~10000ea/cm2之间。碳化硅层的厚度例如小于500μm,较佳是小于400μm。碳化硅层接合前的ttv例如小于10μm,较佳是小于5μm;但是bow大于75μm例如大于100μm,且warp大于150μm例如大于200μm。在本实施例中,接合碳化硅层的方法例如图4所示,对准支撑基板102的平边102a与碳化硅层106的平边106c,降低平边处在后工艺加工时产生碎边或崩边。为了清楚起见,图4中省略示出接合层。而上述接合的负载例如》8kgf,较佳是8kgf~10kgf。步骤s302之后的碳化硅层与支撑基板的同圆心率例如小于1mm,较佳是小于0.5mm。

50.然后进行步骤s304,磨削(grinding)碳化硅层的硅面,以减少碳化硅层的厚度,其中磨削去除的碳化硅层的厚度例如在5μm~12μm之间,较佳8μm~12μm,使硅面的ttv小于5μ

m,较佳小于1μm,磨削后的整体晶片较平坦几何较佳。

51.之后进行步骤s306,对磨削后的碳化硅层的硅面进行抛光,以得到一接合用晶片结构,其中抛光包括粗抛光与细抛光,使硅面的几何ttv小于2μm,较佳小于1μm。在一实施例中,施行粗抛光后与施行细抛光后的粗糙度ra如下所示:

52.1.粗抛光haze=4.67,ra约0.1nm~0.19nm。

53.2.细抛光haze=4.16~4.19,ra平均约0.13nm~0.062nm。

54.步骤s306之后的接合用晶片结构的ttv小于10μm(例如小于3μm)、bow小于30μm(例如小于20μm)以及warp小于60μm(例如小于40μm)。换句话说,接合前的碳化硅层与抛光之后的接合用晶片结构在弯曲度的变化(δbow)大于45μm,较佳是大于80μm,且接合前的碳化硅层与抛光之后的接合用晶片结构在翘曲度的变化(δwarp)大于90μm,较佳是大于160μm。而接合用晶片结构的厚度例如小于2000μm,较佳是小于1000μm。

55.此外,在步骤s302之后,还可先进行步骤s308,去除残留的接合层材料以及清洁支撑基板。

56.若是考量后续外延工艺的产率,可在步骤s304之前先进行步骤s310,测量接合在一起的支撑基板、接合层与碳化硅层的ttv,然后在步骤s312中,若是ttv《10μm则进行后续步骤s304;反之,若是ttv在10μm以上,则先进行步骤s314,去除接合层以及碳化硅层,然后回到步骤s300,在原本的支撑基板的表面另涂布形成一接合层。步骤s310可在步骤s302或步骤s308之后进行。

57.以下列举几个实验来验证本发明的效果,但本发明并不局限于以下的内容。

58.分析方式

59.1.厚度:使用非接触式仪器测量晶片厚度(mx-203/frt/ade7000)。

60.2.ttv、warp、bow:使用非接触式仪器测量。

61.3.bpd:利用自动光学检测(aoi)并计算其密度。

62.〈实验例1〉

63.步骤1)在室温下旋涂蜡到碳化硅与硅基板表面(厚度无限制与当下工艺治具配合选用),放置到120℃加热盘上,加热60秒。

64.步骤2)接合碳化硅层与硅基板,使硅基板的平边与碳化硅层的平边对齐,并在其上予以》8kgf负载静置60秒。碳化硅层的基面线性差排缺陷(bpd)约为4048ea/cm2。

65.步骤3),磨削碳化硅层的硅面约5μm。

66.步骤4),对磨削后的碳化硅层的硅面进行抛光,温度35℃~60℃,温度在此范围可避免晶片边缘剥离还能确保移除量足够,抛光移除量约1μm,以得到一接合用晶片结构。

67.对硅基板以及单独(接合前)的碳化硅层进行平坦特性的测量,并记载于下表1。然后,在步骤2)、3)、4)后均对整体结构进行平坦特性的测量,并记载于下表1。

68.〈实验例2〉

69.与实验例1一样的方式制备接合用晶片结构,其中不同处在于碳化硅层的bpd约4002ea/cm2。然后针对各阶段的结构进行平坦特性的测量,并记载于下表1。

70.〈实验例3〉

71.与实验例1一样的方式制备接合用晶片结构,其中不同处在于碳化硅层的bpd约3957ea/cm2。然后针对各阶段的结构进行平坦特性的测量,并记载于下表1。

72.表1

[0073][0074]

从上表可得到,进接合前的单独的碳化硅层无论是bow或是warp都偏高(分别大于100/大于200),而在实验例1~3经步骤2)接合后的bow和warp已大幅降低(分别约小于20/40),所以能应用在如功率(power)器件或射频(rf)器件的外延工艺。

[0075]

综上所述,本发明接合用晶片结构是利用一层低品质(高应力)的碳化硅层取代一部分原有的支撑基板,与外延用碳化硅基板直接接合,而且完成前述接合工艺后的接合用晶片结构,可通过高温就分离支撑基板与上述低品质的碳化硅层,使支撑基板能被重复利用,所以不但能降低支撑基板的材料成品也可降低废弃低品质sic外延晶片的成本。而且,本发明具有高平坦度的接合用晶片结构有利于客户进行接合工艺,改善晶片接合的产率并适于应用在功率/射频器件的外延工艺。

[0076]

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依

然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1