半导结构及半导体结构的制备方法与流程

1.本公开涉及半导体领域,尤其涉及一种半导结构及半导体结构的制备方法。

背景技术:

2.随着半导体技术的发展,半导体器件的尺寸逐渐缩小,降低厚度已经成为未来半导体器件的主要研发方向。

3.为了在半导体器件中存储电荷,需要维持足够高的电容值。为了提高或保持电容器的容量,通常增加下电极的高度或者减小下电极的厚度,以扩大下电极与电容介质层之间的接触面积。减小下电极的厚度容易引起下电极坍塌,增加下电极的高度会导致半导体器件的厚度增加。

技术实现要素:

4.本公开实施例提供了一种半导结构及半导体结构的制备方法,以解决现有的电容器容量不足的问题。

5.为此,本公开实施例提供了如下技术方案:

6.第一方面,本公开实施例提供了一种半导体结构包括:

7.多个位线堆叠结构,所述位线堆叠结构布置在衬底上;

8.存储接触结构,所述存储接触结构设置在一对所述位线堆叠结构之间,所述存储接触结构的顶面低于所述位线堆叠结构的顶面;

9.电容结构,所述电容结构的下电极的底面的一部分支撑在所述存储接触结构的顶面,所述下电极的底面的另一部分支撑在对应的所述位线堆叠结构的顶面。

10.本公开实施例提供的半导体结构包括顶面具有高度差的存储接触结构和位线堆叠结构,下电极的底面的一部分与存储接触结构的顶面接触,下电极的底面的另一部分与位线堆叠结构的顶面接触,使得下电极向下延伸,提高了下电极的高度,进而提高了电容器的容量。

11.可选地,所述存储接触结构包括存储节点插塞和设置在所述存储节点插塞上方的接触焊盘;

12.所述位线堆叠结构包括从上到下依次堆叠的位线绝缘层、位线和位线接触插塞。

13.可选地,所述接触焊盘和所述存储节点插塞通过焊盘黏附层连接。

14.可选地,所述位线和所述位线接触插塞通过位线黏附层连接。

15.可选地,所述存储节点插塞的顶面高于所述位线绝缘层的底面;

16.所述存储节点插塞的底面高于所述位线接触插塞的底面。

17.可选地,所述下电极的顶面的面积小于所述下电极的底面的面积。

18.可选地,所述下电极下部的截面从上到下逐渐增大。

19.可选地,所述存储接触结构的纵向截面为t形。

20.可选地,所述电容结构为柱状电容或杯状电容。

21.可选地,所述下电极与所述存储接触结构的顶面的接触面积大于所述下电极与所述位线堆叠结构的顶面的接触面积。

22.第二方面,本公开实施例提供了一种半导体结构的制备方法,包括:

23.在衬底上形成多个位线堆叠结构;

24.在一对所述位线堆叠结构之间形成存储接触结构,所述存储接触结构的顶面低于所述位线堆叠结构的顶面;

25.形成下电极,所述下电极的底面的一部分支撑在所述存储接触结构的顶面,所述下电极的底面的另一部分支撑在对应的所述位线堆叠结构的顶面。

26.本公开实施例提供的半导体结构通过设置顶面具有高度差的存储接触结构和位线堆叠结构,并使得下电极的底面的一部分与存储接触结构的顶面接触,下电极的底面的另一部分与位线堆叠结构的顶面接触,使得下电极向下延伸,提高了下电极的高度,进而提高了电容器的容量。

27.可选地,在衬底上形成多个位线堆叠结构包括:

28.在所述衬底的上方形成位线接触插塞;

29.在所述位线接触插塞的上方形成位线;

30.在所述位线上方形成位线绝缘层,

31.在一对所述位线堆叠结构之间形成存储接触结构包括:

32.在所述衬底的上方形成存储节点插塞;

33.在所述存储节点插塞的上方形成接触焊盘。

34.可选地,在所述存储节点插塞的上方形成接触焊盘包括:

35.形成焊盘氧化层,所述焊盘氧化层覆盖所述存储节点插塞以及所述位线绝缘层;

36.对所述焊盘氧化层进行图形化暴露出所述位线绝缘层的顶端,保留位于所述存储节点插塞顶面的所述焊盘氧化层,被保留下来的所述焊盘氧化层构成所述接触焊盘。

37.可选地,在所述支撑结构的顶面形成下电极包括:

38.形成牺牲层,所述牺牲层覆盖所述接触焊盘以及所述位线绝缘层;

39.对所述牺牲层进行刻蚀形成电容孔,所述电容孔暴露出所述位线绝缘层;

40.对所述牺牲层进行刻蚀,所述电容孔暴露出所述接触焊盘;

41.在所述电容孔内形成所述下电极,所述下电极覆盖所述电容孔的侧壁和底部。

42.可选地,所述电容孔的形状为l形。

43.可选地,所述位线包括如下一种或几种材料:钨、铝、铜、镍和钴。

44.本公开实施例中提供的一个或多个技术方案,具有如下优点:

45.本公开实施例提供的半导体结构包括顶面具有高度差的存储接触结构和位线堆叠结构,下电极的底面的一部分与存储接触结构的顶面接触,下电极的底面的另一部分与位线堆叠结构的顶面接触,使得下电极向下延伸,提高了下电极的高度,进而提高了电容器的容量。

附图说明

46.在下面结合附图对于示例性实施例的描述中,本公开的更多细节、特征和优点被公开,在附图中:

47.图1为相关技术中的一种半导体结构的剖面示意图。

48.图2为图1所示的一种半导体结构的俯视图。

49.图3示出了根据本公开示例性实施例的半导体结构的剖面示意图。

50.图4示出了图2所示的半导体结构的俯视图。

51.图5示出了根据本公开一实施例的半导体结构的制备方法的流程图;

52.图6示出了根据本公开实施例的接触焊盘的制备方法的流程图;

53.图7示出了根据本公开实施例的下电极的制备方法的流程图;

54.图8示出了根据图6所示的接触焊盘的制备方法在执行步骤s201时的示意图。

55.图9示出了根据图6所示的接触焊盘的制备方法在执行步骤s202时的示意图。

56.图10示出了根据图7所示的下电极的制备方法在执行步骤s301时的示意图。

57.图11示出了根据图7所示的下电极的制备方法在执行步骤s302时的示意图。

58.图12示出了根据图7所示的下电极的制备方法在执行步骤s303时的示意图。

59.图13示出了根据图7所示的下电极的制备方法在执行步骤s304时的示意图。

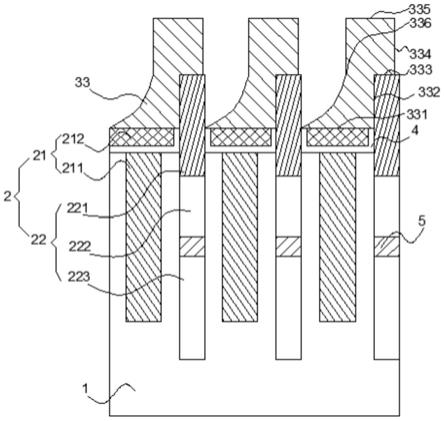

60.其中,附图标记如下:

61.衬底,1;字线,11;

62.支撑结构,2;存储接触结构,21;存储节点插塞,211;接触焊盘,212;位线堆叠结构,22;位线绝缘层,221;位线,222;位线接触插塞,223;

63.下电极,33;第一边,331;第二边,332;第三边,333;第四边,334;第五边,335;第六边,336;

64.焊盘黏附层,4;

65.位线黏附层,5;

66.焊盘氧化层,6;

67.牺牲层,7;

68.电容孔,8;

69.第一存储接触结构,91;第一位线堆叠结构,92;第一接触焊盘,93;第一下电极,94;第一电容介质层,95;第一上电极,96;第一衬底,97。

具体实施方式

70.下面将参照附图更详细地描述本公开的实施例。虽然附图中显示了本公开的某些实施例,然而应当理解的是,本公开可以通过各种形式来实现,而且不应该被解释为限于这里阐述的实施例,相反提供这些实施例是为了更加透彻和完整地理解本公开。应当理解的是,本公开的附图及实施例仅用于示例性作用,并非用于限制本公开的保护范围。

71.应当理解,本公开的方法实施方式中记载的各个步骤可以按照不同的顺序执行,和/或并行执行。此外,方法实施方式可以包括附加的步骤和/或省略执行示出的步骤。本公开的范围在此方面不受限制。

72.本文使用的术语“包括”及其变形是开放性包括,即“包括但不限于”。术语“基于”是“至少部分地基于”。术语“一个实施例”表示“至少一个实施例”;术语“另一实施例”表示“至少一个另外的实施例”;术语“一些实施例”表示“至少一些实施例”。其他术语的相关定义将在下文描述中给出。需要注意,本公开中提及的“第一”、“第二”等概念仅用于对不同的

元件进行区分,并非用于限定这些元件的功能或者相互依存关系。

73.需要注意,本公开中提及的“一个”、“多个”的修饰是示意性而非限制性的,本领域技术人员应当理解,除非在上下文另有明确指出,否则应该理解为“一个或多个”。

74.图1为相关技术中的一种半导体结构的剖面示意图。如图1所示,该半导体结构包括第一衬底97、第一存储接触结构91、第一位线堆叠结构92、第一接触焊盘93、第一下电极94、第一电容介质层95和第一上电极96。第一接触焊盘为阶梯状结构,第一接触焊盘93覆盖第一位线堆叠结构92的顶面并向下延伸覆盖第一存储接触结构91的顶面。第一下电极94设置在第一接触焊盘93的顶面,第一下电极94的底面为平面。如图2所示,第一下电极94为圆柱形。相关技术中,为了提高电容器的容量,通常将第一下电极94向上延伸来增加第一下电极94的高度,但第一下电极94向上延伸的高度受到半导体器件厚度的限制。由背景技术可知,半导体器件的主要研发方向是降低厚度,随着半导体器件厚度的降低,电容器难以维持足够的容量。

75.图3示出了根据本公开示例性实施例的半导体结构的剖面示意图。图4示出了根据本公开示例性实施例的半导体结构的俯视图。如图3和图4所示,本公开示例性实施例提供了一种半导体结构,包括堆叠设置的衬底1、支撑结构2和电容结构。支撑结构2包括位线堆叠结构22和存储接触结构21。位线堆叠结构22和存储接触结构21设置在衬底1的上方,电容结构覆盖位线堆叠结构22和存储接触结构21。

76.衬底1可选包括如下一种或几种半导体材料:硅(si)、锗(ge)、硅锗(sige)和绝缘体上硅(soi)。衬底1可选包括在第一方向上延伸的字线11,字线11可选埋入衬底1内。字线11可选为多个,多个字线11彼此间隔设置。字线11可选包括如下一种或几种导电材料:多晶硅、钨和金属硅化物。

77.位线堆叠结构22的数量为多个,多个位线堆叠结构22间隔设置在衬底1顶面。位线堆叠结构22沿第二方向延伸,第二方向与第一方向相交。第二方向可选与第一方向垂直。位线堆叠结构22的纵向截面为矩形。位线堆叠结构22包括从上到下依次堆叠的位线绝缘层221、位线222和位线接触插塞223。位线222可选包括如下一种或几种导电材料:钨、铝、铜、镍和钴。位线222和位线接触插塞223通过位线黏附层5连接。位线222直接与位线接触插塞223接触时附着性较差,影响位线222的电性能。通过位线黏附层5连接位线222和位线接触插塞223能够提高整体结构的稳定性。位线黏附层5可选包括氮化硅或氮氧化硅。

78.存储接触结构21设置在衬底1上,存储接触结构21可选设置两个位线堆叠结构22之间。存储接触结构21可选设置在位线堆叠结构22和字线11的交叉间隙中。存储接触结构21的数量可选为多个。存储接触结构21的顶面低于位线堆叠结构22的顶面。存储接触结构21可选包括存储节点插塞211和设置在存储节点插塞211上方的接触焊盘212。存储节点插塞211可选包括多晶硅。接触焊盘212可选包括氧化钨。存储接触结构21的纵向截面可选为t形。接触焊盘212可选通过焊盘黏附层4与存储节点插塞211连接。接触焊盘212直接与存储节点插塞211接触时附着性较差。通过焊盘黏附层4连接焊盘和存储节点插塞211能够提高整体结构的稳定性。存储节点插塞211的顶面可选高于位线绝缘层221的底面。存储节点插塞211的底面高于位线接触插塞223的底面。

79.电容结构设置在支撑结构2的顶面,电容结构为柱状电容或杯状电容。杯状电容的制备方法包括:先在电容孔的侧壁形成下电极33,之后在下电极33的外侧依次沉积电解质

和上电极。柱状电容的制备方法包括:先形成填充整个电容孔的下电极33,之后在下电极33的外侧依次沉积介电层和上电极。

80.下电极33的底面的一部分与存储接触结构21的顶面接触,下电极33的底面的另一部分与对应的位线堆叠结构22的顶面接触,如图3所示,与下电极33对应的位线堆叠结构22可选位于存储接触结构21的右侧。下电极33可选与位线堆叠结构22的侧面接触。下电极33与存储接触结构21的顶面的接触面积可选大于下电极33与位线堆叠结构22的顶面的接触面积。下电极33下部的截面面积从上到下逐渐增大,以使得下电极33的底面的一部分与存储接触结构21的顶面相匹配,进而增大了下电极22与存储接触结构21的接触面积。在一些具体的实施方式中,下电极33的底面为阶梯状,下电极33的顶面的面积小于下电极33的底面的面积。下电极33的纵向截面由依次连接的第一边331、第二边332、第三边333、第四边334、第五边335和第六边335围成。第一边331与存储接触结构21的顶面接触,第二边332与位线堆叠结构22的侧面接触,第三边333与位线堆叠结构22的顶面接触,第四边334沿竖直方向设置,第五边335沿水平方向设置。第六边335上部为沿竖直方向设置的直线,第六边335下部为弧线,弧形的侧面增大了下电极33与电容介质层32的接触面积。下电极33可选包括如下一种或几种材料:钛(ti)、钨(w)和氮化钨(wn)。与相关技术中的柱状下电极相比,本公开示例性实施例提供的下电极33具有阶梯状的底面,整体结构的稳定性更高,能够减少电容器坍塌的风险。

81.一些相关技术中,接触焊盘212的顶面通常高于位线绝缘层221的顶面,由于下电极33设置在接触焊盘212的顶面,在不改变半导体器件的前提下,接触焊盘212顶面的高度限制了下电极33的高度。本公开示例性实施例通过去除部分接触焊盘212,降低了接触焊盘212顶面的高度。再将下电极33向接触焊盘212的方向延伸,能够在不增加半导体器件厚度的前提下提高下电极33的高度,进而增加电容器的容量。

82.图5示出了根据本公开一实施例的半导体结构的制备方法的流程图。如图5所示,本公开示例性实施例提供了一种半导体结构的制备方法,包括如下步骤:

83.s101:在衬底1上形成多个位线堆叠结构22。在一些具体的实施方式中,在在衬底1上形成多个位线堆叠结构22包括:在衬底1的上方形成位线接触插塞223,在位线接触插塞223的上方形成位线222,在位线222上方形成位线绝缘层221。在一些具体的实施方式中,衬底1包括多个有源区,沿着有源区中心部分执行刻蚀处理形成第一沟槽,填充第一沟槽形成位线堆叠结构22。

84.s102:在一对位线堆叠结构22之间形成存储接触结构21,存储接触结构21的顶面低于位线堆叠结构22的顶面。在一些具体的实施方式中,通过刻蚀在一对位线堆叠结构22之间形成第二沟槽,填充第二沟槽形成存储接触结构21。在一些具体的实施方式中,在一对位线堆叠结构22之间形成存储接触结构21包括:在衬底1的上方形成存储节点插塞211,在存储节点插塞211的上方形成接触焊盘212。存储节点插塞211可选包括如下一种或几种材料:多晶硅、氮化钛、钛和金属氮化物。

85.s103:形成下电极33,下电极33的底面的一部分支撑在存储接触结构21的顶面,下电极33的底面的另一部分支撑在对应的位线堆叠结构22的顶面。

86.一些相关技术中,接触焊盘212的顶面通常高于位线绝缘层221的顶面,由于下电极33设置在接触焊盘212的顶面,在不改变半导体器件的前提下,接触焊盘212顶面的高度

限制了下电极33的高度。本公开示例性实施例通过去除部分接触焊盘212,降低了接触焊盘212顶面的高度。再将下电极33向接触焊盘212的方向延伸,能够在不增加半导体器件厚度的前提下提高下电极33的高度,进而增加电容器的容量。

87.图6示出了根据本公开示例性实施例的接触焊盘212的制备方法的流程图。如图6所示,接触焊盘212的制备方法包括如下步骤:

88.s201:形成焊盘氧化层6,焊盘氧化层6覆盖存储节点插塞211以及位线绝缘层221。图8示出了根据本公开图6所示的实施例所提供的接触焊盘212的制备方法在执行步骤s201时的示意图。如图8所示,在存储节点插塞211和位线绝缘层221的顶面以及位线绝缘层221暴露出的侧面形成焊盘氧化层6,焊盘氧化层6可选包括氧化钨。

89.s202:对焊盘氧化层6进行图形化暴露出位线绝缘层221的顶端,保留位于存储节点插塞211顶面的焊盘氧化层6,被保留下来的焊盘氧化层6构成接触焊盘212。图9示出了根据本公开图6所示的实施例所提供的接触焊盘212的制备方法在执行步骤s202时的示意图。如图9所示,通过刻蚀移除位于位线绝缘层221上方的焊盘氧化层6,并通过刻蚀移除部分位于存储节点插塞211上方的焊盘氧化层6。在一些具体的实施方式中,图形化包括光阻涂布、曝光、显影、刻蚀、剥膜。

90.图7示出了根据本公开示例性实施例的下电极33的制备方法的流程图。如图7所示,下电极33的制备方法包括如下步骤:

91.s301:形成牺牲层7,牺牲层7覆盖接触焊盘212以及位线绝缘层221。图10示出了根据本公开图7所示的实施例所提供的下电极33的制备方法在执行步骤s301时的示意图。如图10所示,形成覆盖接触焊盘212顶面、位线绝缘层221顶面和位线绝缘层221暴露出的侧面的牺牲层7。牺牲层7为绝缘材料。

92.s302:对牺牲层7进行刻蚀形成电容孔8,电容孔8暴露出位线绝缘层221。图11示出了根据本公开图7所示的实施例所提供的下电极33的制备方法在执行步骤s302时的示意图。电容孔8可选为圆柱形,电容孔8暴露出位线绝缘层221的顶面。

93.s303:对牺牲层7进行刻蚀,电容孔8暴露出接触焊盘212。图12示出了根据本公开图7所示的实施例所提供的下电极33的制备方法在执行步骤s303时的示意图。如图12所示,刻蚀位于电容孔8底面的牺牲层7,电容孔8底面向接触焊盘212的方向延伸直至暴露出接触焊盘212。

94.s304:在电容孔8内形成下电极33,下电极33覆盖电容孔8的侧壁和底部。电容孔8的形状为l形。图13示出了根据本公开图7所示的实施例所提供的下电极33的制备方法在执行步骤s304时的示意图。如图13所示,在电容孔8内沉积导电材料形成下电极33。下电极33可选包括如下一种或几种材料:钛(ti)、钨(w)、镍(ni)、钴(co)和金属氮化物。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1