动态锁存器、半导体芯片、算力板及计算设备的制作方法

本申请涉及集成电路,尤其涉及一种动态锁存器、半导体芯片、算力板及计算设备。

背景技术:

1、目前在集成电路技术领域中,半导体器件(例如半导体芯片)可以采用cnod(continuous oxide diffusion,连续氧化物扩散区)的实现方式,也即,半导体器件中各个功能单元的od(oxide diffusion,氧化物扩散区)是连续的。

2、动态锁存器可用做数字信号的寄存,因此可应用于半导体器件,例如应用于半导体芯片。但在前述cnod的实现方式下,动态锁存器会存在漏电问题,导致动态锁存器发生异常。

技术实现思路

1、基于此,本申请提供了一种动态锁存器、半导体芯片、算力板及计算设备,以解决动态锁存器存在的漏电问题。

2、第一方面,本申请提供了一种动态锁存器,动态锁存器包括:

3、衬底;

4、传输门,设于所述衬底的第一区域;

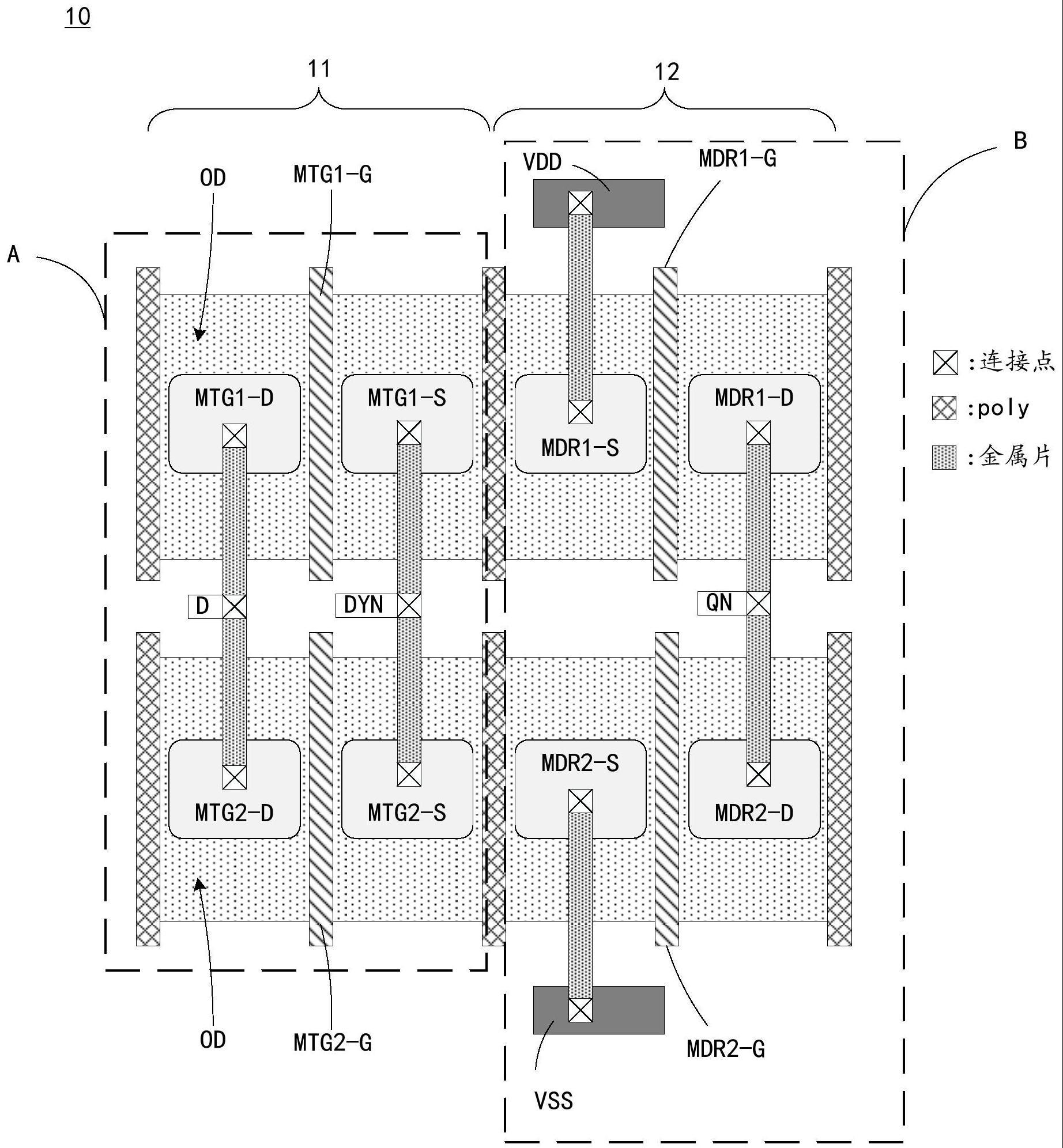

5、数据输出单元,设于所述衬底的第二区域,且包括第一反相器;所述第一反相器的输入端与所述传输门的输出端连接;其中,所述第一区域与所述第二区域邻接且两个区域内的氧化物扩散区是连续的;

6、其中,所述第一反相器的源极区在所述第二区域内位于靠近所述第一区域的一侧,所述第一反相器的漏极区在所述第二区域内位于远离所述第一区域的一侧。

7、第二方面,本申请提供了一种半导体芯片,所述半导体芯片包括一个或多个如上所述的动态锁存器。

8、第三方面,本申请还提供了一种算力板,所述算力板包括一个或多个如上所述的半导体芯片。

9、第四方面,本申请还提供了一种计算设备,计算设备包括电源板、控制板、连接板、散热器以及多个如上所述的算力板;所述电源板分别连接所述控制板、所述连接板、所述散热器以及各所述算力板;所述控制板通过所述连接板连接所述算力板,所述散热器靠近所述算力板设置。

10、本申请通过将第一反相器的源极区设计在第二区域内位于靠近第一区域的一侧,第一反相器的漏极区在第二区域内位于远离第一区域的一侧,可以有效减少由于cnod工艺寄生出的晶体管而造成的漏电。

技术特征:

1.一种动态锁存器,其特征在于,包括:

2.根据权利要求1所述的动态锁存器,其特征在于,所述传输门和所述数据输出单元之间设置有至少一个用于填充的空单元。

3.根据权利要求2所述的动态锁存器,其特征在于,所述空单元内的氧化物扩散区连接预设电压。

4.根据权利要求1所述的动态锁存器,其特征在于,所述动态锁存器还包括二极管单元;所述二极管单元设于所述衬底的第三区域,所述第三区域位于所述第一区域和所述第二区域之间。

5.根据权利要求4所述的动态锁存器,其特征在于,所述二极管单元包括pmos管和nmos管;所述pmos管的栅极与所述pmos管的源极连接,所述nmos管的栅极与所述nmos管的源极连接,所述pmos管的源极与所述nmos管的源极连接。

6.根据权利要求5所述的动态锁存器,其特征在于,所述pmos管的漏极区和所述nmos管的漏极区在所述第三区域内位于靠近所述第一区域的一侧;所述pmos管的源极区和所述nmos管的源极区在所述第三区域内位于靠近所述第二区域的一侧。

7.根据权利要求1所述的动态锁存器,其特征在于,所述数据输出单元还包括第二反相器;所述第二反相器的输入端与所述第一反相器的输出端连接。

8.根据权利要求7所述的动态锁存器,其特征在于,所述第一反相器和所述第二反相器共用同一个源极区;

9.根据权利要求7所述的动态锁存器,其特征在于,所述第一反相器中pmos管的源极和所述第二反相器中pmos管的源极连接同一个漏极电压源;所述第一反相器中nmos管的源极和所述第二反相器中nmos管的源极连接同一个源极电压源。

10.根据权利要求1-9任一项所述的动态锁存器,其特征在于,所述传输门包括第一时钟信号输入端和第二时钟信号输入端;

11.一种半导体芯片,其特征在于,包括一个或多个如权利要求1-10任一项所述的动态锁存器。

12.一种算力板,其特征在于,包括一个或多个如权利要求11所述的半导体芯片。

13.一种计算设备,其特征在于,包括电源板、控制板、连接板、散热器以及多个如权利要求12所述的算力板;所述电源板分别连接所述控制板、所述连接板、所述散热器以及各所述算力板;所述控制板通过所述连接板连接所述算力板,所述散热器靠近所述算力板设置。

技术总结

本申请提供一种动态锁存器、半导体芯片、算力板及计算设备,动态锁存器包括:衬底;传输门,设于所述衬底的第一区域;数据输出单元,设于所述衬底的第二区域,且包括第一反相器;所述第一反相器的输入端与所述传输门的输出端连接;其中,所述第一区域与所述第二区域邻接且两个区域内的氧化物扩散区是连续的;其中,所述第一反相器的源极区在所述第二区域内位于靠近所述第一区域的一侧,所述第一反相器的漏极区在所述第二区域内位于远离所述第一区域的一侧。在半导体器件的制作方式下,通过对动态锁存器中的第一反相器的源极区靠近传输门以及漏极区远离传输门的设置,可以有效减少由于寄生晶体管导致的漏电,从而保证动态锁存器的逻辑正确。

技术研发人员:闫浩,王磊,赵安

受保护的技术使用者:北京比特大陆科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!