屏蔽栅沟槽型半导体器件的制造方法与流程

1.本发明涉及一种半导体集成电路制造方法,特别是涉及一种屏蔽栅沟槽型(sgt)半导体器件的制造方法。

背景技术:

2.sgt中引入源多晶硅(source poly)来承担电荷耦合(charge-coupled)结构在mosfet中的作用,因此在器件设计上,需要增加源多晶硅引出(source poly linkup)区域来引出位于栅沟槽内多晶硅栅(gate poly)下方的源多晶硅(source poly)。

3.在sgt的制造工艺流程中,形成source poly linkup结构形貌通常需要3~4层光刻,分别为trench/(poly1)/p-cover/contact,这里,trench表示沟槽光刻,poly1表示多晶硅栅的光刻,p-cover表示多晶硅间氧化层(ipo)的光刻,contact表示接触孔的光刻。

4.在某些sgt的制造工艺流程中,也可以不使用poly1光刻的掩模版,而直接以深接触孔(deep contact)工艺来将source poly接出。

5.但p-cover掩模版是现有工艺中不可缺少的,其作用主要是为了在湿法刻蚀形成ipo的过程中保护source poly linkup区域的氧化膜,避免在后续的gate poly淀积中在source poly linkup区域残留gate poly,进而使原本连接源极的接触孔同时连接栅极,导致栅源短接使器件失效。

6.如图1所示,是现有一种屏蔽栅沟槽型半导体器件的制造方法采用的版图结构;如图2a至图2g所示,是现有一种屏蔽栅沟槽型半导体器件的制造方法各步骤中的器件结构示意图;现有一种屏蔽栅沟槽型半导体器件的制造方法包括如下步骤:

7.步骤一、如图2a所示,采用光刻定义加刻蚀工艺在半导体衬底上形成多个沟槽201,所述沟槽201包括多个栅沟槽以及至少一个源引出沟槽,所述栅沟槽形成于器件单元区,所述源引出沟槽位于所述器件单元区外侧,所述源引出沟槽和各所述栅沟槽相连通,所述源引出沟槽的宽度和所述栅沟槽的宽度相等。

8.所述半导体衬底为硅衬底。

9.由图1所示的版图可知,所述栅沟槽和所述源引出沟槽都为所述沟槽201的一部分。其中,区域101是由poly1的掩模版定义的区域,区域102则由p-cover掩模版定义的区域,区域102会大于区域101,在区域102中的所述沟槽201都为所述源引出沟槽。下面描述中,省略了定义区域101的poly1的掩模版和对应的光刻工艺。

10.步骤二、如图2a所示,形成底部介质层202和源极多晶硅203,所述底部介质层202覆盖在所述沟槽201的底部表面和所述沟槽201的底部区域的侧面,所述源极多晶硅203填充在形成有所述底部介质层202的所述沟槽201的底部区域。

11.通常,所述底部介质层202为氧化层。

12.所述源极多晶硅203采用多晶硅淀积加回刻工艺形成。

13.步骤三、如图2a所示,采用高密度等离子体(hdp)化学气相沉积(cvd)淀积多晶硅间氧化层204a;hdp cvd淀积的所述多晶硅间氧化层204a的厚度满足将各所述沟槽201的顶

部区域完全填充。

14.之后,如图2a所示,进行光刻定义将所述源引出沟槽的顶部保护,光刻工艺采用p-cover掩模版并形成光刻胶图形102a来将所述源引出沟槽的顶部保护。

15.之后进行多晶硅间氧化层204a的回刻,回刻后,所述栅沟槽中的多晶硅间氧化层204位于所述源极多晶硅203的表面并单独用标记204表示;所述源引出沟槽的顶部由于受到光刻保护而使得所述源引出沟槽的顶部区域完全填充由标记204a单独标出的多晶硅间氧化层。

16.步骤四、如图2c所示,在所述多晶硅间氧化层204顶部的所述沟槽201的侧面形成栅介质层205。

17.通常,所述栅介质层205为采用热氧化工艺生长的栅氧化层。

18.步骤五、如图2d所示,进行多晶硅淀积形成第二多晶硅层206a,所述第二多晶硅层206a将所述栅沟槽的所述源极多晶硅203的顶部区域完全填充,所述第二多晶硅层206a还延伸到所述栅沟槽的外侧。

19.步骤六、如图2e所示,对所述第二多晶硅层206a进行回刻,回刻后的所述第二多晶硅层206a仅填充在所述栅沟槽中并组成多晶硅栅206。

20.在所述多晶硅栅206形成之后以及后续的金属下介质层207形成之前还包括形成体区和源区的步骤。

21.所述体区形成在所述器件单元区和所述器件单元区外侧的所述半导体衬底上,各所述沟槽201的深度大于所述体区的结深。

22.所述源区形成在所述器件单元区的所述体区表面,被所述多晶硅栅206侧面覆盖的所述体区表面用于形成沟道。

23.步骤七、如图2f所示,进行金属下介质层207生长到所需要的目标厚度,目标厚度即为所述金属下介质层207位于所述半导体衬底表面上的厚度。通常,所述金属下介质层207采用硼磷硅玻璃。

24.步骤八、如图2g所示,根据光刻定义进行刻蚀形成接触孔208的开口。所述接触孔208的开口的刻蚀包括介质层刻蚀以及半导体材料刻蚀。所述接触孔208包括位于所述源引出沟槽中的所述第一接触孔208a,所述第一接触孔208a穿过所述金属下介质层207。

25.之后在所述接触孔208的开口中填充金属。

26.之后形成正面金属层并图形化形成源极和栅极。

27.由上可知,现有方法需要在步骤三中需要单独采用一次光刻工艺将所述源引出沟槽的顶部保护,具有较高的成本。

技术实现要素:

28.本发明所要解决的技术问题是提供一种屏蔽栅沟槽型半导体器件的制造方法,能减少形成ipo的掩模版,从而能降低工艺成本。

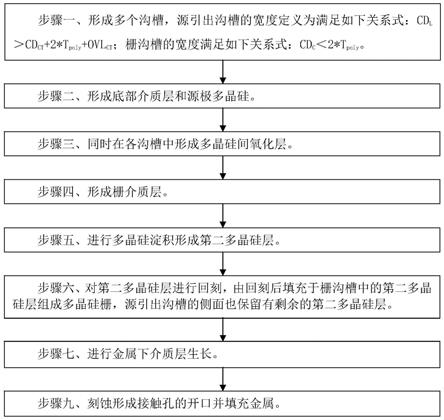

29.为解决上述技术问题,本发明提供的屏蔽栅沟槽型半导体器件的制造方法包括如下步骤:

30.步骤一、采用光刻定义加刻蚀工艺在半导体衬底上形成多个沟槽,所述沟槽包括多个栅沟槽以及至少一个源引出沟槽,所述栅沟槽形成于器件单元区,所述源引出沟槽位

于所述器件单元区外侧,所述源引出沟槽和各所述栅沟槽相连通,所述源引出沟槽的宽度定义为满足如下关系式:

31.cd

l

>cd

ct

+2*t

poly

+ovl

ct

。

32.其中cd

l

表示所述源引出沟槽的宽度,cd

ct

表示后续形成的所述源引出沟槽中的第一接触孔的宽度,t

poly

表示后续淀积的所述第二多晶硅层的厚度,ovl

ct

表示接触孔的工艺波动偏差量。

33.所述栅沟槽的宽度满足如下关系式:

34.cdc<2*t

poly

;

35.cdc表示所述栅沟槽的宽度。

36.步骤二、形成底部介质层和源极多晶硅,所述底部介质层覆盖在所述沟槽的底部表面和所述沟槽的底部区域的侧面,所述源极多晶硅填充在形成有所述底部介质层的所述沟槽的底部区域。

37.步骤三、采用相同的工艺同时在各所述沟槽中形成多晶硅间氧化层,所述多晶硅间氧化层覆盖在所述源极多晶硅的表面。

38.步骤四、在所述多晶硅间氧化层顶部的所述沟槽的侧面形成栅介质层。

39.步骤五、进行多晶硅淀积形成第二多晶硅层,所述第二多晶硅层的厚度为t

ploy

,t

poly

和cd

l

以及cdc的关系使得,所述第二多晶硅层将所述栅沟槽的所述源极多晶硅的顶部区域完全填充以及所述第二多晶硅层未将所述源引出沟槽的所述源极多晶硅的顶部区域完全填充并形成有间隙区,所述第二多晶硅层还延伸到所述沟槽的外侧。

40.步骤六、对所述第二多晶硅层进行回刻,回刻后的所述第二多晶硅层仅填充在所述栅沟槽中以及位于所述源引出沟槽的侧面,所述源引出沟槽的所述源极多晶硅的顶部表面以及所述沟槽外的所述第二多晶硅层都被去除,由填充于所述栅沟槽中的所述第二多晶硅层组成多晶硅栅。

41.步骤七、进行金属下介质层生长,所述金属下介质层会将所述源引出沟槽中的间隙区完全填充。

42.步骤八、根据光刻定义进行刻蚀形成接触孔的开口,之后在所述接触孔的开口中填充金属;所述接触孔包括位于所述源引出沟槽中的所述第一接触孔,所述第一接触孔穿过所述金属下介质层。

43.进一步的改进是,所述半导体衬底为硅衬底。

44.进一步的改进是,步骤二中所述底部介质层为氧化层。

45.进一步的改进是,步骤二中所述源极多晶硅采用多晶硅淀积加回刻工艺形成。

46.进一步的改进是,所述底部介质层采用热氧化工艺或淀积工艺生长形成,生长后的所述底部介质层覆盖在所述沟槽的内侧表面和所述沟槽的外侧表面;在所述源极多晶硅的回刻工艺之后,所述源极多晶硅的顶部的所述沟槽侧面和所述沟槽外侧表面的所述底部介质层被去除。

47.进一步的改进是,步骤三包括如下分步骤:

48.步骤31、进行氧化层生长形成所述多晶硅间氧化层;

49.步骤32、进行湿法刻蚀将所述多晶硅间氧化层回刻到所需要的厚度。

50.进一步的改进是,步骤31中生长所述多晶硅间氧化层的工艺包括hdp cvd工艺。

51.进一步的改进是,步骤三中,所述多晶硅间氧化层将所述源极多晶硅顶部的所述沟槽填满或者部分填充。

52.进一步的改进是,所述源极多晶硅的顶部的所述沟槽侧面和所述沟槽外侧表面的所述底部介质层在步骤31生长所述多晶硅间氧化层之前被去除;或者,所述源极多晶硅的顶部的所述沟槽侧面和所述沟槽外侧表面的所述底部介质层同时采用步骤32的湿法刻蚀去除。

53.进一步的改进是,步骤四中所述栅介质层为采用热氧化工艺生长的栅氧化层。

54.进一步的改进是,在步骤六的所述多晶硅栅形成之后以及所述金属下介质层形成之前还包括形成体区和源区的步骤;

55.所述体区形成在所述器件单元区和所述器件单元区外侧的所述半导体衬底上,各所述沟槽的深度大于所述体区的结深;

56.所述源区形成在所述器件单元区的所述体区表面,被所述多晶硅栅侧面覆盖的所述体区表面用于形成沟道。

57.进一步的改进是,在步骤八的所述接触孔的开口的金属填充完成之后,还包括形成正面金属层,对所述正面金属层进行图形化形成源极和栅极的步骤;所述源极通过接触孔和所述源区接触以及通过所述第一接触孔和所述源极多晶硅接触。

58.进一步的改进是,所述源极和所述栅极形成之后,还包括对所述半导体衬底进行背面减薄,在所述半导体衬底的背面形成漏区以及在所述漏区的背面形成由背面金属层组成的漏极的步骤。

59.进一步的改进是,步骤八中的所述接触孔的开口的刻蚀包括介质层刻蚀以及半导体材料刻蚀。

60.进一步的改进是,步骤七中所述金属下介质层采用硼磷硅玻璃。

61.进一步的改进是,步骤一中,所述源引出沟槽的长度定义为满足如下关系式:

62.l

l

>l

ct

+2*t

poly

+ovl

ct

;

63.其中l

l

表示所述源引出沟槽的长度,l

ct

表示后续形成的所述源引出沟槽中的第一接触孔的长度。

64.本发明结合多晶硅栅对应的第二多晶硅层沉积后和接触孔的尺寸预先定义源引出沟槽的尺寸,使得在形成栅沟槽中的结构时,源引出沟槽中的结构也能同时一并进行,并不需要额外增加掩模版和对应的光刻工艺,也即不需要增加poly1掩模版和对应的光刻工艺以及不需要增加p-cover掩模版和对应的光刻工艺;现有工艺中,poly1掩模版用于在源多晶硅的刻蚀中覆盖源引出沟槽区域,poly1可以省略;但是,p-cover掩模版用于在刻蚀形成ipo中覆盖源引出沟槽的区域,现有工艺中无法省略p-cover掩模版和对应的光刻工艺,所以,本发明能减少形成ipo的掩模版,从而能降低工艺成本。

附图说明

65.下面结合附图和具体实施方式对本发明作进一步详细的说明:

66.图1是现有一种屏蔽栅沟槽型半导体器件的制造方法采用的版图结构;

67.图2a-图2g是现有一种屏蔽栅沟槽型半导体器件的制造方法各步骤中的器件结构示意图;

68.图3是本发明实施例屏蔽栅沟槽型半导体器件的制造方法的流程图;

69.图4是本发明实施例屏蔽栅沟槽型半导体器件的制造方法采用的版图结构;

70.图4a是图4中源多晶硅引出结构处的放大图;

71.图5a-图5f是本发明实施例屏蔽栅沟槽型半导体器件的制造方法各步骤中的器件结构示意图。

具体实施方式

72.如图3所示,是本发明实施例屏蔽栅沟槽401型半导体器件的制造方法的流程图;如图4所示,是本发明实施例屏蔽栅沟槽401型半导体器件的制造方法采用的版图结构;如图4a所示,是图4中源多晶硅引出结构处的放大图;如图5a至图5f所示,是本发明实施例屏蔽栅沟槽401型半导体器件的制造方法各步骤中的器件结构示意图;本发明实施例屏蔽栅沟槽401型半导体器件的制造方法包括如下步骤:

73.步骤一、如图5a所示,采用光刻定义加刻蚀工艺在半导体衬底上形成多个沟槽,所述沟槽包括多个栅沟槽401以及至少一个源引出沟槽401a,所述栅沟槽401形成于器件单元区301,所述源引出沟槽401a位于所述器件单元区301外侧即图4中的源多晶硅引出区域302中,所述源引出沟槽401a和各所述栅沟槽401相连通。

74.如图4a所示,所述源引出沟槽401a的宽度定义为满足如下关系式:

75.cd

l

>cd

ct

+2*t

poly

+ovl

ct

(1);

76.其中cd

l

表示所述源引出沟槽401a的宽度,cd

ct

表示后续形成的所述源引出沟槽401a中的第一接触孔408a的宽度,t

poly

表示后续淀积的所述第二多晶硅层406a的厚度,ovl

ct

表示接触孔408的工艺波动偏差量。

77.所述栅沟槽401的宽度满足如下关系式:

78.cdc<2*t

poly

(2);

79.cdc表示所述栅沟槽401的宽度。

80.公式(1)和(2)合起来表示为:

81.cdc/2<t

poly

<(cd

l-cd

ct-ovl

ct

)/2(3)。

82.本发明实施例中,所述源引出沟槽401a的长度定义为满足如下关系式:

83.l

l

>l

ct

+2*t

poly

+ovl

ct

(4);

84.其中l

l

表示所述源引出沟槽401a的长度,l

ct

表示后续形成的所述源引出沟槽401a中的第一接触孔408a的长度。

85.所述半导体衬底为硅衬底。

86.步骤二、如图5a所示,形成底部介质层402和源极多晶硅403,所述底部介质层402覆盖在所述沟槽的底部表面和所述沟槽的底部区域的侧面,所述源极多晶硅403填充在形成有所述底部介质层402的所述沟槽的底部区域。

87.本发明实施例中,所述底部介质层402为氧化层。

88.所述源极多晶硅403采用多晶硅淀积加回刻工艺形成。

89.所述底部介质层402采用热氧化工艺或淀积工艺生长形成,生长后的所述底部介质层402覆盖在所述沟槽的内侧表面和所述沟槽的外侧表面。

90.在所述源极多晶硅403的回刻工艺之后,所述源极多晶硅403的顶部的所述沟槽侧

面和所述沟槽外侧表面的所述底部介质层402被去除。

91.步骤三、如图5a所示,采用相同的工艺同时在各所述沟槽中形成多晶硅间氧化层404,所述多晶硅间氧化层404覆盖在所述源极多晶硅403的表面。

92.本发明实施例中,步骤三包括如下分步骤:

93.步骤31、进行氧化层生长形成所述多晶硅间氧化层404。

94.较佳为,步骤31中生长所述多晶硅间氧化层404的工艺包括hdp cvd工艺。

95.所述多晶硅间氧化层404将所述源极多晶硅403顶部的所述沟槽填满或者部分填充。

96.步骤32、进行湿法刻蚀将所述多晶硅间氧化层404回刻到所需要的厚度。

97.如果步骤31中,所述多晶硅间氧化层404将所述源极多晶硅403顶部的所述沟槽填满,则步骤32之前还包括进行化学机械研磨工艺,以使所述多晶硅间氧化层404的表面平坦化。

98.所述源极多晶硅403的顶部的所述沟槽侧面和所述沟槽外侧表面的所述底部介质层402在步骤31生长所述多晶硅间氧化层404之前被去除。在其他实施例中也能为:所述源极多晶硅403的顶部的所述沟槽侧面和所述沟槽外侧表面的所述底部介质层402同时采用步骤32的湿法刻蚀去除。

99.步骤四、如图5b所示,在所述多晶硅间氧化层404顶部的所述沟槽的侧面形成栅介质层405。

100.本发明实施例中,步骤四中所述栅介质层405为采用热氧化工艺生长的栅氧化层。

101.步骤五、如图5c所示,进行多晶硅淀积形成第二多晶硅层406a,所述第二多晶硅层406a的厚度为t

ploy

,t

poly

和cd

l

以及cdc的关系使得,所述第二多晶硅层406a将所述栅沟槽401的所述源极多晶硅403的顶部区域完全填充以及所述第二多晶硅层406a未将所述源引出沟槽401a的所述源极多晶硅403的顶部区域完全填充并形成有间隙区,所述第二多晶硅层406a还延伸到所述沟槽的外侧。

102.步骤六、如图5d所示,对所述第二多晶硅层406a进行回刻,回刻后的所述第二多晶硅层406a仅填充在所述栅沟槽401中以及位于所述源引出沟槽401a的侧面,所述源引出沟槽401a的所述源极多晶硅403的顶部表面以及所述沟槽外的所述第二多晶硅层406a都被去除,由填充于所述栅沟槽401中的所述第二多晶硅层406a组成多晶硅栅406。

103.本发明实施例中,在步骤六的所述多晶硅栅406形成之后以及所述金属下介质层407形成之前还包括形成体区和源区的步骤;

104.所述体区形成在所述器件单元区301和所述器件单元区301外侧的所述半导体衬底上,各所述沟槽的深度大于所述体区的结深;

105.所述源区形成在所述器件单元区301的所述体区表面,被所述多晶硅栅406侧面覆盖的所述体区表面用于形成沟道。

106.步骤七、如图5e所示,进行金属下介质层407生长,所述金属下介质层407会将所述源引出沟槽401a中的间隙区完全填充,也即所述金属下介质层407除了能覆盖在栅极结构表面、源多晶硅引出结构的表面以及栅极结构和源多晶硅引出结构之外的区域表面外,还能同时将所述源引出沟槽401a中的间隙区完全填充。所述栅极结构即为由形成于所述栅沟槽401中的所述底部介质层402、所述源多晶硅403、所述多晶硅间氧化层404、所述栅介质层

405和所述多晶硅栅406叠加而成的结构。所述源引出结构则包括形成于所述源引出沟槽401a中的所述底部介质层402、所述源多晶硅403和所述多晶硅间氧化层404。

107.本发明实施例中,所述金属下介质层407采用硼磷硅玻璃。

108.步骤八、如图5f所示,根据光刻定义进行刻蚀形成接触孔408的开口,之后在所述接触孔408的开口中填充金属;所述接触孔408包括位于所述源引出沟槽401a中的所述第一接触孔408a,所述第一接触孔408a穿过所述金属下介质层407。

109.在步骤八的所述接触孔408的开口的金属填充完成之后,还包括形成正面金属层,对所述正面金属层进行图形化形成源极和栅极的步骤;所述源极通过接触孔408和所述源区接触以及通过所述第一接触孔408a和所述源极多晶硅403接触。

110.所述源极和所述栅极形成之后,还包括对所述半导体衬底进行背面减薄,在所述半导体衬底的背面形成漏区以及在所述漏区的背面形成由背面金属层组成的漏极的步骤。

111.本发明实施例中,所述接触孔408的开口的刻蚀包括介质层刻蚀以及半导体材料刻蚀。

112.本发明实施例结合多晶硅栅406对应的第二多晶硅层406a沉积后和接触孔408的尺寸预先定义源引出沟槽401a的尺寸,使得在形成栅沟槽401中的结构时,源引出沟槽401a中的结构也能同时一并进行,并不需要额外增加掩模版和对应的光刻工艺,也即不需要增加poly1掩模版和对应的光刻工艺以及不需要增加p-cover掩模版和对应的光刻工艺;现有工艺中,poly1掩模版用于在源多晶硅的刻蚀中覆盖源引出沟槽401a区域,poly1可以省略;但是,p-cover掩模版用于在刻蚀形成ipo中覆盖源引出沟槽401a的区域,现有工艺中无法省略p-cover掩模版和对应的光刻工艺,所以,本发明实施例能减少形成ipo的掩模版,从而能降低工艺成本。

113.以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1