各向异性导电片、各向异性导电片的制造方法、电气检查装置及电气检查方法与流程

1.本发明涉及各向异性导电片、各向异性导电片的制造方法、电气检查装置及电气检查方法。

背景技术:

2.对于搭载于电子产品的印刷电路板等半导体器件,通常进行电气检查。一般地,通过使电气检查装置的(具有电极的)基板与半导体器件等作为检查对象的端子电接触,并读取在检查对象的端子间施加规定的电压时的电流来进行电气检查。而且,为了可靠地进行电气检查装置的基板的电极与检查对象的端子之间的电接触,在电气检查装置的基板与检查对象之间配置各向异性导电片。

3.各向异性导电片是在厚度方向上具有导电性且在面方向上具有绝缘性的片,被作为电气检查中的探头(接触器)使用。为了可靠地进行电气检查装置的基板与检查对象之间的电连接,施加压入负荷而使用这样的各向异性导电片。因此,各向异性导电片需要在厚度方向上容易弹性变形。

4.作为这样的各向异性导电片,已知一种各向异性导电片(例如专利文献1),其具有:由硅橡胶等构成的绝缘层、和以在绝缘层的厚度方向上贯穿的方式配置的多个金属丝。另外,已知一种电连接器(例如参照专利文献2),其具有:具有在厚度方向上贯穿的多个通孔的弹性体(例如硅橡胶片)、和接合于通孔的内壁面的中空状的多个导电部件。

5.现有技术文献

6.专利文献

7.专利文献1:日本专利特开2016-213186号公报。

8.专利文献2:国际公开第2018/212277号

技术实现要素:

9.发明要解决的问题

10.近年来,要求进一步降低电气检查时的压入负荷,正在研究金属丝、导电部件等导电通路的构成材料的进一步的低弹性模量化。但是,存在以下问题:越使导电通路的构成材料低弹性模量化,则越容易因重复由压入负荷引起的加压和减压而使导电通路从绝缘层剥离。在专利文献1和2中,也存在同样的问题。

11.本发明是鉴于上述问题而完成的,其目的在于,提供即使重复弹性变形,导电通路的剥离也较少,且能够保持良好的密合性的各向异性导电片、各向异性导电片的制造方法、电气检查装置及电气检查方法。

12.解决问题的方案

13.上述问题能够通过以下结构来解决。

14.本发明的各向异性导电片具有:绝缘层,具有位于厚度方向上的一侧的第一面、以

及位于另一侧的第二面;以及多个导电通路,在所述绝缘层内以沿所述厚度方向延伸的方式配置,且分别在所述第一面和所述第二面向外部露出,所述导电通路的周面包含如下区域,该区域的由下式(1)表示的表面积率为1.04以上,

15.式(1):表面积率=表面积/面积。

16.本发明的各向异性导电片的制造方法包括以下工序:准备多个单元的工序,该单元具有绝缘层、和配置于所述绝缘层上且周面包含如下区域的多个导电线,该区域的由下式(1)表示的表面积率为1.04以上;将多个所述单元层叠并一体化,来得到层叠体的工序;以及沿着所述层叠体的层叠方向,以与所述多个导电线的延伸方向交叉的方式进行切割,来得到各向异性导电片的工序,

17.式(1):表面积率=表面积/面积。

18.本发明的电气检查装置具有:具有多个电极的检查用基板;以及本发明的各向异性导电片,该各向异性导电片配置在所述检查用基板的配置有所述多个电极的面上。

19.本发明的电气检查方法包括如下工序,该工序中,以隔着本发明的各向异性导电片的方式,将具有多个电极的检查用基板和具有端子的检查对象层叠起来,使所述检查用基板的所述电极与所述检查对象的所述端子通过所述各向异性导电片电连接。

20.发明效果

21.根据本发明,可以提供即使重复弹性变形,导电通路的剥离也较少且能够保持良好的密合性的各向异性导电片、各向异性导电片的制造方法、电气检查装置及电气检查方法。

附图说明

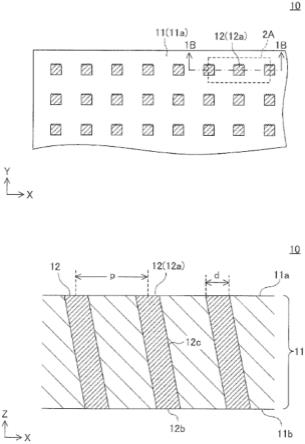

22.图1a是表示本实施方式的各向异性导电片的局部放大俯视图,图1b是图1a的各向异性导电片的1b-1b线的放大剖面图。

23.图2a是图1a的各向异性导电片的局部放大图,图2b是其他实施方式的各向异性导电片的局部放大图。

24.图3a~图3f是表示本实施方式的各向异性导电片的制造方法的一部分的工序的剖面示意图。

25.图4a~图4c是表示本实施方式的各向异性导电片的制造方法的剩余的工序的示意图。

26.图5是表示本实施方式的电气检查装置的剖面图。

27.图6是其他实施方式的各向异性导电片的局部放大剖面图。

具体实施方式

28.1.各向异性导电片

29.图1a是本实施方式的各向异性导电片10的局部放大俯视图,图1b是图1a的各向异性导电片10的1b-1b线的放大剖面图。图2是图1b的放大图。在这些图中,将绝缘层11的厚度方向表示为z方向,将在与绝缘层11的厚度方向正交的平面上正交的两个方向表示为x方向、y方向。以下的附图都是示意图,且比例等与实际不同。

30.各向异性导电片10具有:绝缘层11;以及在该绝缘层11的内部以沿其厚度方向延

伸的方式配置的多个导电通路12。

31.1-1.绝缘层11

32.绝缘层11是具有位于厚度方向上的一侧的第一面11a、和位于厚度方向的另一侧的第二面11b的层(参照图1a及图1b)。绝缘层11将多个导电通路12彼此之间绝缘。在本实施方式中,优选地,在绝缘层11的第一面11a上配置检查对象。

33.绝缘层11可以包含如下的交联物,该交联物是含有原料橡胶(聚合物)的橡胶组合物的交联物。

34.原料橡胶的例子包括:硅橡胶、聚氨酯橡胶、丙烯酸橡胶、乙烯-丙烯-二烯共聚物(epdm)、氯丁二烯橡胶、苯乙烯-丁二烯共聚物、丙烯腈-丁二烯共聚物、聚丁二烯橡胶、天然橡胶、聚酯类热塑性弹性体、烯烃类热塑性弹性体等。其中,从具有良好的绝缘性和弹性考虑,硅橡胶是优选的。硅橡胶可以是加成交联型、过氧化物交联型、缩合交联型中的任意一种。

35.橡胶组合物还可以根据需要包含交联剂。交联剂可以根据原料橡胶的种类适当选择。例如,过氧化物交联型硅橡胶的交联剂的例子包括:过氧化苯甲酰、过氧化双(2,4-二氯苯甲酰)、过氧化二异丙苯以及二叔丁基过氧化物等有机过氧化物。加成交联型硅橡胶的交联剂的例子包括:具有氢化硅烷化反应的催化活性的金属、金属化合物、金属络合物等(铂、铂化合物、它们的络合物)。

36.例如,加成交联型的硅橡胶组合物包含:(a)具有乙烯基的有机聚硅氧烷;(b)具有sih基的有机氢聚硅氧烷;以及(c)加成反应催化剂。

37.例如从调整硬度等的观点考虑,橡胶组合物还可以根据需要包含增粘剂、硅烷偶联剂、填料等其他成分。

38.从易弹性变形的观点等考虑,绝缘层11也可以形成为多孔。

39.不特别地限定橡胶组合物的交联物的25℃下的硬度,只要是能够通过电气检查时的压入负荷而弹性变形的程度的硬度即可,但是,例如优选为,以jis(日本工业标准)k6253硬度计类型a测定的硬度为40~90度。

40.不特别地限定绝缘层11的厚度,只要是能够确保非导通部分的绝缘性的程度的厚度即可,但是,例如优选为5~300μm,更优选为10~100μm。

41.1-2.导电通路12

42.导电通路12在绝缘层11内,以在其厚度方向上延伸且分别在第一面11a和第二面11b露出的方式配置(参照图1b)。

43.具体而言,导电通路12在绝缘层11的厚度方向上延伸所指的是:导电通路12的轴向与绝缘层11的厚度方向大致平行(具体而言,绝缘层11的厚度方向与导电通路12的轴向所成的角度中的较小的角度为10

°

以下),或在规定的范围内倾斜(绝缘层11的厚度方向与导电通路12的轴向所成的角度中的较小的角度超过10

°

且在50

°

以下,优选为20

°

~45

°

)。其中,从在施加压入负荷时容易弹性变形且容易电连接的观点考虑,优选为,导电通路12的轴向相对于绝缘层11的厚度方向倾斜(参照图1b)。应予说明,轴向是指将导电通路12的第一面11a侧的端部12a与第二面11b侧的端部12b连结的方向。即,导电通路12以端部12a在第一面11a侧露出,且端部12b在第二面11b侧露出的方式配置(参照图1b)。

44.导电通路12的第一面11a侧的端部12a(或第二面11b侧的端部12b)也可以从绝缘

层11的第一面11a(或第二面11b)突出(参照后述的图6)。

45.导电通路12的周面是导电通路12的与绝缘层11接触的面,其配置于两个端部12a、12b之间。

46.本发明的发明人研究了导电通路12与绝缘层11的密合性,并发现,导电通路12的周面的表面积率与密合性具有相关关系。表面积率是指相对于规定的区域的面积的、该区域的表面积的比例,由下式(1)表示。即,优选地,导电通路12的周面包含如下区域,该区域的由下式(1)表示的表面积率为1.04以上。表面积率为1.04以上的区域中,对与绝缘层11的接触作出贡献的面积(表面积)的比例高,因此,容易得到与绝缘层11之间的密合性。

47.式(1):表面积率=表面积/面积

[0048]“区域的表面积”是指用激光显微镜等测定的该区域的三维的面积。“区域的面积”是从法线方向观察该区域的面时看到的区域的大小,是指区域的二维的面积(平面面积)。

[0049]

其中,从提高导电通路12与绝缘层11之间的密合性,且不易损害各向异性导电片10的高频特性的观点考虑,上述的面的表面积率更优选为1.04~1.4,进一步优选为1.1~1.3。

[0050]

导电通路12的表面积率可以以如下方式求得:利用激光显微镜等测定规定的区域(测定区域)的表面积,并以所得到的表面积除以利用激光显微镜等测定的上述区域的面积而求出。应予说明,表面积及面积的测定均分别进行3次(n=3),针对每次测定分别计算表面积率,并将它们的平均值设为“表面积率”。可将测定区域设为纵向250μm

×

横向250μm。

[0051]

优选地,表面积率为1.04以上的区域是被粗糙化处理的区域(粗糙面)。因此,可以通过上述区域的凹凸形状(例如凸部的高度、存在密度)来调整上述区域的表面积率。例如,可以通过调整对于成为导电通路12的原料的金属箔的粗糙面的处理条件,来调整上述区域的凹凸形状。

[0052]

应予说明,作为表面物性,也已知表面粗糙度rz,但是,在本发明的发明人的研究中,未确认到导电通路12的周面的表面粗糙度rz与密合性之间的相关关系。可以推测这是因为,对表面积的提高(密合性的提高)不做贡献那样的宽大的凹凸也容易被反映在表面粗糙度rz中。

[0053]

这样,导电通路12的周面包含表面积率高的区域,由此能够提高与绝缘层11之间的密合性。另一方面,若表面积率高的区域所占的比例过多,则容易损害高频特性。因此,从不损害高频特性的观点考虑,优选地,导电通路12的周面还包含表面积率低于1.04的区域(平滑面)。

[0054]

不特别地限定表面积率为1.04以上的区域与表面积率低于1.04的区域之间的表面积率之差,但该表面积率之差例如可以为0.05以上。

[0055]

不特别限定表面积率为1.04以上的区域所占的比例,但是,该比例例如可以为导电通路12的周面的25~75%。

[0056]

不特别地限定导电通路12的形状,该形状例如可以是棱柱状。在本实施方式中,导电通路12的形状为四棱柱状(参照图1a及图1b)。

[0057]

四棱柱状的导电通路12具有四个侧面,具体而言,相对置的第一侧面12c和第二侧面12d、以及相对置的第三侧面12e和第四侧面12f(参照图2a及图2b)。而且,优选地,相对置的第一侧面12c和第二侧面12d中的至少一者是包含表面积率为1.04以上的区域的粗糙面,

相对置的第三侧面12e和第四侧面12f是包含表面积率低于1.04的区域的平滑面。

[0058]

在本实施方式中,导电通路12的第一侧面12c是由表面积率为1.04以上的区域构成的粗糙面,其以外的第二侧面12d、第三侧面12e及第四侧面12f是由表面积率低于1.04的区域构成的平滑面(参照图2a)。应予说明,也可以是,第一侧面12c和第二侧面12d这两者是表面积率为1.04以上的粗糙面(参照图2b)。

[0059]

导电通路12的第一面11a侧的端部12a的等效圆直径d只要为如下程度即可,即,只要是能将多个导电通路12的端部12a在第一面11a侧的中心间距离p调整为后述的范围,且能确保检查对象的端子与导电通路12之间的导通的程度即可,等效圆直径d例如优选为2~30μm(参照图1b)。第一面11a侧的、导电通路12的端部12a的等效圆直径d是指,从第一面11a侧沿绝缘层11的厚度方向观察时的导电通路12的端部12a的等效圆直径。

[0060]

在本实施方式中,对于由导电通路12的第一侧面12c与第二侧面12d之间的距离表示的厚度(t),也以使等效圆直径d能满足上述范围的方式设定该厚度(t)。该厚度(t)与后述的金属箔21的厚度对应,例如可以是1~35μm(参照图2a)。

[0061]

导电通路12的第一面11a侧的端部12a的等效圆直径、和第二面11b侧的端部12b的等效圆直径可以相同(参照图1b),也可以不同。

[0062]

不特别地限定第一面11a侧的、多个导电通路12的中心间距离(间距)p,可以与检查对象的端子的间距对应地适当设定。考虑到作为检查对象的hbm(high bandwidth memory,高带宽存储器)的端子的间距为55μm,以及pop(package on package,叠层封装)的端子的间距为400~650μm等情况,从与这些检查对象配合的观点考虑,第一面11a侧的、多个导电通路12的端部12a的中心间距离p例如可以为5~650μm。其中,从不需要检查对象的端子的位置对准(实现无需对准(alignment-free))的观点考虑,更优选地,第一面11a侧的、多个导电通路12的中心间距离p为5~55μm。多个导电通路12的中心间距离p是指多个导电通路12的中心间距离中的最小值。

[0063]

第一面11a侧的多个导电通路12的中心间距离p与第二面11b侧的多个导电通路12的中心间距离可以相同(参照图1b),也可以不同。

[0064]

不特别限定构成导电通路12的材料,只要是具有导电性的材料即可。不特别地限定构成导电通路12的材料的体积电阻率,只要是能够得到足够的导通的程度的体积电阻率即可,但例如优选为1.0

×

10-4

ω

·

m以下,更优选为1.0

×

10-6

ω

·

m~1.0

×

10-9

ω

·

m。可以按照美国测试和材料学会标准astm d991中记载的方法测定体积电阻率。

[0065]

不特别地限定构成导电通路12的材料的25℃下的弹性率,但从减少电气检查时的压入负荷的观点考虑,该弹性率优选为50~150gpa。例如可以通过共振法(依据jis z2280)测定弹性率。

[0066]

不特别地限定构成导电通路12的材料,只要体积电阻率满足上述范围即可,可以是铜、金、铂、银、镍、锡、铁及其中一种材料的合金等金属材料。其中,从具有良好的导电性和柔软性并容易减少电气检查时的压入负荷的观点考虑,优选为从由金、银、铜及它们的合金构成的组中选择的一种以上的材料,其中,铜及其合金是更优选的。

[0067]

1-3.其他层

[0068]

本实施方式的各向异性导电片10还可以根据需要具有上述以外的其他层。其他层的例子包括:配置于导电通路12与绝缘层11之间的粘接层、作为绝缘层11的一部分的(与橡

胶组合物的交联物相比热膨胀系数低的)耐热性树脂层等。

[0069]

2.各向异性导电片的制造方法

[0070]

可以按照任意的方法制造本实施方式的各向异性导电片10。本实施方式的各向异性导电片10例如可以经过以下工序制造:1)准备多个单元的工序,该单元具有绝缘层、和周面的至少一部分的表面积率被调整为上述范围的多个导电线;2)将多个单元层叠并一体化来得到层叠体的工序;3)沿着层叠体的层叠方向,以与多个导电线的延伸方向交叉的方式进行切割,来得到各向异性导电片的工序。

[0071]

在1)的工序中,可以通过任意的方法来形成表面积率被调整后的多个导电线。例如,可以通过对表面积率被调整后的金属箔进行蚀刻来形成,也可以以使得表面积率成为上述范围的方式通过镀覆形成或转印。其中,从能够精度良好地调整表面积率的观点等考虑,优选对金属箔进行蚀刻来形成多个导电线。以下,说明利用对金属箔进行蚀刻来形成多个导电线的例子。

[0072]

图3a~图3f是表示本实施方式的各向异性导电片10的制造方法的一部分的工序的剖面示意图。图4a~图4c是表示本实施方式的各向异性导电片10的制造方法的剩余的工序的示意图。

[0073]

本实施方式的各向异性导电片10例如可以经过以下工序制造:i)准备具有金属箔21和绝缘层22的绝缘层-金属箔层叠体20的工序(参照图3a及图3b);ii)对绝缘层-金属箔层叠体20的金属箔21进行蚀刻,来得到多个导电线21’的工序(参照图3c~图3e);iii)用橡胶组合物将多个导电线21’密封,来得到单元24的工序(参照图3f);iv)将所得到的单元24层叠多个,来得到层叠体25的工序(参照图4a及图4b);v)将所得到的层叠体25沿层叠方向进行切割,来得到各向异性导电片10的工序(参照图4c)。

[0074]

i)的工序

[0075]

首先,准备具有表面积率被调整后的金属箔21和绝缘层22的绝缘层-金属箔层叠体20(参照图3a及图3b)。

[0076]

(金属箔21)

[0077]

金属箔21是导电通路12的原料,从减少电气检查时的压入负荷的观点考虑,优选是由从由金、银、铜及它们的合金构成的组中选择的一个以上的金属构成的金属箔,更优选是铜箔。

[0078]

另外,金属箔21的至少一个面是表面积率满足上述范围的粗糙面。在本实施方式中,金属箔21的一个面是粗糙面m,另一个面是光泽面(非粗糙面)s(参照图3a)。

[0079]

不特别地限定金属箔21的厚度,但是例如可以为1~35μm。

[0080]

(绝缘层-金属箔层叠体20)

[0081]

接着准备绝缘层-金属箔层叠体20。

[0082]

可以通过任意的方法来得到绝缘层-金属箔层叠体20。例如,在将金属箔21与由上述的橡胶组合物构成的层层叠后,使该橡胶组合物交联来作为绝缘层22,从而可得到绝缘层-金属箔层叠体20。

[0083]

对于金属箔21与由上述的橡胶组合物构成的层的层叠,例如可以通过在金属箔21上涂敷橡胶组合物、或(将片状的橡胶组合物)层压而得到。

[0084]

可以通过加热来进行橡胶组合物的交联。

[0085]

ii)的工序

[0086]

接着,对绝缘层-金属箔层叠体20的金属箔21进行蚀刻,来形成多个导电线21’(参照图3c~图3e)。

[0087]

在本实施方式中,在绝缘层-金属箔层叠体20的金属箔21上,呈图案状地配置掩模23,将未被掩模23覆盖的金属箔21的部分通过蚀刻去除(参照图3c及图3d)。

[0088]

掩模23例如可以是以规定的图案形成的光刻胶图案。以光刻胶图案为掩模,对露出的金属箔21进行蚀刻,形成与光刻胶图案大致相似形状的导电线21’。

[0089]

不特别地限定蚀刻方法,例如可以通过化学蚀刻进行。化学蚀刻例如可以通过使配置有掩模23的金属箔21与蚀刻液接触(例如将蚀刻液喷雾)来进行。

[0090]

然后,在蚀刻后,去除掩模23,得到多个导电线21’(参照图3e)。例如可利用碱性溶液等将由光刻胶图案构成的掩模23剥离去除。

[0091]

在本实施方式中,配置为,在俯视时,多个导电线21’的延伸方向相对于切割预定线倾斜。

[0092]

另外,所得到的导电线21’中的第一侧面21’c是来源于金属箔21的粗糙面m且表面积率为1.04以上的粗糙面。第二侧面21’d是来源于金属箔21的光泽面s且表面积率低于1.04的平滑面。导电线21’的第三侧面21’e及第四侧面21’f是通过金属箔21的蚀刻形成的面,且是表面积率低于1.04的平滑面。

[0093]

iii)的工序

[0094]

接着,以将多个导电线埋入该橡胶组合物中的方式,填充橡胶组合物(参照图3f)。

[0095]

关于所使用的橡胶组合物,可以使用与在上述i)的工序中使用的橡胶组合物同样的橡胶组合物,可以是成分相同的组合物,也可以是成分不同的组合物。从容易使单元之间一体化的观点考虑,优选地,所使用的橡胶组合物是与在上述i)的工序中使用的橡胶组合物成分相同的橡胶组合物。

[0096]

接着,对所填充的橡胶组合物进行加热,来使其交联。由此,形成包含橡胶组合物的交联物的绝缘层22。由此,得到多个导电线21’被埋入绝缘层22中的单元24(参照图3f)。

[0097]

优选地,在使橡胶组合物中的交联反应进展的条件下进行橡胶组合物的加热。从这样的观点考虑,加热温度可以优选为80℃以上,更优选为120℃以上。加热时间因加热温度而异,但是,例如可以是1~150分钟。

[0098]

iv)的工序

[0099]

接着,将所得到的多个单元24层叠,并使其一体化,来得到层叠体25(参照图4a及图4b)。

[0100]

对于被层叠的单元24的表面,从提高单元24之间的粘接性的观点考虑,也可以预先施加o2等离子处理等表面处理。

[0101]

可以通过任意的方法进行多个单元24的一体化,例如可以通过热压接合等进行。例如,依次重复进行层叠和一体化,来得到块状的层叠体25(参照图4b)。

[0102]

v)的工序

[0103]

以相对于导电线21’的延伸方向(轴向)交叉的方式(优选以正交的方式),按规定的间隔(t),沿层叠方向切割所得到的层叠体25(图4b的虚线)。由此,可以得到具有规定的厚度(t)的各向异性导电片10(参照图4c)。

[0104]

所得到的各向异性导电片10的绝缘层11来源于绝缘层22,多个导电通路12来源于多个导电线21’。

[0105]

另外,导电通路12的第一侧面12c来源于导电线21’的第一侧面21’c,导电通路12的第二侧面12d来源于第二侧面21’d,导电通路12的第三侧面12e来源于导电线21’的第三侧面21’e,导电通路12的第四侧面12f来源于导电线21’的第四侧面21’f(参照图3e)。

[0106]

优选地,可将所得到的各向异性导电片10用于电气检查。

[0107]

3.电气检查装置及电气检查方法

[0108]

(电气检查装置)

[0109]

图5是表示本实施方式的电气检查装置100的一例的剖面图。

[0110]

电气检查装置100是使用图1的各向异性导电片10的装置,例如用于对检查对象130的端子131间(测定点间)的电气特性(导通等)进行检查。应予说明,在该图中,从说明电气检查方法的观点出发,还一并图示了检查对象130。

[0111]

如图5所示,电气检查装置100具有保持容器(插座)110、检查用基板120及各向异性导电片10。

[0112]

保持容器(插座)110是用于保持检查用基板120和各向异性导电片10等的容器。

[0113]

检查用基板120配置于保持容器110内,在与检查对象130相对的面上,具有与检查对象130的各测定点相对的多个电极121。

[0114]

各向异性导电片10在检查用基板120的配置有电极121的面上,以使该电极121与各向异性导电片10中的第二面11b侧的导电通路12接触的方式配置。

[0115]

不特别地限定检查对象130,但作为检查对象130,例如可举出hbm、pop等各种半导体装置(半导体封装)或电子部件、印刷基板等。在检查对象130是半导体封装的情况下,测定点可以是焊垫(端子)。另外,在检查对象130是印刷基板的情况下,测定点可以是设置于导电图案中的测定用焊盘或部件安装用的焊盘。

[0116]

(电气检查方法)

[0117]

对使用图5的电气检查装置100的电气检查方法进行说明。

[0118]

如图5所示,本实施方式的电气检查方法具有以下工序:以隔着各向异性导电片10的方式将具有电极121的检查用基板120和检查对象130层叠起来,使检查用基板120的电极121与检查对象130的端子131通过各向异性导电片10电连接。

[0119]

在进行上述工序时,从便于使检查用基板120的电极121与检查对象130的端子131通过各向异性导电片10充分导通的观点考虑,可以根据需要,通过按压检查对象130来进行加压,或者在加热气氛下使它们接触。

[0120]

(作用)

[0121]

在本实施方式的各向异性导电片10中,多个导电通路12的周面包含表面积率被调整为一定值以上的区域(第一侧面12c)。由此,多个导电通路12与绝缘层11之间的密合性提高,因此,即使在电气检查时重复进行加压和减压,也能够抑制各向异性导电片10的导电通路12从绝缘层11剥离。

[0122]

特别地,通过将导电通路12利用铜等柔软的金属材料构成,从而能够减少压入负荷,但是,容易产生因加压和减压的重复引起的导电通路12的剥离。本发明的各向异性导电片10即使是在这样的情况下,也能使导电通路12不易从绝缘层11剥离。由此,能够进行准确

的电气检查。

[0123]

(变形例)

[0124]

应予说明,在上述实施方式中,示出了在各向异性导电片10中,导电通路12的端部12a(或12b)不在第一面11a侧(或第二面11b侧)突出的例子,但是,不限定于此,其也可以在第一面11a侧(或第二面11b侧)突出。

[0125]

图6是其他实施方式的各向异性导电片10的局部放大剖面图。如图6所示,导电通路12的端部12a(或12b)也可以在第一面11a侧(或第二面11b侧)突出。不特别地限定导电通路12在第一面11a侧的突出高度h(或导电通路12在第二面11b侧的突出高度),但是,例如可以将突出高度设为,相对于绝缘层11的厚度(t)为5~20%左右。

[0126]

第一面11a侧的、导电通路12的端部12a的突出高度与在第二面11b侧的端部12b的突出高度可以相同,也可以不同。

[0127]

另外,在上述实施方式中,示出了在各向异性导电片10中,导电通路12的延伸方向(轴向)相对于绝缘层11的厚度方向倾斜的例子,但是,不限定于此,导电通路12的延伸方向也可以与绝缘层11的厚度方向大致平行。

[0128]

另外,在上述实施方式中,示出了将各向异性导电片10用于电气检查的例子,但是,不限定于此,其也可以用于两个电子部件间的电连接,例如,玻璃基板与柔性印刷基板之间的电连接、或基板与安装于基板的电子零件之间的电连接等。

[0129]

[实施例]

[0130]

下面,参照实施例对本发明进行说明。本发明的范围不被实施例限定地解释。

[0131]

1.样本的材料

[0132]

(1)绝缘层的材料

[0133]

(硅橡胶组合物的制备)

[0134]

将ke-2061-40(信越有机硅公司制)用甲苯稀释至浓度为80%,得到了加成交联型的硅橡胶组合物(以jis k6253硬度计类型a测定的硬度为40)。

[0135]

(2)金属箔(导电通路)的材料

[0136]

准备了以下的铜箔。

[0137]

[表1]

[0138][0139]

通过以下的方法测定了表面积率及rz。

[0140]

(表面积率、rz)

[0141]

关于所准备的金属箔的各个面,在测定区域:纵向250μm

×

横向250μm的条件下,利

用激光显微镜(奥林巴斯公司制ols5000)观察,测定了测定区域中的表面积及rz。另外,作为测定区域的面积,使用了激光显微镜的测定值。而且,将所得到的值代入下式(1),计算出了表面积率。

[0142]

式(1):表面积率=表面积/面积

[0143]

应予说明,表面积及面积的测定均分别进行了3次(n=3),针对每次测定分别计算表面积率,并将它们的平均值设为“表面积率”。

[0144]

2.样本的制作及评价

[0145]

《样本1~5的制备》

[0146]

在表2所示的铜箔上,将上述制备的硅橡胶组合物利用贝克涂抹器涂敷后,在惰性烘箱中,在100℃下加热10分钟后,在150℃下进一步加热120分钟,使其干燥及固化。由此,形成了包含硅橡胶组合物的加成交联物的、厚度20μm的绝缘层。由此,得到了将铜箔与绝缘层层叠后的样本。

[0147]

《评价》

[0148]

通过以下的方法对所得到的样本的绝缘层与铜箔之间的密合性进行了评价。

[0149]

(密合性)

[0150]

除了将方格数设为100方格,并将评价基准如后述那样设置以外,依据划格胶带剥离试验(jis k 5600-5-6:1999(iso 2409:1992))进行了密合性的评价。

[0151]

首先,在样本的铜箔表面利用切刀以2mm间隔使100方格(10

×

10)的围棋网格状的伤痕从铜箔表层深入到绝缘层(包含硅橡胶组合物的加成交联物的层)。接着,在围棋网格状的部分将粘合胶带(nichiban株式会社制、

“セロテープ

(cellotape)(注册商标)”)以按压负荷0.1mpa进行了贴附。之后,快速地将粘合胶带剥离,观察(铜箔侧的)最表层的剥离状态,按以下的评价基准进行了密合性的评价。

[0152]

○

:100方格中,低于10方格发生了剥离。

[0153]

△

:100方格中,10方格以上且低于50方格发生了剥离。

[0154]

×

:100方格中,50方格以上发生了剥离。

[0155]

如果是

△

以上,则判断为良好。

[0156]

将样本1~5的评价结果示于表2。

[0157]

[表2]

[0158][0159]

※

产品目录值

[0160]

如表2所示,可知,金属箔的、(与绝缘层的)粘接面的表面积率为1.04以上的样本1~3在胶带剥离试验中示出良好的密合性。

[0161]

相对于此,可知,金属箔的、(与绝缘层的)粘接面的表面积率低于1.04的样本4及5未得到充分的密合性。

[0162]

本技术主张基于在2020年5月29日提出的日本专利申请特愿2020-94359的优先权。该申请说明书及附图中记载的内容全部引用于本技术说明书及附图中。

[0163]

工业实用性

[0164]

根据本发明,可以提供即使重复弹性变形,导电通路的剥离也较少且能够保持良好的密合性的各向异性导电片。

[0165]

附图标记说明

[0166]

10 各向异性导电片

[0167]

11 绝缘层

[0168]

11a 第一面

[0169]

11b 第二面

[0170]

12 导电通路

[0171]

12a、12b 端部

[0172]

12c 第一侧面

[0173]

12d 第二侧面

[0174]

12e 第三侧面

[0175]

12f 第四侧面

[0176]

20 绝缘层-金属箔层叠体

[0177]

21 金属箔

[0178]

21

’ꢀ

导电线

[0179]

22 绝缘层

[0180]

23 掩模

[0181]

24 单元

[0182]

25 层叠体

[0183]

100 电气检查装置

[0184]

110 保持容器

[0185]

120 检查用基板

[0186]

121 电极

[0187]

130 检查对象

[0188]

131 (检查对象的)端子

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1