半导体装置和电子设备的制作方法

1.根据本公开的技术(本技术)涉及半导体装置和包括该半导体装置的电子设备。

背景技术:

2.作为拍摄图像的固态摄像装置,例如提供ccd(charge coupled device:电荷耦合器件)图像传感器和cmos(complementary metal oxide semiconductor:互补金属氧化物半导体)图像传感器。然而,不需要特别的资金投入就能够在现有的cmos工艺中制造的cmos图像传感器已经受到关注,并且已迅速被应用于内置在手机中的相机系统或监控系统中。

3.随着cmos图像传感器在各种领域的应用,对小型化和高性能提出了更高的要求。因此,为了满足这些要求,提出了层叠式cmos图像传感器,在该层叠式cmos图像传感器中,传感器单元和外围电路单元分别形成在不同的基板(晶片)上,并且使用wow技术将这些晶片接合,使其具有作为图像传感器的功能(专利文献1)。

4.在层叠式cmos图像传感器中,入射光由传感器单元接收,并且由传感器单元中的光电二极管进行光电转换。由光电二极管产生的电荷由外围电路单元模数转换为像素信号。在此,在外围电路单元中,使用了用于截断输入信号的直流分量的耦合电容器。

5.所使用的电容元件的电容密度(每单位面积的电容值)越大,耦合电容器就越能够小型化,但要求电容值的偏置依赖性小。这是因为,如果电容值的偏置依赖性大,则例如传输到比较器的差分输入晶体管的栅电极的像素信号和参考信号失真,模数转换的精度显著劣化。

6.此外,用于制造外围电路单元的cmos工艺已经向精细工艺转移。然而,即使向精细工艺转移,处理数字信号并且包括诸如sram或逻辑电路等mosfet的逻辑电路也能够小型化,但是处理从传感器单元输出的模拟信号的模拟电路的小型化并不容易。其原因在于,虽然能够由传感器单元读取的最大电荷越大,图像传感器的性能就越好,但是由于检测到的电荷被转换为电压并且通过电路传输,因此,即使制造工艺按比例缩小,只要保持最大电荷时的性能,包括接收传感器单元的信号的模拟电路在内的器件的工作电压也不会降低,并且器件本身也无法按照缩放规则进行小型化。

7.注意,作为在半导体基板上形成的电容元件,提出了使用专利文献2中公开的mos型电容元件、专利文献3中公开的梳状配线电容元件和专利文献4中公开的mim(metal insulator metal:金属-绝缘体-金属)电容元件。

8.mos型电容元件的电容密度和mim电容元件的电容密度基本上由栅极绝缘膜的膜厚(d)和栅极绝缘膜的介电常数(ε)决定(ε/d)。作为增大电容密度的方法,由于增大介电常数会增加制造成本,因此通常使用减小膜厚的方法。然而,如果在不降低电容元件的工作电压的情况下减小绝缘膜的膜厚,则作为绝缘膜寿命的tddb(time dependent dielectric breakdown:时间相关介质击穿)会劣化,产品寿命缩短。

9.另外,梳状配线电容元件是利用相对配线形成的寄生电容作为电容元件的元件,但是为了增大电容密度,需要缩小配线的空间。然而,如果不降低电容元件的工作电压而缩

小配线空间,则配线空间之间的绝缘膜的tddb就会劣化,产品寿命就会缩短。此外,随着工艺的精细化,使用介电常数更小的低k膜作为覆盖配线层的绝缘膜,这也成为梳状配线电容元件的电容值不增加的原因。

10.另外,对于专利文献4中公开的mim电容元件,与上述mos型电容元件类似,绝缘膜的可靠性成为问题,并且无法提高电容密度。

11.引用文献列表

12.专利文献

13.专利文献1:日本专利申请公开号2018-148528

14.专利文献2:日本专利申请公开号2011-254088

15.专利文献3:日本专利申请公开号2005-183739

16.专利文献4:日本专利申请公开号2018-37626

技术实现要素:

17.本发明要解决的技术问题

18.如上所述,强烈需要在不降低电容元件的工作电压的情况下显著增加电容元件的电容密度的技术。

19.本公开是鉴于这种情况而作出的,并且本公开的目的是提供一种能够在不降低工作电压的情况下提高电容元件的电容密度的半导体装置和电子设备。

20.问题的解决方案

21.根据本公开的一个方面,提供了一种半导体装置,其包括:第一半导体基板,其包括第一电容元件部,所述第一电容元件部包括至少一个电容元件;第二半导体基板,其与所述第一半导体基板层叠;以及第二电容元件部,其由设置在所述第一半导体基板和所述第二半导体基板之间的接合面上的金属接合部形成,其中,所述第一电容元件部和所述第二电容元件部彼此并联连接。

22.根据本公开的另一方面,提供了一种电子设备,其包括半导体装置,所述半导体装置包括:第一半导体基板,其包括第一电容元件部,所述第一电容元件部包括至少一个电容元件;第二半导体基板,其与所述第一半导体基板层叠;以及第二电容元件部,其由设置在所述第一半导体基板和所述第二半导体基板之间的接合面上的金属接合部形成,其中,所述第一电容元件部和所述第二电容元件部彼此并联连接。

附图说明

23.图1是根据第一实施例的固态摄像装置的等效电路图。

24.图2是根据第一实施例的像素阵列单元的等效电路图。

25.图3是根据第一实施例的像素的等效电路图。

26.图4是根据第一实施例的比较器的等效电路图。

27.图5是根据第一实施例的上侧半导体基板和下侧半导体基板的示意图。

28.图6是根据第一实施例的固态摄像装置的剖视图。

29.图7是示出根据第一实施例的n+累积型mos电容元件的构造的平面图。

30.图8是示出根据第一实施例的mom电容元件的构造的平面图。

31.图9是示出根据第一实施例的mim电容元件的构造的平面图。

32.图10是根据第一实施例的变形例的固态摄像装置的剖视图。

33.图11是示出根据第一实施例的变形例的pip电容元件的构造的平面图。

34.图12是根据第二实施例的固态摄像装置的剖视图。

35.图13是示出根据第二实施例的第一变形例的接合部电容元件的布置示例的平面图。

36.图14是示出根据第二实施例的第一变形例的接合部电容元件的另一布置示例的平面图。

37.图15是示出根据第二实施例的第一变形例的接合部电容元件的又一布置示例的平面图。

38.图16是根据第二实施例的第二变形例的固态摄像装置的剖视图。

39.图17是示出根据第二实施例的第二变形例的接合部电容元件的布置示例的图。

40.图18是示出根据第二实施例的第二变形例的根据接合部电容元件的移位而发生的电容值的变化的图。

41.图19是示出根据第二实施例的第二变形例的接合部电容元件的另一布置示例的图。

42.图20是示出在第二实施例中布置在每个芯片中的电容元件的类型以及当电容元件并联连接时电容值的增加率的示例的表。

43.图21是根据第二实施例的第三变形例的固态摄像装置的剖视图。

44.图22是根据第二实施例的第四变形例的固态摄像装置的剖视图。

45.图23是根据第二实施例的第五变形例的固态摄像装置的剖视图。

46.图24是根据第三实施例的固态摄像装置的剖视图。

47.图25是根据第四实施例的固态摄像装置的剖视图。

48.图26是示出根据第四实施例的传感器单元、像素晶体管单元和外围电路单元的示意图。

49.图27是示出根据第四实施例的传感器单元、像素晶体管单元和外围电路单元的等效电路图。

50.图28是构成根据第五实施例的固态摄像装置的半导体芯片上的各电路的布置图。

51.图29是根据第五实施例的固态摄像装置的剖视图。

52.图30是根据第六实施例的滤波电路的等效电路图。

53.图31是根据第六实施例的平滑电路的等效电路图。

54.图32是根据第六实施例的积分电路的等效电路图。

55.图33是根据第六实施例的电容dac的等效电路图。

56.图34是根据第七实施例的电子设备的示意性构造图。

具体实施方式

57.在下文中,将参考附图来说明本公开的实施例。在以下说明中,相同或相似的构件由相同或相似的附图标记表示,并且将省略重复的说明。然而,应当注意的是,附图是示意性的,并且厚度与平面尺寸的关系、各装置和各构件的厚度比例等与实际情况不同。因此,

具体的厚度和具体的尺寸应参考以下说明来确定。此外,各附图当然也包括具有不同尺寸关系和比例的部分。

58.在本说明书中,“第一导电型”是指p型和n型中的一种,并且“第二导电型”是指p型和n型中的与“第一导电型”不同的一种。此外,附加到“n”或“p”的“+”或

“‑”

是指与未附加“+”或

“‑”

的半导体区域相比具有相对更高的杂质浓度或相对更低的杂质浓度的半导体区域。然而,即使将相同的“n”添加到半导体区域,也不意味着各个半导体区域的杂质浓度完全相同。

59.此外,在以下说明中,诸如上和下等方向的定义仅是为了便于说明的定义,并不限制本公开的技术思想。例如,不用说,如果将对象旋转90

°

进行观察,则上侧和下侧被转换为左侧和右侧进行阅读,如果将对象旋转180

°

进行观察,则上侧和下侧被颠倒进行阅读。

60.注意,在本说明书中描述的效果仅仅是示例而不是限制,并且可以提供其他效果。

61.《第一实施例》

62.《固态摄像装置的总体构造》

63.作为第一实施例,将以根据本技术的半导体装置应用于固态摄像装置(cmos图像传感器)的情况为例进行说明。如图1所示,根据第一实施例的固态摄像装置100包括像素阵列单元110和用于读取来自像素阵列单元110的电信号并执行预定的信号处理的外围电路。

64.根据第一实施例的固态摄像装置100包括作为外围电路的用于控制行地址和行扫描的行选择电路120、用于控制列地址和列扫描的水平传输扫描电路130、以及作为控制电路的用于生成内部时钟的时序控制电路140。此外,根据第一实施例的固态摄像装置100包括作为外围电路的adc组150、作为斜坡信号发生器的dac(digital-to-analog conversion device:数模转换装置)160、放大器电路170、信号处理电路180和水平传输线190。此外,根据第一实施例的固态摄像装置100包括作为外围电路的dc电源电路(未示出)。

65.如图2所示,像素阵列单元110包括以阵列(矩阵)方式排列的多个像素30。例如,如图3所示,每个像素30包括光电转换元件d1,该光电转换元件d1例如包括光电二极管(pd)。像素30包括传输晶体管t1、复位晶体管t2、放大晶体管t3和选择晶体管t4这四个晶体管作为光电转换元件d1的有源元件。此外,为了提取来自像素30的信号作为电压变化,恒流源负载z1连接到像素30在列方向上共享的垂直信号线(lsgn)。

66.光电转换元件d1将入射光光电转换为与入射光的量对应的电荷(在这种情况下为电子)。作为传输元件的传输晶体管t1连接在光电转换元件d1和作为输入节点的浮动扩散部fd之间,并且作为控制信号的传输信号trg通过传输控制线ltrg被提供给传输晶体管t1的栅极(传输栅极)。因此,传输晶体管t1将由光电转换元件d1光电转换的电子传输到浮动扩散部fd。

67.复位晶体管t2连接在提供电源电压vdd的电源线lvdd和浮动扩散部fd之间,并且作为控制信号的复位信号rst通过复位控制线lrst被提供给复位晶体管t2的栅极。因此,作为复位元件的复位晶体管t2将浮动扩散部fd的电位复位到电源线lvdd的电位。

68.作为放大元件的放大晶体管t3的栅极连接到浮动扩散部fd。也就是说,浮动扩散部fd用作作为放大元件的放大晶体管t3的输入节点。放大晶体管t3和选择晶体管t4串联连接在提供电源电压vdd的电源线lvdd和信号线lsgn之间。如上所述,放大晶体管t3经由选择晶体管t4连接到信号线lsgn,并且与像素部外部的恒流源is构成源极跟随器。然后,作为与

地址信号对应的控制信号的选择信号sel通过选择控制线lsel被施加到选择晶体管t4的栅极,并且选择晶体管t4导通。当选择晶体管t4导通时,放大晶体管t3放大浮动扩散部fd的电位,并且将与浮动扩散部fd的电位对应的电压输出到信号线lsgn。通过信号线lsgn将从各像素输出的电压输出到adc组150。例如,由于传输晶体管t1、复位晶体管t2和选择晶体管t4的栅极以行为单位连接,因此对一行的各像素同时执行这些操作。

69.在像素阵列单元110中布线的复位控制线lrst、传输控制线ltrg和选择控制线lsel作为一组以像素阵列的各行为单位进行布线。设置有m条复位控制线lrst、m条传输控制线ltrg和m条选择控制线lsel。复位控制线lrst、传输控制线ltrg和选择控制线lsel由行选择电路120进行驱动。

70.同时,去耦电容器cv1连接在电源线lvdd和地(gnd)之间。去耦电容器cv1去除混入为了驱动电路而提供的直流电源电压中的噪声分量。去耦电容器cv1的总面积可以超过10mm2,并且去耦电容器cv1在层叠式cmos图像传感器的芯片面积中所占的比例大。

71.在图1所示的adc组150中,布置有多个包括比较器151、计数器152和锁存器153的单斜率型adc。例如,如图4所示,比较器151包括差分放大电路,该差分放大电路包括构成差分对的差分输入晶体管t21和t22以及由电流镜电路构成的有源负载晶体管t11和t12。差分输入晶体管t21和t22由n型mosfet(以下也被称为“nmos”)构成,并且有源负载晶体管t11和t12由p型mosfet(以下也被称为“pmos”)构成。在根据第一实施例的固态摄像装置的外围电路中,有源负载晶体管t11和t12以及差分输入晶体管t21和t22是噪声源。

72.采样电容器c1和c2分别串联连接到比较器151的两个差分输入端子。比较器151将参考电压(dac侧输入)vslop与模拟信号(垂直信号线(vsl:vertical signal line)侧输入)进行比较,所述参考电压vslop是通过阶梯状地改变由dac 160产生的参考电压而获得的斜坡波形,所述模拟信号是经由垂直信号线lsgn从各行线的像素获得的。

73.图1所示的计数器152对比较器151的比较次数进行计数。adc组150具有n位数字信号转换功能,针对每条垂直信号线(列线)布置有该adc组150,并且该adc组150构成列并行adc块。各锁存器153的输出例如连接到具有2n位宽度的水平传输线190。然后,布置与水平传输线190对应的2n个放大器电路170及信号处理电路180。

74.所使用的电容元件的电容密度(每单位面积的电容值)越大,图4所示的采样电容器c1和c2越能够小型化,但是要求电容值的偏置依赖性小。这是因为,如果电容值的偏置依赖性大,则例如传输到比较器的差分输入晶体管的栅电极的像素信号和参考信号失真,模数转换的精度显著劣化。此外,对于比较器151,去耦电容器cv2连接在电源线vdd和地(gnd)之间。

75.因此,在本公开的第一实施例中,即使固态摄像装置100小型化,也能够实现电容值的偏置依赖性小、不降低工作电压而电容密度大的电容元件。

76.图5是构成根据第一实施例的固态摄像装置100的半导体芯片上的各电路的布置图。根据第一实施例的固态摄像装置100包括层叠式图像传感器,在该层叠式图像传感器中,层叠有上侧半导体基板210和下侧半导体基板220这两个半导体芯片,并且上侧芯片和下侧芯片的配线的一部分通过诸如tsv(hrough-silicon via:硅通孔)等金属接合部mc1电连接。在这种情况下,像素30以矩阵方式排列的像素阵列单元110被安装在上侧半导体基板210上,并且除像素阵列单元110以外的诸如adc组150和信号处理电路180等外围电路被安

装在下侧半导体基板220上。

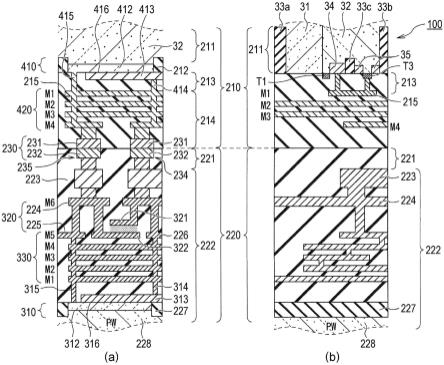

77.图6是根据第一实施例的固态摄像装置100的剖视图。图6(a)示出了像素的外部,图6(b)示出了像素的内部。

78.在图6中,上侧半导体基板210从上面开始包括光电转换层211、层间绝缘膜213和配线层214。光电转换层211是形成有光电二极管(pd)31的层,该光电转换层通过光电转换产生与入射光的量对应的电荷。对于各像素30,pd 31通过形成在光电转换层211中的元件分离部33a和33b电气分离。此外,在光电转换层211中未形成pd 31的区域中形成有p型阱32。在p型阱32中形成有fd 34和n型扩散层35。注意,如图6(a)所示,在像素30的外部仅设置有p型阱32。

79.由pd 31产生的电荷经由设置在层间绝缘膜213中的传输晶体管t1传输到fd 34。设置在层间绝缘膜213中的放大晶体管t3位于n型扩散层35附近。在n型扩散层35的两端形成有元件分离部33b和33c。因此,fd 34和像素晶体管t3通过n型扩散层35和元件分离部33b、33c电气分离。

80.配线层214包括通过层叠成多层而形成的配线(m1至m4)215。构成各像素30的传输晶体管t1、复位晶体管t2、放大晶体管t3和选择晶体管t4经由在配线层214中形成的多层配线(m1至m4)215进行驱动。此外,在配线层214中设置由铜(cu)制成的金属接合部231,以执行与下侧半导体基板220的接合。

81.另一方面,下侧半导体基板220从上面开始包括层间绝缘膜221和配线层222。配线层222包括所有的配线223和通过层叠成多层而形成的配线(m1至m6)224。此外,层间绝缘膜221设置有由铜(cu)制成的金属接合部232,用于与上侧半导体基板210的金属接合部231接合。

82.在具有上述构造的固态摄像装置100中,入射到上侧半导体基板210的光被pd 31光电转换,从而生成电荷。然后,所生成的电荷经由放大晶体管t3,通过由配线(m1至m4)215和下侧半导体基板220的配线(m1至m6)224形成的图1所示的信号线lsgn,作为像素信号输出到形成在下侧半导体基板220上的adc组150。

83.如图6(a)所示,在下侧半导体基板220上布置有n+累积型的mos电容元件310。在mos电容元件310中,如图7所示,如果更靠近安装的下侧半导体基板220侧的电极是下部电极312,则例如安装在元件分离部311上的下部电极312是形成在p型阱228中的n型扩散层,在下部电极312上形成有由氧化硅(sio2)制成的栅极绝缘膜316,并且在栅极绝缘膜316上形成有由n型多晶硅制成的上部电极313。由于在操作期间电子被累积在下部电极312的表面上,因此mos电容元件310被称为n+累积型mos电容器。

84.在形成有配线(m1至m6)224的区域中,该配线(m1至m6)224是布置有mos电容元件310的同一区域中的上层,安装有mim(metal insulator metal:金属绝缘体金属)电容元件320,该mim电容元件320是通过层叠位于靠近下侧半导体基板220侧的一侧的下部电极322、绝缘膜(包括high-k材料)和上部电极321而形成的。该绝缘膜由ta2o2、nb2o3、zro2、hfo2、la2o3、pr2o3、al2o3、sio2和sin中的任一种的单层膜或多个层叠膜形成。如图9所示,下部电极322和上部电极321分别由cu、al、ti、tin、ta、tan中的任一种的单层膜或多个层叠膜形成。

85.配线(m5)224设置有负(minus)端子225和正(plus)端子226。

86.此外,通过使用配线(m1至m4)224,在下侧半导体基板220上形成有图8所示的mom电容元件330。n+累积型mos电容元件310、mim电容元件320和mom电容元件330并联连接。在这种情况下,mom电容元件330的上部电极331经由通孔315和配线(m6)224连接到mos电容元件310的下部电极312和mim电容元件320的下部电极322。此外,mom电容元件330的下部电极332经由通孔314和配线(m6)224连接到mos电容元件310的上部电极313和mim电容元件320的上部电极321。在这种构造中,能够进一步增加电容密度。

87.上侧半导体基板210从上面开始包括p型阱32、层间绝缘膜213和配线层214。在上侧半导体基板210的下侧布置有n+累积型mos电容元件410。在mos电容元件410中,下部电极412是形成在p型阱32中的n型扩散层,在下部电极412上形成有由氧化硅(sio2)制成的栅极绝缘膜416,在栅极绝缘膜416上形成有由n型多晶硅制成的上部电极413。

88.在布置有mos电容元件410的同一区域中,在形成有配线(m1至m4)215的区域中,使用配线(m1至m4)215形成作为梳状配线电容元件的mom电容元件420。在这种情况下,mom电容元件420的上部电极经由通孔414连接到mos电容元件410的上部电极413。此外,mom电容元件420的下部电极经由通孔415连接到mos电容元件410的下部电极412。

89.此外,mos电容元件410的上部电极413和mom电容元件420的上部电极经由由铜(cu)制成的金属接合部231和232连接到下侧半导体基板220侧的mos电容元件310的上部电极313、下侧半导体基板220侧的mim电容元件320的上部电极321以及下侧半导体基板220侧的mom电容元件330的上部电极。此外,mos电容元件410的下部电极412和mom电容元件420的下部电极经由由铜(cu)制成的金属接合部231和232连接到下侧半导体基板220侧的mos电容元件310的下部电极312、下侧半导体基板220侧的mim电容元件320的下部电极322以及下侧半导体基板220侧的mom电容元件330的下部电极。

90.在图6中,在固态摄像装置100中,将布置在接合面上的上侧半导体基板210侧的金属接合部231和下侧半导体基板220侧的金属接合部232接合以形成电容元件,并且该电容元件与另一电容元件并联连接,从而进一步增加电容密度。该电容元件被称为接合部电容元件230。

91.接合部电容元件230的上部电极234经由通孔414连接到mos电容元件410的上部电极413和mom电容元件420的上部电极。此外,接合部电容元件230的下部电极235经由通孔415连接到mos电容元件410的下部电极412和mom电容元件420的下部电极。

92.另外,接合部电容元件230的上部电极234连接到下侧半导体基板220侧的mos电容元件310的上部电极313、下侧半导体基板220侧的mim电容元件320的上部电极321以及下侧半导体基板220侧的mom电容元件330的上部电极。此外,接合部电容元件230的下部电极235连接到下侧半导体基板220侧的mos电容元件310的下部电极312、下侧半导体基板220侧的mim电容元件320的下部电极322以及下侧半导体基板220侧的mom电容元件330的下部电极。

93.《第一实施例的操作效果》

94.如上所述,根据第一实施例,接合部电容元件230由上侧半导体基板210和下侧半导体基板220之间的金属接合部231和232形成,并且接合部电容元件230与包括在上侧半导体基板210中的mos电容元件410和mom电容元件420以及包括在下侧半导体基板220中的mos电容元件310、mim电容元件320和mom电容元件330并联连接,从而能够增加整个电容元件的电容值。因此,能够在不降低工作电压的情况下提高电容元件的电容密度。

95.《第一实施例的变形例》

96.图10是根据第一实施例的变形例的固态摄像装置100的剖视图。在图10中,与图6(a)中的部件相同的部件由相同的附图标记表示,并且省略其详细说明。

97.在图10中,固态摄像装置100是使用pip(poly insulator poly:多晶硅-绝缘体-多晶硅)电容元件340的示例。如图11所示,pip电容元件340是使用多晶硅作为电极的电容元件,并且例如是通过顺序地层叠作为下部电极342的n型多晶硅、作为绝缘膜的sio2以及作为上部电极的n型多晶硅而形成的电容元件。其特征在于,电容值的偏置依赖性小。

98.pip电容元件340的上部电极343经由通孔314和配线(m6)224连接到mim电容元件320的上部电极321。此外,pip电容元件340的下部电极342经由通孔315和配线(m6)224连接到mim电容元件320的下部电极322。

99.因此,即使在第一实施例的变形例中,也能够获得与第一实施例的操作效果相同的操作效果。

100.《第二实施例》

101.图12是根据第二实施例的固态摄像装置100的剖视图。在图12中,与图6(a)中的部件相同的部件由相同的附图标记表示,并且省略其详细说明。

102.在图12中,在固态摄像装置100中,将布置在接合面上的上侧半导体基板210侧的金属接合部511和下侧半导体基板220侧的金属接合部512接合以形成接合部电容元件510。

103.在第二实施例中,通过使接合部电容元件510的上部电极514和接合部电容元件510的下部电极515相互接近至工艺的加工精度可允许的距离,从而增大横向的电容分量,并且能够进一步增加固态摄像装置100的电容元件的电容值。

104.《第二实施例的操作效果》

105.如上所述,根据第二实施例,在接合部电容元件510中,通过使用与上侧半导体基板210和下侧半导体基板220的层叠方向(图12中的z方向)正交的方向(图12中的y方向)、即横向的电容分量,能够进一步增大电容值。

106.《第二实施例的第一变形例》

107.图13是示出根据本技术的第二实施例的第一变形例的接合部电容元件510的布置示例的平面图。如图13所示,连接到金属接合部的通孔516以可伸缩的方式彼此相对,还利用通孔516的横向电容分量,从而能够进一步增大电容值。

108.注意,即使在图14和图15所示的接合部电容元件510的布置示例中,也能够进一步增大电容值。

109.《第二实施例的第二变形例》

110.图16是根据本技术的第二实施例的第二变形例的固态摄像装置100的剖视图。在图16中,与图12中的部件相同的部件由相同的附图标记表示,并且省略其详细说明。

111.在图16中,在固态摄像装置100中,将布置在接合面上的上侧半导体基板210侧的第一金属膜521、523与下侧半导体基板220侧的第二金属膜522、524接合以形成接合部电容元件520。

112.接合部电容元件520的问题在于,如果在上侧半导体基板210(传感器单元)和下侧半导体基板220(外围电路单元)接合时发生的接合对准偏差大,则电容值变化增大,但是通过采用图17所示的布局,能够减小由接合不对准引起的电容值变化。具体布局包括环形的

第一电极525和位于第一电极525中心的第二电极526。构成第一电极525的第一金属膜521的内径大于构成第一电极525的第二金属膜522的内径。构成第二电极526的第一金属膜523的外径大于构成第二电极526的第二金属膜524的外径。在图17中,接合部电容元件520的第一电极525和接合部电容元件520的第二电极526具有正方形布局,但是也可以具有圆形形状。

113.通过采用这种布局,如图18所示,例如,在上侧半导体基板210(传感器单元)相对于下侧半导体基板220(外围电路单元)向左侧偏移的情况下,接合部电容元件520的左侧面的电容值增大,但是右侧面的电容值减小。因此,能够减小整个接合部的电容值变化。

114.此外,在上侧半导体基板210(传感器单元)相对于下侧半导体基板220(外围电路单元)向右偏移的情况下,发生上述相反的电容值的增减。然而,在这种情况下,整个接合部的电容值的变化也小,结果,即使接合部的对准偏差大,也能提供接合部电容值的变化不增大的元件结构。

115.此外,即使在图19所示的布局中,也能够减少由于接合不对准引起的电容值变化。在这种情况下,构成第一电极525的第一金属膜521的内径小于构成第一电极525的第二金属膜522的内径。构成第二电极526的第一金属膜523的外径小于构成第二电极526的第二金属膜524的外径。

116.图20示出了布置在各芯片中的电容元件的类型以及当这些电容元件并联连接时的电容值的倍增因子的示例。如果以布置在下侧半导体基板220(外围电路单元)上的mom电容元件330单独时的电容值为基准,则当所有所述电容元件并联连接时,电容值增加10倍。应注意,当布置在下侧半导体基板220(外围电路单元)上的累积型mos电容元件310和mim电容元件320并联连接时,电容值增加5.1倍。此外,当布置在下侧半导体基板220(外围电路单元)上的累积型mos电容元件310、mim电容元件320和mom电容元件330并联连接时,电容值增加6.1倍。

117.《根据第二实施例的第二变形例的操作效果》

118.根据第二实施例的第二变形例,由于上侧半导体基板210相对于下侧半导体基板220向左侧或右侧偏移,因此即使接合部的对准偏差大,接合部电容元件520的电容值变化也不会增大。

119.《第二实施例的第三变形例》

120.图21是根据本技术的第二实施例的第三变形例的固态摄像装置100的剖视图。在图21中,与图12中的部件相同的部件由相同的附图标记表示,并且省略其详细说明。

121.图21的示例是如下电容元件的示例:在下侧半导体基板220(外围电路单元)的同一区域上布置累积型mos电容元件310和mim电容元件320,在接合部布置接合部电容元件510,在上侧半导体基板210(传感器单元)中布置累积型mos电容元件410,并且累积型mos电容元件310、mim电容元件320、接合部电容元件510和累积型mos电容元件410全部并联连接。

122.即使在第三变形例中,也能够获得与第二实施例的操作效果相同的操作效果。

123.《第二实施例的第四变形例》

124.图22是根据本技术的第二实施例的第四变形例的固态摄像装置100的剖视图。在图22中,与图12中的部件相同的部件由相同的附图标记表示,并且省略其详细说明。

125.图22的示例是如下电容元件的示例:在下侧半导体基板220(外围电路单元)的同

一区域上布置累积型mos电容元件310和mom电容元件330,在接合部布置接合部电容元件510,在上侧半导体基板210(传感器单元)中布置累积型mos电容元件410和mom电容元件420,并且累积型mos电容元件310、mom电容元件330、接合部电容元件510、累积型mos电容元件410和mom电容元件420全部并联连接。

126.即使在第四变形例中,也能够获得与第二实施例的操作效果相同的操作效果。

127.《第二实施例的第五变形例》

128.图23是根据本技术的第二实施例的第五变形例的固态摄像装置100的剖视图。在图23中,与图12中的部件相同的部件由相同的附图标记表示,并且省略其详细说明。

129.图23的示例是如下电容元件的示例:在下侧半导体基板220(外围电路单元)的同一区域上布置累积型mos电容元件310和mom电容元件330,在接合部布置接合部电容元件510,在上侧半导体基板210(传感器单元)中不布置任何电容元件,并且累积型mos电容元件310、mom电容元件330和接合部电容元件510并联连接。

130.即使在第五变形例中,也能够获得与第二实施例的操作效果相同的操作效果。

131.《第二实施例的另一变形例》

132.第二实施例不限于此。例如,在通过一般的cmos工艺制造上侧半导体基板210(传感器单元)和下侧半导体基板220(外围电路单元)的情况下,存在多个能够安装在上侧半导体基板210和下侧半导体基板220各者上的电容元件。本领域技术人员能够容易地想到,在添加图12所示的接合部电容元件510的情况下,存在许多能够并联连接的电容元件的组合。设计者只需要根据整个电路的布局和所要求的电容值来选择并联连接的电容元件,使其达到最优即可。

133.《第三实施例》

134.图24是根据第三实施例的固态摄像装置100a的剖视图。在图24中,与图6(b)中的部件相同的部件由相同的附图标记表示,并且省略其详细说明。

135.在图24中,在固态摄像装置100a中,将布置在接合面上的上侧半导体基板210侧的第一金属膜531、533和下侧半导体基板220侧的第二金属膜532、534接合以形成接合部电容元件530。

136.接合部电容元件530包括环形的第一电极535和位于第一电极535的中心的第二电极536。构成第一电极535的第一金属膜531的内径小于构成第一电极535的第二金属膜532的内径。构成第二电极536的第一金属膜533的外径小于构成第二电极536的第二金属膜534的外径。在图24中,接合部电容元件530的第一电极535和接合部电容元件530的第二电极536具有正方形布局,但是也可以具有圆形形状。

137.固态摄像装置100a通过在像素中设置累积从光电二极管31溢出的电荷的电容元件,来扩展摄像元件的动态范围。本发明优选应用于具有像素内电容元件的层叠式图像传感器。将针对各像素布置的两个第一金属膜531、533与两个第二金属膜532、534接合以形成接合部电容元件530。在接合部电容元件530中,即使发生接合面的不对准,电极之间的电容值变化也会减小,并且能够减小像素的动态范围的变化。此外,在现有技术中,为了在传感器单元中形成像素内电容器,需要为此的制造工序。然而,在第三实施例中,由于像素内电容器是使用连接上侧半导体基板210(传感器单元)和下侧半导体基板220(外围电路单元)的第一金属膜531、533以及第二金属膜532、534形成的,因此能够在不增加制造工序的情况

下以低成本扩大动态范围。

138.《第四实施例》

139.本公开的第四实施例将说明如下的固态摄像装置:将光电转换元件和放大来自光电转换元件的信号的放大晶体管布置在不同的基板上,并且通过wow技术层叠三个基板,在所述三个基板上安装有传感器单元、像素晶体管单元和外围电路单元,在所述传感器单元中,设置有光电转换元件和传输栅极(trg),在所述像素晶体管单元中,设置有诸如放大晶体管等像素晶体管,在所述外围电路单元中,设置有处理来自放大晶体管的信号的信号处理电路。

140.图25是根据第四实施例的固态摄像装置100b的剖视图。图25(a)示出了像素的外部,图25(b)示出了像素的内部。在图25中,与图6中的部件相同的部件由相同的附图标记表示,并且省略其详细说明。

141.固态摄像装置100b从上面开始包括传感器单元610、像素晶体管单元620和外围电路单元630。如图26所示,固态摄像装置100b包括层叠式图像传感器,在该层叠式图像传感器中,层叠有传感器单元610、像素晶体管单元620和外围电路单元630这三个半导体芯片,并且配线的一部分通过金属接合部640电气连接。如图27所示,在传感器单元610中布置有传输晶体管t1、光电二极管31和浮动扩散部fd 34。在像素晶体管单元620中布置有复位晶体管t2、放大晶体管t3、选择晶体管t4。

142.返回参考图25,传感器单元610从上面开始包括光电转换层611和层间绝缘膜612。光电转换层211是形成有pd(photodiode:光电二极管)31的层,该光电转换层通过光电转换产生与入射光的量对应的电荷。针对各像素30,pd 31通过形成在光电转换层611中的元件分离部33a、33b电气分离。此外,fd 34和传输晶体管t1的栅电极36形成在光电转换层611中。应注意,如图25(a)所示,在像素30的外部仅布置p型阱32。传输晶体管t1形成在层间绝缘膜612中。

143.像素晶体管单元620从上面开始包括p型阱621和配线层622。在p型阱621中形成n型扩散层。配线层622包括通过层叠成多层而形成的配线(m1至m4)623。构成各像素30的传输晶体管t1、复位晶体管t2、放大晶体管t3和选择晶体管t4经由形成在配线层622中的多层配线(m1至m4)623进行驱动。此外,在配线层622中布置由铜(cu)制成的金属接合部641,用于执行与外围电路单元630的接合。

144.另一方面,外围电路单元630从上面开始包括层间绝缘膜和配线层。配线层包括所有配线631和通过层叠成多层而形成的配线(m1至m6)632。此外,层间绝缘膜设置有由铜(cu)制成的金属接合部642,用于与像素晶体管单元620的金属接合部641接合。

145.在具有上述构造的固态摄像装置100b中,入射在传感器单元610上的光被pd 31光电转换,从而产生电荷。然后,所产生的电荷经由放大晶体管t3,通过由配线(m1至m4)623和外围电路单元630的配线(m1至m6)632形成的图1所示的信号线lsgn,作为像素信号输出到在外围电路单元630上形成的adc组150。

146.如图25(a)所示,在外围电路单元630上布置有n+累积型mos电容元件310。在mos电容元件310的上层中布置有mom电容元件330和mim电容元件320。

147.在像素晶体管单元620的下侧布置有n+累积型mos电容元件410。在形成有配线(m1至m4)623的区域中,使用配线(m1至m4)623形成mom电容元件420,所述配线(m1至m4)623是

在布置有mos电容元件420的同一区域中的与像素晶体管单元620侧相反侧的层。在这种情况下,如图26所示,mom电容元件420的上部电极421经由通孔414连接到mos电容元件410的上部电极413。此外,mom电容元件420的下部电极422经由通孔415连接到mos电容元件410的下部电极412。

148.此外,mos电容元件410的上部电极413和mom电容元件420的上部电极421经由由铜(cu)制成的金属接合部641、642连接到外围电路单元630侧的mos电容元件310的上部电极313、外围电路单元630侧的mim电容元件320的下部电极322以及外围电路单元630侧的mom电容元件330的上部电极331。此外,mos电容元件410的下部电极412和mom电容元件420的下部电极422经由由铜(cu)制成的金属接合部641、642连接到外围电路单元630侧的mos电容元件310的下部电极312、外围电路单元630侧的mim电容元件320的上部电极321以及外围电路单元630侧的mom电容元件330的下部电极332。

149.《第四实施例的操作效果》

150.如上所述,根据第四实施例,能够获得与第一实施例的操作效果相同的操作效果。

151.《第五实施例》

152.本公开的第五实施例将说明应用于使用spad(single photon avalanche diode:单光子雪崩二极管)的光检测装置的固态摄像装置。

153.图28是构成根据第五实施例的固态摄像装置100c的半导体芯片上的各电路的布置图。根据第四实施例的固态摄像装置100c包括层叠式图像传感器,在该层叠式图像传感器中,层叠有上侧半导体基板710和下侧半导体基板720这两个半导体芯片,并且上下芯片的配线的一部分通过诸如tsv(through-silicon via:硅通孔)等金属接合部mc2电气连接。在这种情况下,spad光电二极管41以矩阵状排列在上侧半导体基板710中,并且spad光电二极管41以外的诸如adc组150或信号处理电路180等外围电路51安装在下侧半导体基板720上。

154.图29是根据第五实施例的固态摄像装置100c的剖视图。

155.在图29中,上侧半导体基板710从上面开始包括光电转换层711、层间绝缘膜713和配线层714。光电转换层711是形成有spad光电二极管41的层,该光电转换层711检测入射光(光子),并且通过使用雪崩倍增将由检测产生的载流子转换为电信号脉冲。针对各像素30,spad光电二极管41由形成在光电转换层711中的p型扩散层42a和n型扩散层42b电气分离。

156.从spad光电二极管41产生的电信号脉冲经由形成在层间绝缘膜713中的通孔716输出到形成在配线层714中的配线(m1至m4)715。将由铜(cu)制成的金属接合部731设置在配线层714中以执行与下侧半导体基板720的接合。

157.另一方面,下侧半导体基板720从上面开始包括层间绝缘膜721和配线层722。配线层722包括所有配线723和通过层叠成多层而形成的配线(m1至m6)724。此外,层间绝缘膜721设置有由铜(cu)制成的金属接合部732,用于与上侧半导体基板710的金属接合部731接合。

158.在具有上述构造的固态摄像装置100c中,在上侧半导体基板210中检测到的光被spad光电二极管41光电转换,从而产生电信号脉冲。然后,电信号脉冲经由由配线(m1至m4)715和下侧半导体基板720的配线(m1至m6)724形成的图1所示的信号线lsgn输出到外围电路51。

159.《第五实施例的操作效果》

160.如上所述,根据第五实施例,能够获得与第一实施例的操作效果相同的操作效果,并且构成了接合部电容元件730。据此,能够使接合部电容元件730用作临时累积来自上侧半导体基板710(传感器单元)的电信号的存储元件,并且能够提高spad的性能。

161.《第六实施例》

162.在第一至第五实施例中,已经以将根据本技术的半导体装置应用于作为电子设备的示例的固态摄像装置的情况为例进行了说明。在第六实施例中,以将根据本技术的半导体装置应用于其他电子设备的情况为例进行说明。

163.例如,根据本技术的半导体装置能够应用于构成一般滤波电路的电容器。如图30所示,一般滤波电路包括电阻器r11和电容器c11,并且能够将根据本技术的半导体装置用作电容器c11的构造。通过将根据本技术的半导体装置应用于构成滤波电路的电容器c11,能够实现大容量,并且能够进一步扩大通频带。

164.此外,根据本技术的半导体装置能够应用于构成一般平滑电路的电容器。如图31所示,一般的滤波电路包括二极管d21和电容器c21,并且能够将根据本技术的半导体装置用作电容器c21的构造。通过将根据本技术的半导体装置应用于构成滤波电路的电容器c21,能够实现大容量,并且能够将交流电精确地转换为直流电。

165.此外,根据本技术的半导体装置能够应用于构成一般积分电路的电容器。如图32所示,一般积分电路包括电阻器r32、电容器c31和运算放大器800,并且能够将根据本技术的半导体装置用作电容器c31的构造。

166.此外,根据本技术的半导体装置能够应用于图33所示的电容dac。电容dac包括多级电容器,并且能够将根据本技术的半导体装置用作具有多级电容器的构造。

167.《其他实施例》

168.如上所述,已经通过第一至第六实施例以及第一至第二实施例的变形例说明了本技术,但是不应理解为构成本公开的一部分的说明和附图限制本技术。如果理解上述第一至第六实施例中公开的技术内容,则本领域技术人员将清楚,本技术能够包括各种替代的实施例、示例和运用技术。此外,在第一至第六实施例以及第一和第二实施例的变形例中公开的构造能够在不发生矛盾的范围内适当地组合。例如,可以组合在多个不同实施例中公开的构造,或者可以组合在同一实施例的多个不同变形例中公开的构造。

169.《电子设备的应用示例》

170.接下来,将说明根据本公开的第七实施例的电子设备。图34是根据本公开的第七实施例的电子设备1000的示意性构造图。

171.根据第七实施例的电子设备1000包括固态摄像装置1010、光学透镜1020、快门装置1030、驱动电路1040和信号处理电路1050。对于根据第六实施例的电子设备1000,说明了电子设备(例如,相机)使用根据本公开的第一实施例的固态摄像装置100作为固态摄像装置1010时的实施例。

172.光学透镜1020在固态摄像装置1010的成像面上形成来自被摄体的图像光(入射光1060)的图像。因此,信号电荷在一定时段内累积在固态摄像装置1010中。快门装置1030控制固态摄像装置1010的光照时段和遮光时段。驱动电路1040提供用于控制固态摄像装置1010的传输操作和快门装置1030的快门操作的驱动信号。固态摄像装置1010的信号响应于

从驱动电路1040提供的驱动信号(时序信号)进行传输。信号处理电路1050对从固态摄像装置1010输出的信号(像素信号)进行各种类型的信号处理。经过信号处理的视频信号被存储在存储器等存储介质中,或者被输出到监视器。

173.在这种构造中,在根据第七实施例的电子设备1000中,在固态摄像装置1010中能够抑制光学混色,从而能够提高视频信号的图像质量。

174.应注意,能够应用固态摄像装置100、100a和100b的电子设备1000不限于相机,该电子设备1000也能够应用于其他电子设备。例如,可以将固态摄像装置应用于诸如用于移动电话等移动装置的相机模块等摄像装置。

175.此外,在第七实施例中,作为固态摄像装置1010,电子设备使用根据第一至第五实施例的固态摄像装置100、100a、100b和100c,但是也可以使用其他构造。

176.《固态摄像装置的使用示例》

177.上述固态摄像装置例如如下所述,能够用于感测诸如可见光、红外光、紫外光和x射线等光的各种情况。

178.用于拍摄供观看的图像的设备,例如,数码相机或具有相机功能的便携式设备。

179.用于交通控制的设备,例如,为了诸如自动停车等安全驾驶或驾驶员状态的识别等,用于拍摄汽车的前方、后方、周围、内部等的车载传感器;用于监视行驶车辆和道路的监视摄像机;以及用于测量车辆间的距离的测距传感器等。

180.用于诸如电视机、冰箱和空调等家用电器的设备,以便拍摄用户手势的图像并根据该手势执行设备操作。

181.用于医疗护理或健康护理的设备,例如,内窥镜或通过接收红外光执行血管造影的设备。

182.用于安全的设备,例如,用于预防犯罪的监控相机或用于人员身份验证的相机。

183.用于美容的设备,例如,用于对皮肤进行成像的皮肤测量仪器或用于对头皮进行成像的显微镜。

184.用于运动的设备,例如,运动用的运动相机或运动用的可穿戴式相机。

185.用于农业的设备,例如,用于监视田地和农作物状况的相机。

186.应注意,本说明书中描述的效果仅是示例且不受限制,并且可以提供其他效果。

187.应注意,本公开还能够具有以下构造。

188.(1)

189.一种半导体装置,其包括:

190.第一半导体基板,其包括第一电容元件部,所述第一电容元件部包括至少一个电容元件;

191.第二半导体基板,其与所述第一半导体基板层叠;和

192.第二电容元件部,其由设置在所述第一半导体基板和所述第二半导体基板之间的接合面上的金属接合部形成,

193.其中,所述第一电容元件部和所述第二电容元件部彼此并联连接。

194.(2)

195.根据(1)所述的半导体装置,其中,所述第二半导体基板包括第三电容元件部,所述第三电容元件部包括至少一个电容元件。

196.(3)

197.根据(2)所述的半导体装置,

198.其中,所述第一电容元件部和所述第三电容元件部分别并联连接多个电容元件,并且

199.所述多个电容元件包括mos电容元件、梳状配线电容元件、mim(金属绝缘体金属)电容元件和pip(多晶硅绝缘体多晶硅)电容元件中的两种或更多种。

200.(4)

201.根据(1)至(3)中任一项所述的半导体装置,其中,所述第二电容元件部包括第一金属接合部和第二金属接合部,所述第一金属接合部和所述第二金属接合部被形成为在与所述第一半导体基板和所述第二半导体基板的层叠方向正交的方向上彼此相对。

202.(5)

203.根据(4)所述的半导体装置,

204.其中,所述第一金属接合部是环形,并且所述第二金属接合部形成在所述环形的中心部分。

205.(6)

206.根据(5)所述的半导体装置,

207.其中,所述第一金属接合部和所述第二金属接合部包括设置在所述第一半导体基板的接合面上的第一金属膜和设置在所述第二半导体基板的接合面上的第二金属膜,

208.在所述第一金属接合部中,所述第一金属膜的内径小于所述第二金属膜的内径,并且

209.在所述第二金属接合部中,所述第一金属膜的直径小于所述第二金属膜的直径。

210.(7)

211.根据(4)至(6)中任一项所述的半导体装置,

212.其中,所述第一金属接合部和所述第二金属接合部具有正方形结构。

213.(8)

214.根据(1)至(7)中任一项所述的半导体装置,

215.其中,所述第一半导体基板包括像素和外围电路中的至少一者,所述外围电路对来自像素晶体管的信号进行处理,所述像素晶体管放大来自所述像素的信号,并且

216.所述第二半导体基板包括所述像素和所述外围电路中的另一者。

217.(9)

218.根据(8)所述的半导体装置,

219.其中,所述像素包括光电二极管,并且

220.包括所述像素晶体管的第三半导体基板进一步层叠在下述三个位置的至少一者上:所述第一半导体基板上、所述第二半导体基板上、所述第一半导体基板和所述第二半导体基板之间。

221.(10)

222.根据(1)至(7)中任一项所述的半导体装置,

223.其中,所述第一半导体基板包括传感器单元和外围电路中的至少一者,所述传感器单元包括spad(单光子雪崩二极管)光电二极管,所述外围电路对来自所述传感器单元的

信号进行处理,并且

224.所述第二半导体基板包括所述传感器单元和所述外围电路中的另一者。

225.(11)

226.根据(1)至(10)中任一项所述的半导体装置,

227.其中,所述第三电容元件部包括像素内电容器。

228.(12)

229.一种电子设备,其包括半导体装置,所述半导体装置包括:

230.第一半导体基板,其包括第一电容元件部,所述第一电容元件部包括至少一个电容元件;

231.第二半导体基板,其与所述第一半导体基板层叠;和

232.第二电容元件部,其由设置在所述第一半导体基板和所述第二半导体基板之间的接合面上的金属接合部形成,

233.其中,所述第一电容元件部和所述第二电容元件部彼此并联连接。

234.附图标记列表

235.30 像素

236.31 光电二极管

237.32、228、621 p型阱

238.33a、33b、33c、311 元件分离部

239.35、42b n型扩散层

240.36 栅电极

241.41 spad光电二极管

242.42a p型扩散层

243.51 外围电路

244.100、110a、100b、100c 固态摄像装置

245.110 像素阵列单元

246.120 行选择电路

247.130 水平传输扫描电路

248.140 时序控制电路

249.150 adc组

250.151 比较器

251.152 计数器

252.153 锁存器

253.170 放大器电路

254.180 信号处理电路

255.190 水平传输线

256.210、710 上侧半导体基板

257.211、711 光电转换层

258.213、221、713、721 层间绝缘膜

259.214、222、622、714、722 配线层

260.215、223、623、631、632、715、723、724 配线

261.220、720 下侧半导体基板

262.225、226 端子

263.230、510、520、530、730 接合部电容元件

264.231、232、511、512、640、641、642、731、732 金属接合部

265.234、313、321、331、343、413、421、514 上部电极

266.235、312、322、332、342、412、422、515 下部电极

267.310、410 累积型mos电容元件

268.314、315、414、415 通孔

269.316、416 栅极绝缘膜

270.320 mim电容元件

271.330 mom电容元件

272.340 pip电容元件

273.420 mom电容元件

274.521、523、531、533 第一金属膜

275.522、524、532、534 第二金属膜

276.525、535 第一电极

277.526、536 第二电极

278.610 传感器单元

279.611 光电转换层

280.612 层间绝缘膜

281.620 像素晶体管单元

282.630 外围电路单元

283.800 运算放大器

284.1000 电子设备

285.1010 固态摄像装置

286.1020 光学透镜

287.1030 快门装置

288.1040 驱动电路

289.1050 信号处理电路

290.1060 入射光

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1