一种基于芯片结构中Via与TSV导通的封装结构及方法与流程

一种基于芯片结构中via与tsv导通的封装结构及方法

技术领域

1.本发明属于芯片封装技术领域,更具体地说,涉及一种基于芯片结构中via与tsv导通的封装结构及方法。

背景技术:

2.随着集成电路芯片行业的迅速发展,现可以实现多器件有效集成在单一芯片上,从而也会导致芯片上的结构以及电路设计会非常复杂,相应的也会使芯片的尺寸变大,以及功耗的增加。况且单器件芯片已经不能满足现今的芯片市场需求,多器件集成芯片已渐渐出现在人们的视野,因此,如何解决多器件集成芯片所带来的尺寸大、功耗高、体积大等问题成为了研究热点。

3.如中国专利申请号cn201911367662.1,公开日为2020年5月8日,该专利公开了一种晶圆级封装芯片及方法。通过基底进行减薄处理,tsv孔里的金属和硅基底的背金连接在一起,可实现小尺寸超薄芯片的晶圆级封装,同时满足散热要求;缩减接地线路的封装电阻,降低电感效应,提升芯片性能,减少接地焊垫的连线数量,减少贵金属的使用,减小封装面积,有效降低成本;采用在图形化的增粘层上制作种子层和金属背金层,可避免发生鼓泡分层等结合力不足问题,提升可靠性,同时解决了散热问题。

4.又如中国专利申请号cn201410751394.4,公开日为2015年4月1日,该专利公开了一种高频ipd模块三维集成晶圆级封装结构及封装方法,包括pcb系统板,其特征是:在所述pcb系统板上堆叠低频ipd封装体,在低频ipd封装体上堆叠射频ipd封装体;所述pcb系统板通过焊球与低频ipd封装体的正面连接,低频ipd封装体通过焊球实现与外界的电学连接;所述低频ipd封装体通过第一金属焊垫和第二金属焊垫与射频ipd封装体连接。本发明将射频ipd模块功能进行分割,将ipd芯片分割为低频电路和射频电路两部分,并采用基于高电阻硅材料的晶圆级平面加工、tsv三维集成晶圆工艺,实现三维结构的射频ipd模块封装,减少射频ipd模块对于pcb系统板上信号线路的干扰。同时,占用pcb系统板的面积也相应减小,有利于实现器件和系统小型化。

5.上述专利虽然都能在一定程度上实现器件的小型化,但是程度有限,无法更进一步的实现在保证电气性能优异的情况下缩小集成芯片尺寸以及体积大小。

技术实现要素:

6.1、要解决的问题

7.针对现有集成芯片尺寸体积过大和性能差的问题,,本发明提供一种基于芯片结构中via与tsv导通的封装结构及方法。本发明的封装结构通过将tsv孔开设在了via孔上以达到垂直直线导通的目的,实现器件有序堆叠的同时缩短走线,无需额外的位置来做tsv通孔,减小集成芯片尺寸及体积的大小,且缩短走线能够降低功耗并且提高电气性能,结构简单。本发明的封装方法步骤简单,易于操作,效率高。

8.2、技术方案

9.为解决上述问题,本发明采用如下的技术方案。

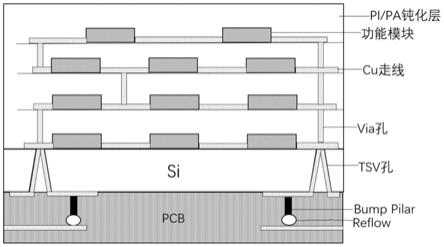

10.一种基于芯片结构中via与tsv导通的封装结构,包括硅衬底,硅衬底与pcb板连接,硅衬底的上方堆叠若干层功能层,若干层功能层之间通过via孔进行堆叠,功能层表面覆盖有钝化层,硅衬底的背面中在与底层功能层中via孔对应的地方刻蚀形成tsv孔,via孔与tsv孔内布设导电材料。

11.更进一步的,硅衬底的背面中刻蚀mark标记,mark标记对应底层功能层中via孔,tsv孔的位置对应mark标记的位置。

12.一种如上述任一项所述的基于芯片结构中via与tsv导通的封装结构的封装方法,包括如下步骤:

13.s1:依照via过孔工艺对硅衬底上方的若干层功能层进行堆叠叠层,实现各功能层之间电路的互联,并在每层功能层的表面覆盖钝化层;

14.s2:在硅衬底的背面采用刻蚀工艺形成tsv孔,tsv孔的位置为硅衬底的背面中与底层功能层中via孔对应的位置;

15.s3:形成tsv孔后进行铜键合,实现铜走线互连,再与pcb板进行焊接,完成封装。

16.更进一步的,所述步骤s1之前还包括s0:前期准备工作,其具体如下:

17.s01:制作硅片,并对硅片进行清洗得到硅衬底;

18.s02:在硅衬底的表面加工二氧化硅薄膜;

19.s03:在硅衬底的背面做若干个mark标记,mark标记与底层功能层中的via孔一一对应。

20.更进一步的,所述步骤s03中采用湿法腐蚀和干法等离子刻蚀的工艺进行mark标记。

21.更进一步的,所述步骤s2具体为:用胶膜包裹硅衬底正面,再以硅衬底背面的mark标记为基准,在mark标记处进行光刻刻蚀工艺形成tsv孔。

22.更进一步的,所述光刻刻蚀工艺包括rie刻蚀加上hf和氨水的混合溶液。

23.3、有益效果

24.相比于现有技术,本发明的有益效果为:

25.(1)本发明通过对硅衬底上tsv孔的位置做出改变,将tsv孔开设在了via孔上以达到垂直直线导通的目的,能够实现器件有序堆叠的同时缩短走线,无需另外预留额外的位置来做tsv通孔,从而减小集成芯片尺寸及体积的大小,同时缩短走线能够降低功耗并且提高电气性能,并且能够保证tsv通孔足够大,避免铜线走线出现孔洞的情况,继而避免器件发生短路,整体结构简单,成本低,使得芯片能够同时拥有更好的电路互连性能、低功耗、小尺寸和小体积等优势,适用性广;

26.(2)本发明通过在硅衬底背面刻蚀mark标记,mark标记用以锁定via孔的位置,进一步保证后续tsv孔刻蚀的准确性,保证tsv孔设置在via孔上达到垂直直线导通的目的,提高整个加工过程的精准性,保证各器件能够顺利连接,便于后续封装步骤的进行,使其最终具有良好的电气性能;

27.(3)本发明的封装方法步骤简单,易于操作,通过对硅衬底的背面进行光刻刻蚀形成tsv孔与via孔导通,即使得在硅衬底的背面将via孔裸露出来,再进行cu键合,实现cu走线互连,无需另外预留tsv孔,极大的减小了整体芯片的尺寸;并且缩短了走线,降低损耗,

提高封装效率的同时节省成本;

28.(4)本发明在进行堆叠叠层之前,对硅衬底进行预处理,二氧化硅薄膜的形成易保护硅衬底和减少刻蚀硅衬底所带来的应力影响;对硅衬底进行mark标记,采用湿法腐蚀和干法等离子刻蚀的工艺进行mark标记,保证其能够击穿整个硅衬底;tsv孔的形成工艺能够保证有效打通硅衬底,使得via孔中的铜能够完全显露出来方便后续的走线;使得最终封装完成的芯片能够有着优异的性能。

附图说明

29.图1为本发明的结构示意图;

具体实施方式

30.下面结合具体实施例和附图对本发明进一步进行描述。

31.实施例1

32.一种基于芯片结构中via与tsv导通的封装结构,包括硅衬底,硅衬底与pcb板连接,硅衬底的上方堆叠若干层功能层,若干个功能层与硅衬底形成一个整体,所述单个功能层即为由若干个功能模块(器件)组成,相邻两个功能模块之间进行铜走线。若干层功能层之间通过via孔进行堆叠,功能层表面覆盖有对功能层表面起到保护作用的钝化层,硅衬底的背面中在与底层功能层中via孔对应的地方刻蚀形成tsv孔,若干个功能层从硅衬底的上方依次向上堆叠,底层功能层即为靠近硅衬底的那一层功能层。本技术核心是将tsv孔开设在via孔上,实现tsv孔与via孔垂直导通,via孔与tsv孔内布设导电材料,在本实施例中将导电材料设置为铜线,即铜线在tsv孔与via孔中进行垂直直线导通。并且,为了保证tsv孔与via孔对应的精准性,更进一步的,在硅衬底的背面中刻蚀mark标记,mark标记对应底层功能层中via孔,tsv孔的位置对应mark标记的位置,mark标记对via孔起到定位锁定的作用,后续只需将tsv孔开设在mark标记处便可实现tsv孔与via孔垂直导通,保证精准度的同时提高工作效率。

33.本发明通过对硅衬底上tsv孔的位置做出改变,将tsv孔开设在了via孔上以达到垂直直线导通的目的,能够实现器件有序堆叠的同时缩短走线,无需另外预留额外的位置来做tsv通孔,从而减小集成芯片尺寸及体积的大小,同时缩短走线能够降低功耗并且提高电气性能,并且能够保证tsv通孔足够大,避免铜线走线出现孔洞的情况,继而避免器件发生短路,整体结构简单,成本低,使得芯片能够同时拥有更好的电路互连性能、低功耗、小尺寸和小体积等优势,适用性广。同时本技术中的该结构已经投入在生产实验中,通过tsv孔与via孔流程上下直线导通所制造出来的芯片电气性能更优。

34.一种如上述所述的基于芯片结构中via与tsv导通的封装结构的封装方法,包括如下步骤:

35.s0:前期准备工作,其具体如下:

36.s01:制作硅片,并对硅片进行plasma离子清洗得到硅衬底,减少硅衬底上的杂质,避免对后续封装带来不利影响;

37.s02:在硅衬底的表面加工二氧化硅薄膜,以保护硅衬底不受外界影响,且二氧化硅薄膜的设置能够减小在后续刻蚀工艺中对硅衬底的应力影响;

38.s03:在硅衬底的背面做若干个mark标记,mark标记与底层功能层中的via孔一一对应,此处应该说明的是,针对单个via孔可以采用一个或若干个mark标记,使其能够对via孔起到精准定位的作用,具体的可视不同情况而定;mark标记在硅衬底背面的形成工艺可采用湿法腐蚀hf和干法等离子刻蚀结合的工艺,该种工艺能够保证有足够的能力击穿整个硅衬底,保证mark标记对准via孔的精度,为后续tsv孔的形成提供精准的支撑;随后通过光刻、刻蚀、扩散、注入、电镀、薄膜等工艺完成芯片前端制作过程;并且出一版以背部mark标记为对位标记且能定位到via孔的mask,便于后续光刻机的工作;

39.s1:依照via过孔工艺对硅衬底上方的若干层功能层进行堆叠叠层,实现各功能层之间电路的互联,并在每层功能层的表面覆盖钝化层;

40.s2:在硅衬底的背面采用刻蚀工艺形成tsv孔,tsv孔的位置为硅衬底的背面中与底层功能层中via孔对应的位置;具体的,该步骤中用胶膜包裹硅衬底的正面,再以硅衬底背面的mark标记为基准,在mark标记处进行光刻刻蚀工艺形成tsv孔,硅衬底的正面即是指加装功能层的一面,背面即是正面的相对面;并且tsv孔的光刻刻蚀工艺包括rie刻蚀加上hf和氨水的混合溶液,可以有效的打通硅衬底,使得硅衬底上功能层的via孔中的导电材料铜线能够完全显露出来,便于后续完成走线;这里值得说明的是,现有的tsv孔工艺流程为当前端芯片制作完成后,对硅衬底的背面进行减薄抛光,再对硅衬底背面进行tsv打孔,tsv打孔开设在via孔的旁边,最终由dep cu种籽层以实现cu走线互连。现有的方式极大的增加了走线,并且要预留tsv孔的位置,使得最终尺寸和体积都较大;

41.s3:形成tsv孔后通过化学镀工艺形成外部的较厚铜走线,即进行铜键合,实现铜走线互连,并且对硅衬底做cmp,实现其表面平坦化,同时采用电镀形成bumppilar,再与pcb板进行焊接,完成封装。

42.本发明的封装方法步骤简单,易于操作,通过对硅衬底的背面进行光刻刻蚀形成tsv孔与via孔导通,即使得在硅衬底的背面将via孔裸露出来,再进行cu键合,实现cu走线互连,无需另外预留tsv孔,极大的减小了整体芯片的尺寸;并且缩短了走线,降低损耗,提高封装效率的同时节省成本,并且也能够保证tsv孔足够大,铜线不会出现空洞的情况。

43.本发明所述实例仅仅是对本发明的优选实施方式进行描述,并非对本发明构思和范围进行限定,在不脱离本发明设计思想的前提下,本领域工程技术人员对本发明的技术方案作出的各种变形和改进,均应落入本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1