半导体装置的制作方法

1.本发明实施例涉及一种半导体装置及其形成方法,尤其涉及一种多栅极装置及其形成方法。

背景技术:

2.半导体装置被用于各种电子应用中,例如个人电脑、手机、数字相机以及其他电子设备。一般通过在半导体基板上依序沉积绝缘或介电层、导电层以及半导体层材料以制造半导体装置,并使用光刻对各种材料层进行图案化,以在其上形成电路组件及元件。

3.半导体产业通过持续减小最小部件尺寸以持续提高各种电子组件(例如晶体管、二极管、电阻、电容等)的整合密度,其允许将更多组件整合至给定区域中。然而,随着最小部件尺寸的减小,出现了应解决的额外问题。

技术实现要素:

4.本发明一些实施例提供一种半导体装置,包括:第一通道区以及第二通道区,第一通道区以及第二通道区在基板上方;以及第一绝缘鳍片,在基板上,第一绝缘鳍片插入(interposed)在第一通道区与第二通道区之间,第一绝缘鳍片包括:下部,包括填充材料;以及上部,包括:第一介电层,在下部上,第一介电层为第一介电材料;第一盖层,在第一介电层上,第一盖层为第二介电材料,第二介电材料不同于第一介电材料;以及第二介电层,在第一盖层上,第二介电层为第一介电材料。

5.本发明另一些实施例提供一种半导体装置,包括:第一源极/漏极区,在第一半导体鳍片上;第二源极/漏极区,在第二半导体鳍片上;以及第一绝缘鳍片,在第一源极/漏极区以及第二源极/漏极区之间,第一绝缘鳍片包括:底部,底部包括衬层以及填充材料,填充材料插入在衬层的侧壁之间;以及顶部,在底部上,顶部包括:第一高介电常数介电层;第二高介电常数介电层,在第一高介电常数介电层的内侧壁之间;以及第一盖层,在第一高介电常数介电层以及第二高介电常数介电层之间。

6.本发明又一些实施例提供一种形成半导体装置的方法,包括:在第一半导体鳍片以及第二半导体鳍片之间形成衬层;在衬层上方形成填充材料;凹蚀衬层以及填充材料,以在衬层以及填充材料上方定义第一开口;在第一开口的侧壁上以及底表面上形成第一高介电常数介电层;在第一高介电常数介电层上形成第一盖层;以及在第一盖层上形成第二高介电常数介电层。

附图说明

7.以下将配合所附图示详述本公开的各面向。应注意的是,依据在业界的标准做法,各种特征并未按照比例绘制且仅用以说明例示。事实上,可能任意地放大或缩小单元的尺寸,以清楚地表现出本公开的特征。

8.根据本公开的一些实施例,图1以三维视图示出纳米结构场效晶体管

(nanostructure field-effect transistors,nano-fets)的示例。

9.根据本公开的一些实施例,图2至图4、图5a至图5c、图6a至图6c、图7a至图7c、图8a至图8f、图9a至图9b、图10a至图10b、图11a至图11b、图12a至图12b、图13a至图13f、图14a至图14e、图15a至图15c、图16a至图16c、图17a至图17c、图18a至图18c、图19a至图19c、图20a至图20c、图21a至图21c、图22a至图22c、图23a至图23c、图24a至图24c以及图25a至图25f为纳米fets于制造中间阶段的剖面图。

10.附图标记如下:

11.50:基板

12.52:堆叠

13.54:半导体层

14.56:半导体层

15.58:掩模

16.62:半导体鳍片

17.64:纳米结构

18.66:纳米结构

19.68:通道区

20.72:隔离区(sti区)

21.74:牺牲层

22.76:牺牲间隔物

23.79:缝隙

24.80:上介电层

25.81:缝隙

26.82:绝缘鳍片

27.83:空隙

28.84:虚设栅极层

29.86:掩模层

30.94:虚设栅极

31.96:掩模

32.98:栅极间隔物

33.104:凹口

34.106:内间隔物

35.108:源极/漏极区

36.112:接触蚀刻停止层

37.114:层间电介质

38.116:凹口

39.118:开口

40.120:开口

41.124:栅极介电层

42.126:栅极电极层

43.127:开口

44.129:开口

45.130:栅极结构

46.132:隔离区

47.134:蚀刻停止层

48.136:层间电介质

49.142:栅极接触件

50.144:源极/漏极接触件

51.146:金属-半导体合金区

52.500:密集区

53.600:稀疏区

54.1000:区域

55.1002:区域

56.108a:衬层

57.108b:主层

58.108c:完成层

59.50n:n型区

60.50p:p型区

61.78a:衬层

62.78b:填充材料

63.80a:高介电常数介电层

64.80b:盖层

65.80c:高介电常数介电层

66.80d:盖层

67.80e:高介电常数介电层

68.80f:盖层

69.80g:高介电常数介电层

70.80h:盖层

71.80i:高介电常数介电层

72.80j:盖层

73.80k:高介电常数介电层

74.d1:距离

75.d2:距离

76.h1:高度

77.t1:厚度

78.t10:厚度

79.t11:厚度

80.t2:厚度

81.t3:厚度

82.t4:厚度

83.t5:厚度

84.t6:厚度

85.t7:厚度

86.t8:厚度

87.t9:厚度

88.w1:宽度

89.w2:宽度

具体实施方式

90.以下内容提供了许多不同实施例或范例,以实现本公开实施例的不同部件。以下描述组件和配置方式的具体范例,以简化本公开实施例。当然,这些仅仅是范例,而非意图限制本公开实施例。举例而言,在以下描述中提及于第二部件上方或其上形成第一部件,其可以包含第一部件和第二部件以直接接触的方式形成的实施例,并且也可以包含在第一部件和第二部件之间形成额外的部件,使得第一部件和第二部件可以不直接接触的实施例。此外,本公开实施例可在各个范例中重复参考标号及/或字母。此重复是为了简化和清楚的目的,其本身并非用于指定所讨论的各个实施例及/或配置之间的关系。

91.再者,其中可能用到与空间相对用词,例如“在

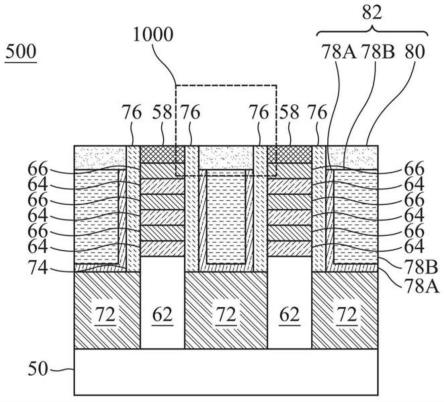

……

之下”、“下方”、“较低的”、“上方”、“上”等相似用词,是为了便于描述附图中一个(些)部件或特征与另一个(些)部件或特征之间的关系。空间相对用词用以包括使用中或操作中的装置的不同方位,以及附图中所描述的方位。当装置被转向不同方位时(旋转90度或其他方位),其中所使用的空间相对形容词也将依转向后的方位来解释。

92.根据一些实施例,使用绝缘鳍片。例如,在一些实施例中,绝缘鳍片形成在纳米结构的堆叠之间,用于例如减少源极/漏极区不期望的合并(merging)。绝缘鳍片的顶部形成有交替的高介电常数介电层以及盖层。盖层可以减少绝缘鳍片顶表面上的局部裸片(local grain)成长导致的挤压缺陷(extrusion defects)。当平坦化绝缘鳍片时,交替的高介电常数介电层以及盖层也可以用于改善薄膜质量并且更好地控制化学机械研磨(chemical mechanical polish,cmp)速率。

93.在本公开中描述包括纳米fets的裸片的一些实施例。然而,各种实施例可以应用于包括代替纳米fets或与纳米fets组合的其他类型的晶体管(例如,鳍式场效晶体管(fin field-effect transistors,finfets)、平面晶体管等)的裸片。

94.根据一些实施例,图1示出纳米fets(例如,纳米线fets、纳米片fets等)的示例。图1为三维视图,其为了清楚显示而省略纳米fets的一些部件。纳米fets可以是纳米片场效晶体管(nanosheet field-effect transistors,nsfets)、纳米线场效晶体管(nanowire field-effect transistors,nwfets)、全绕式栅极场效晶体管(gate-all-around field-effect transistors,gaafets)等。

95.纳米fets在基板50(例如,半导体基板)上的半导体鳍片62上方包括纳米结构66,纳米结构66作为纳米fets的通道区。纳米结构66可以包括p型纳米结构、n型纳米结构或其组合。隔离区72,例如浅沟槽隔离(shallow trench isolation,sti)区,设置在相邻的半导

体鳍片62之间,半导体鳍片62在相邻的隔离区72上方及之间突出。尽管将隔离区72描述/示出为与基板50分离,但是如本公开中所使用,术语“基板”可以是指单独的半导体基板或与隔离区结合的半导体基板。此外,尽管半导体鳍片62的底部被示为与基板50分开,然而半导体鳍片62的底部可以是与基板50相同的、连续的材料。在本公开中,半导体鳍片62是指在相邻的隔离区72上方以及之间延伸的部分。

96.栅极结构130在半导体鳍片62的顶表面上方,并沿着纳米结构66的顶表面、侧壁以及底表面设置。外延源极/漏极区108设置在位于栅极结构130的相对侧的半导体鳍片62上。外延源极/漏极区108可以在各种半导体鳍片62之间共享。例如,相邻的外延源极/漏极区108可以电性连接,例如通过将外延源极/漏极区108与相同的源极/漏极接触件耦合。

97.绝缘鳍片82,也称为混合鳍片或介电鳍片,设置在隔离区72上方以及相邻的外延源极/漏极区108之间。绝缘鳍片82阻止外延成长以防止外延成长期间外延源极/漏极区108的聚结(coalescing)。例如,绝缘鳍片82可以形成在单元(cell)边界处以分开相邻单元的外延源极/漏极区108。绝缘鳍片82可以包括衬层78a、填充材料78b、以及在衬层78a以及填充材料78b上方的上介电层80。

98.图1进一步示出在后续附图中所使用的参考剖面。剖面a-a’沿着半导体鳍片62的纵轴,并且,例如,沿着纳米fets的外延源极/漏极区108之间的电流流动方向。剖面b-b’沿着栅极结构130的纵轴,并且,例如,垂直于纳米fets的外延源极/漏极区108之间的电流流动方向。剖面c-c’平行于剖面b-b’,并延伸穿过纳米fets的外延源极/漏极区108。为了清楚起见,后续附图参考这些参考剖面。

99.根据一些实施例,图2至图25e为在制造纳米fets的中间阶段的视图。图2、图3以及图4为三维视图。图5a、图6a、图7a、图8a、图13a、图14a、图15a、图16a、图17a、图18a、图19a、图20a、图21a、图22a、图23a、图24a以及图25a为沿着与图1中的参考剖面a-a’相似的剖面所示出的剖面图。图5b、图5c、图6b、图6c、图7b、图7c、图8b、图8c、图8d、图8e、图8f、图9a、图9b、图10a、图10b、图11a、图11b、图12a、图12b、图13b、图13c、图13d、图13e、图13f、图14b、图14c、图14d、图14e、图15b、图16b、图17b、图18b、图19b、图20b、图21b、图22b、图23b、图24b、图25b、图25d以及图25e图为沿着与图1中的参考剖面b-b’相似的剖面所示出的剖面图。图15c、图16c、图17c、图18c、图19c、图20c、图21c、图22c、图23c、图24c以及图25c为沿着与图1中的参考剖面c-c’相似的剖面所示出的剖面图。

100.在图2中,提供用以形成纳米fets的基板50。基板50可以是半导体基板,例如,块体半导体、绝缘体上半导体(semiconductor-on-insulator,soi)基板等,其可以掺杂(例如,用p型掺质或n型杂质)或不掺杂。基板50可以是晶片,例如硅晶片。一般来说,soi基板是在绝缘层上形成的半导体材料层。绝缘层可以是,例如埋入式氧化物(buried oxide,box)层、氧化硅层等。绝缘层通常设置在基板上,例如硅基板或玻璃基板上。也可以使用其他基板,例如多层基板或梯度基板。在一些实施例中,基板50的半导体材料可以包括硅(si)、锗(ge);化合物半导体,包括碳化硅(sic)、砷化镓(gaas)、磷化镓(gap)、磷化铟(inp)、砷化铟(inas)及/或锑化铟(insb);合金半导体,包括硅锗(sige)、磷砷化镓(gaasp)、砷化铝铟(alinas)、砷化铝镓(algaas)、砷化镓铟(gainas)、磷化镓铟(gainp)及/或磷砷化镓铟(gainasp);其组合;或相似材料。

101.基板50具有n型区50n及p型区50p。n型区50n可以用于形成n型装置,例如nmos晶体

管(例如,n型纳米fets)。p型区50p可以用于形成p型装置,例如pmos晶体管(例如,p型纳米fets)。n型区50n可以与p型区50p实体分离(未单独示出),并且可以在n型区50n与p型区50p之间设置任意数量的装置部件(例如,其他有源装置、掺杂区、隔离结构等)。尽管示出一个n型区50n和一个p型区50p,然而可以提供任何数量的n型区50n和p型区50p。

102.基板50可以被轻掺杂有p型或n型杂质。可以对基板50的上部执行抗击穿(anti-punch-through,apt)注入,以形成apt区。在apt注入期间,可以将杂质注入到基板50中。杂质的导电类型可以与随后将形成在每个n型区50n和p型区50p中的源极/漏极区的导电类型相反。apt区可以在纳米fets中的源极/漏极区下方延伸。apt区可以用于减少从源极/漏极区到基板50的漏电流。在一些实施例中,apt区中的掺杂浓度可以为大约10

18

cm-3

至大约10

19

cm-3

。

103.多层堆叠52形成在基板50上方。多层堆叠52包括交替的第一半导体层54和第二半导体层56。第一半导体层54由第一半导体材料形成,并且第二半导体层56由第二半导体材料形成。半导体材料可以各自选自基板50的候选半导体材料。在所示的实施例中,多层堆叠52包括三层的第一半导体层54和三层的第二半导体层56。应当理解,多层堆叠52可以包括任意数量的第一半导体层54和第二半导体层56。例如,多层堆叠52可以包括一层至十层的第一半导体层54和一层至十层的第二半导体层56。

104.在所示的实施例中,并且如随后将更详细地描述,第一半导体层54将被去除,并且第二半导体层56将被图案化以在n型区50n和p型区50p中形成用于纳米fets的通道区。第一半导体层54为牺牲层(或虚设层),其将在后续工艺中被去除以露出第二半导体层56的顶表面和底表面。第一半导体层54的第一半导体材料是相对于第二半导体层56的蚀刻具有高蚀刻选择性的材料,例如硅锗。第二半导体层56的第二半导体材料是适用于n型和p型装置的材料,例如硅。

105.在另一实施例中(未单独示出),第一半导体层54将被图案化以在一个区(例如,p型区50p)中形成用于纳米fets的通道区,并且第二半导体层56将被图案化以在另一个区中形成用于纳米fets的通道区(例如,n型区50n)。第一半导体层54的第一半导体材料可以是适用于p型装置的材料,例如硅锗(例如si

x

ge

1-x

,其中x可以在0至1之间)、纯锗、iii-v族化合物半导体、ii-vi族化合物半导体等。第二半导体层56的第二半导体材料可以是适用于n型装置的材料,例如硅、碳化硅、iii-v族化合物半导体、ii-vi族化合物半导体等。第一半导体材料和第二半导体材料可以具有相对于彼此蚀刻的高蚀刻选择性,从而可以在不去除n型区50n中的第二半导体层56的情况下去除第一半导体层54,并且可以在不去除p型区50p中的第一半导体层54的情况下去除第二半导体层56。每个膜层可以具有小的厚度,例如5纳米至30纳米的厚度。

106.在图3中,在基板50和多层堆叠52中图案化沟槽以形成半导体鳍片62、纳米结构64和纳米结构66。半导体鳍片62是在基板50中图案化的半导体条(strips)。纳米结构64和纳米结构66分别包括第一半导体层54和第二半导体层56的剩余部分。可以通过任何可接受的蚀刻工艺图案化沟槽,例如反应离子蚀刻(reactive ion etch,rie)、中性束蚀刻(neutral beam etch,nbe)等或其组合。蚀刻可以是各向异性蚀刻。

107.半导体鳍片62、纳米结构64和纳米结构66可以通过任何合适的方法图案化。例如,可以使用一种或多种光刻工艺以图案化半导体鳍片62、纳米结构64和纳米结构66,包括双

重图案化或多重图案化工艺。一般来说,双重图案或多重图案工艺将光刻工艺结合自对准工艺,允许创建图案,例如,其节距(pitch)比使用单一直接光刻工艺可获得的节距小。例如,在一实施例中,在基板上方形成牺牲层,并使用光刻工艺对其进行图案化。使用自对准工艺在图案化的牺牲层旁边形成间隔物。然后去除牺牲层,之后可以使用剩余的间隔物作为掩模58以图案化半导体鳍片62、纳米结构64和纳米结构66。

108.在一些实施例中,半导体鳍片62和纳米结构64、66各自具有8纳米至40纳米的宽度。在所示实施例中,半导体鳍片62和纳米结构64、66在n型区50n和p型区50p中具有大抵相等的宽度。在另一实施例中,一个区(例如,n型区50n)中的半导体鳍片62和纳米结构64、66比另一区(例如,p型区50p)中的半导体鳍片62和纳米结构64、66更宽或更窄。

109.在图4中,sti区72形成在基板50上方和相邻的半导体鳍片62之间。sti区72设置在半导体鳍片62的至少一部分周围,使得纳米结构64、66的至少一部分从相邻的sti区72之间突出。在所示的实施例中,sti区72的顶表面在半导体鳍片62的顶表面下方。在一些实施例中,sti区72的顶表面在半导体鳍片62的顶表面上方或与其共平面(在工艺变化内)。

110.sti区72可以通过任何合适的方法形成。例如,绝缘材料可以形成在基板50和纳米结构64、66上方以及相邻的半导体鳍片62之间。绝缘材料可以是氧化物,例如氧化硅、氮化物,例如氮化硅等或其组合,其可以通过化学气相沉积(chemical vapor deposition,cvd)工艺,例如高密度等离子体cvd(high density plasma cvd,hdp-cvd)、流动式cvd(flowable cvd,fcvd)等或其组合形成。可以使用通过任何可接受的工艺形成的其他绝缘材料。在一些实施例中,绝缘材料是通过fcvd工艺形成的氧化硅。一旦形成绝缘材料,就可以执行退火工艺。在一个实施例中,绝缘材料被形成为过量的绝缘材料以覆盖纳米结构64、66。尽管隔离区72各自被示出为单层,但是一些实施例可以利用多个膜层。例如,在一些实施例中,可以首先沿着基板50、半导体鳍片62以及纳米结构64、66的表面形成衬层(未单独示出)。之后,可以在衬层上方形成绝缘材料,例如,上述所讨论的材料。

111.去除工艺被应用于绝缘材料以去除纳米结构64、66上方多余的绝缘材料。在一些实施例中,可以利用平坦化工艺,例如化学机械研磨(chemical mechanical polish,cmp)、回蚀工艺、其组合等。在一些实施例中,平坦化工艺可以露出掩模58或去除掩模58。在平坦化工艺之后,绝缘材料的顶表面和掩模58或纳米结构64、66共平面(在工艺变化内)。因此,掩模58(若存在)或纳米结构64、66的顶表面通过绝缘材料露出。在所示的实施例中,掩模58保留在纳米结构64、66上。之后,绝缘材料被凹蚀以形成sti区72。绝缘材料被凹蚀,使得纳米结构64、66的至少一部分从绝缘材料的相邻部分之间突出。此外,通过应用适当的蚀刻,sti区72的顶表面可以具有如图所示的平坦表面、凸(convex)表面、凹(concave)表面(例如,碟形(dishing)表面)或其组合。可以使用可接受的蚀刻工艺凹蚀sti区72,例如对绝缘材料的材料具有选择性的蚀刻工艺(例如,以比蚀刻半导体鳍片62以及纳米结构64、66的材料更快的速率选择性蚀刻sti区72的绝缘材料)。例如,可以执行使用稀释氢氟酸(dilute hydrofluoric,dhf)的氧化物去除。

112.以上描述的工艺仅仅是可以形成半导体鳍片62以及纳米结构64、66的一个示例。在一些实施例中,半导体鳍片62及/或纳米结构64、66可以通过利用掩模以及外延成长工艺形成。例如,可以在基板50的顶表面上方形成介电层,并且可以蚀刻沟槽穿过介电层以露出下方的基板50。可以在沟槽中外延成长外延结构,并且可以凹蚀介电层,使得外延结构从介

电层突出以形成半导体鳍片62及/或纳米结构64、66。外延结构可以包括以上讨论的交替的半导体材料,例如第一半导体材料和第二半导体材料。在外延成长外延结构的一些实施例中,外延成长的材料可以在成长工艺中被原位掺杂,其可省去之前和之后的注入,尽管如此,原位和注入掺杂亦可以一起使用。

113.此外,可以在纳米结构64、66、半导体鳍片62及/或基板50中形成适当的阱(未单独示出)。阱的导电类型可以与随后将各别形成在n型区50n和p型区50p中的源极/漏极区的导电类型相反。在一些实施例中,在n型区50n中形成p型阱,并且在p型区50p中形成n型阱。在一些实施例中,在n型区50n和p型区50p两者中形成p型阱或n型阱。

114.在具有不同阱类型的一些实施例中,可以使用掩模(未单独示出)例如光刻胶,以实现用于n型区50n和p型区50p的不同注入步骤。例如,可以在n型区50n中的半导体鳍片62、纳米结构64、66和sti区72上方形成光刻胶。图案化光刻胶以露出p型区50p。可以通过使用旋转涂布技术形成光刻胶,并且可以使用可接受的光刻技术对光刻胶进行图案化。一旦图案化光刻胶,就可以在p型区50p中执行n型杂质注入,并且光刻胶可以用作掩模以大抵防止n型杂质被注入到n型区50n中。n型杂质可以是注入到其区中的磷、砷、锑等,杂质浓度可以在10

13

cm-3

至10

14

cm-3

之间。在注入之后,例如通过可接受的灰化(ashing)工艺去除光刻胶。

115.在注入p型区50p之后或之前,在p型区50p中的半导体鳍片62、纳米结构64、66和sti区72上方形成掩模,例如光刻胶。图案化光刻胶以露出n型区50n。可以通过使用旋转涂布技术形成光刻胶,并且可以使用可接受的光刻技术对光刻胶进行图案化。一旦图案化光刻胶,就可以在n型区50n中执行p型杂质注入,并且光刻胶可以用作掩模以大抵防止p型杂质被注入到p型区50p中。p型杂质可以是注入到其区中的硼、氟化硼、铟等,杂质浓度可以在10

13

cm-3

至10

14

cm-3

之间。在注入之后,例如通过可接受的灰化工艺去除光刻胶。

116.在n型区50n和p型区50p的注入之后,可以执行退火以修复注入损伤并活化注入的p型及/或n型杂质。在外延结构为外延成长的半导体鳍片62及/或纳米结构64、66的一些实施例中,外延成长材料可以在成长期间被原位掺杂,其可以避免注入,尽管原位掺杂及注入掺杂可以一起使用。

117.图5a至图25e示出制造实施例装置的各种额外步骤。图5a至图25f示出在n型区50n或p型区50p中的部件。例如,所示的结构可以适用于n型区50n和p型区50p。n型区50n和p型区50p的结构差异(若有差异)将在各附图相应的文字中描述。如随后将更详细描述,绝缘鳍片82将形成在半导体鳍片62之间。图5a、图6a、图7a、图8a、图13a、图14a、图15a、图16a、图17a、图18a、图19a、图20a、图21a、图22a、图23a、图24a及图25a示出半导体鳍片62以及在其上形成的结构。图5b、图5c、图6b、图6c、图7b、图7c、图8b、图8c、图8d、图8e、图9a、图9b、图10a、图10b、图11a、图11b、图12a、图12b、图13b、图13c、图13d、图13e、图14b、图14c、图14d、图14e、图15b、图15c、图16b、图16c、图17b、图17c、图18b、图18c、图19b、图19c、图20b、图20c、图21b、图21c、图22b、图22c、图23b、图23c、图24b、图24c、图25b及图25c各别示出两个半导体鳍片62以及部分的绝缘鳍片82和sti区72,其设置在相应剖面中的两个半导体鳍片62之间。图8f、图13f及图25d各别示出四个半导体鳍片62以及部分的绝缘鳍片82和sti区72,其设置在相应剖面中的四个半导体鳍片62之间。

118.图5a示出半导体鳍片62,图5b示出基板50的密集区(dense area)500中的两个半导体鳍片62,并且图5c示出基板50的稀疏区(sparse area)600中的两个半导体鳍片62。密

集区500可以包括n型区50n和p型区50p(未单独示出)。在一些实施例中,密集区500的n型区50n中的半导体鳍片62的宽度可以大于或小于密集区500的p型区50p中的半导体鳍片62的宽度,并且稀疏区600的n型区50n中的半导体鳍片62的宽度可以大于或小于稀疏区600的p型区50p中的半导体鳍片62的宽度。此外,虽然半导体鳍片62和纳米结构64、66各别被示为具有一致的宽度,但在其他实施例中,半导体鳍片62及/或纳米结构64、66可以具有锥形(tapered)侧壁,使得半导体鳍片62及/或纳米结构64、66各别的宽度在朝向基板50的方向上连续增加。在这样的实施例中,纳米结构64、66可以各别具有不同的宽度并且为梯形(trapezoidal)。在一些实施例中,密集区500中的半导体鳍片62相隔20纳米至40纳米的距离d1。稀疏区600可以包括n型区50n和p型区50p(未单独示出)。在一些实施例中,稀疏区600中的半导体鳍片62相隔40纳米至600纳米的距离d2。

119.在图5a至图5c中,牺牲层74顺应地(conformally)形成在掩模58(若存在)、半导体鳍片62、纳米结构64、66以及sti区72上方。牺牲层74可由半导体材料(例如选自基板50的候选半导体材料中的一种)形成,其可以通过工艺,例如气相外延(vapor phase epitaxy,vpe)或分子束外延(molecular beam epitaxy,mbe)成长,通过工艺,例如化学气相沉积(cvd)或原子层沉积(atomic layer deposition,ald)等沉积。例如,牺牲层74可以由硅或硅锗形成。

120.在图6a至图6c中,牺牲层74被图案化以在掩模58(若存在)、半导体鳍片62和纳米结构64、66周围形成牺牲间隔物76。牺牲间隔物76设置在sti区72上方。当被图案化时,牺牲层74具有留在掩模58(若存在)、半导体鳍片62和纳米结构64、66的侧壁上的部分(从而形成牺牲间隔物76)。牺牲间隔物76覆盖纳米结构64、66的侧壁,其将在后续工艺中露出以形成通道区。牺牲间隔物76在工艺期间用作暂时的间隔物,并且随后将被去除以露出部分纳米结构66的侧壁,其将用作纳米fets的通道区。详细而言,在所示的实施例中,牺牲间隔物76和纳米结构64随后将被去除并替换为包绕(wrap around)纳米结构66的栅极结构。牺牲间隔物76由对纳米结构66的材料的蚀刻具有高蚀刻选择性的材料形成。牺牲间隔物76可以由与纳米结构64相同的半导体材料形成,或者可以由不同的半导体材料形成。在随后的工艺步骤中,虚设栅极层84可以沉积在牺牲间隔物76的部分之上(参考以下图15a至图15c),并且虚设栅极层84可以被图案化以提供虚设栅极94,其包括牺牲间隔物76的下方部分(参考以下图16a至图16c)。这些虚设栅极94(例如,虚设栅极层84的图案化部分和牺牲间隔物76的部分)随后可以被功能性栅极堆叠替换。

121.在图6a至图6c中,执行第一蚀刻工艺以初始将牺牲层74(参考图5a至图5b)图案化至牺牲间隔物76中。牺牲层74在掩模58(若存在)或纳米结构64、66上方的部分通过第一蚀刻工艺被去除。沿着纳米结构64、66的牺牲间隔物76可以被图案化,使得纳米结构64、66之间的sti区72露出,如图6a至图6b所示。第一蚀刻工艺可以是干式蚀刻、湿式蚀刻等或其组合。第一蚀刻工艺可以为各向异性的。在一些实施例中,露出的sti区72的顶部被凹蚀至牺牲间隔物76的底表面以下的深度(参考以下图8f)。此外,半导体鳍片62对之间的每个sti区72的凹蚀量可以变化(参考以下图8f)。

122.图7a至图14e示出在邻近半导体鳍片62和纳米结构64、66的牺牲间隔物76之间形成绝缘鳍片82(也称为混合鳍片或介电鳍片)。绝缘鳍片82可以使随后形成的源极/漏极区(参考以下图18a和图18c)彼此绝缘。

123.在图7a至图7c中,在结构上方形成衬层78a和填充材料78b。衬层78a通过可接受的沉积工艺顺应地沉积在sti区72、掩模58、半导体鳍片62、纳米结构64、66和牺牲间隔物76露出的表面上,例如原子层沉积(ald)、化学气相沉积(cvd)、低压化学气相沉积(low-pressure cvd,lpcvd)、等离子体辅助化学气相沉积(plasma-enhanced cvd,pecvd)、流动式化学气相沉积(fcvd)、分子束沉积(molecular-beam deposition,mbd)、物理气相沉积(physical vapor deposition,pvd)等。衬层78a可由一种或多种介电材料形成,其介电材料具有对于半导体鳍片62、纳米结构64、66和牺牲间隔物76的蚀刻的高蚀刻选择性,例如氮化物,例如氮化硅、碳氮化硅、碳氮氧化硅等。衬层78a可以在随后形成填充材料78b(参考以下图8a和图8b)的期间减少牺牲间隔物76的氧化,其可有利于随后去除牺牲间隔物76。

124.接着,填充材料78b形成在衬层78a之上,填充半导体鳍片62和纳米结构64、66之间未被牺牲间隔物76或衬层78a填充的剩余区域,并且可以形成在掩模58(若存在)或纳米结构64、66的顶表面上方。填充材料78b可以形成绝缘鳍片82的大部分下部(参考图14a至图14d)以将随后形成的源极/漏极区(参考以下图18b)彼此绝缘。填充材料78b可以通过可接受的沉积工艺形成,例如ald、cvd、lpcvd、pecvd、fcvd、mbd、pvd等。填充材料78b可由一种或多种介电材料形成,其介电材料具有对于半导体鳍片62、纳米结构64、66和牺牲间隔物76的蚀刻的高蚀刻选择性,例如氧化物,例如氧化硅、氮氧化硅、碳氮氧化硅、碳氧化硅等或其组合。

125.在图8a至图8e中,可以使用一种或多种可接受的平坦化及/或蚀刻工艺,例如对衬层78a和填充材料78b具有选择性的一种工艺,去除在掩模58的顶表面上方的衬层78a和填充材料78b的上部(例如,以比蚀刻牺牲间隔物76的材料更快的速率选择性地蚀刻衬层78a和填充材料78b的材料)。在蚀刻之后,衬层78a和填充材料78b的顶表面可以低于掩模58(若存在)及/或纳米结构64、66的顶表面,并且开口127、129被定义在衬层78a和填充材料78b上方以及相邻的牺牲间隔物76之间的区域中。开口127位于密集区500中,而开口129位于稀疏区600中。图8d示出图8b所示的密集区500的区域1000的详细视图,并且图8e示出图8c所示的稀疏区600的区域1002的详细视图。开口129可以比开口127宽。在一些实施例中,密集区500中牺牲间隔物76的相对侧壁之间的开口127具有20纳米至40纳米的宽度w1,并且稀疏区600中的半导体鳍片62上方的牺牲间隔物76的相对侧壁之间的开口129具有40纳米至600纳米的宽度w2。

126.根据一些实施例,图8f示出具有四个半导体鳍片62以及设置在它们之间的三个sti区72的密集区500的区域详细视图。衬层78a和填充材料78b的剩余部分设置在相邻的半导体鳍片62对之间。相邻的半导体鳍片62对之间的每个sti区72的凹蚀量可以变化。在一些实施例中,sti区72的顶表面为凹陷的(参考以上图6a至图6c),并且衬层78a及/或填充材料78b在sti区72的顶表面下方延伸。此外,如图8f所示,由于上述去除衬层78a和填充材料78b的上部,衬层78a及/或填充材料78b的顶表面可以具有凹形轮廓。

127.图9a至图13e示出在衬层78a和填充材料78b上形成上介电层80以形成绝缘鳍片82的顶部。上介电层80可以包括交替的高介电常数介电层80a、80c、80e、80g、80i和80k,以及盖层80b、80d、80f、80h和80j,其可以减少由绝缘鳍片82的顶表面上的局部裸片成长导致的挤压缺陷。使用交替的高介电常数介电层和盖层还可以通过增加膜层均一性以改善膜层质量的控制和后续cmp的研磨速率(参考以下图14a至图14e)。作为示例,图9a至图13e示出包

括六个高介电常数介电层以及五个盖层的上介电层80。然而,可以形成任何合适数量的交替高介电常数介电层以及盖层。

128.在图9a至图9b中,在密集区500的开口127和稀疏区600的开口129中的半导体鳍片62上方的衬层78a、填充材料78b和牺牲间隔物76上方形成第一高介电常数介电层80a和第一盖层80b。图9a示出接续图8d的区域1000的视图,并且图9b示出接续图8e的区域1002的视图。第一高介电常数介电层80a可以由高介电常数介电材料(例如,具有大于约7的介电常数值)形成,例如氧化铪、氧化锆、氧化锆铝、氧化铪铝、氧化铪硅、氧化铝等;或其组合,其可以通过顺应性沉积工艺例如通过cvd、ald等沉积。在一些实施例中,衬层78a和填充材料78b由与掩模58相同或相似的材料形成,所以选择第一高介电常数介电层80a的材料以与衬层78a和填充材料78b的材料具有蚀刻选择性。这可以保护衬层78a和填充材料78b免受随后去除掩模58的工艺的影响(参考以下图21b)。在一些实施例中,第一高介电常数介电层80a以大抵非结晶态沉积,并且第一高介电常数介电层80可以随后通过退火结晶(参考以下图14a至图14e)

129.在一些实施例中,第一高介电常数介电层80a形成为3纳米至12纳米的第一厚度t1,其可以有益于沉积具有相对均一的膜特性和质量的第一高介电常数介电层80a(例如,均一地非晶态),而不形成挤压缺陷。将第一高介电常数介电层80a形成为小于3纳米的厚度可能是不利的,因为在随后的退火工艺中导致第一高介电常数介电层80a的结晶不充分(参考以下图14a至图14e)。将第一高介电常数介电层80a形成为大于12纳米的厚度可能是不利的,导致来自第一高介电常数介电层80a的材料的局部裸片成长的挤压缺陷。

130.接着,在第一高介电常数介电层80a上方形成第一盖层80b。第一盖层80b通过抑制第一高介电常数介电层80a的材料的局部裸片成长,以减少可能出现在第一高介电常数介电层80a的顶表面上的挤压缺陷。在一些实施例中,第一盖层80b覆盖第一高介电常数介电层80a的内侧壁。第一盖层80b可由氧化物、氮化物或碳化物形成,例如氧化硅、二氧化硅、氮化硅、碳化硅等或其组合,其可以通过顺应性沉积工艺沉积(例如从形成填充材料78b的候选方法中选择的一种;参考以上图7a至图7c)。

131.在一些实施例中,第一盖层80b形成为0.5纳米至2纳米的第二厚度t2,其可以有益于减少挤压缺陷。将第一盖层80b形成为小于0.5纳米的厚度可能会导致在上介电层80的顶表面上出现不希望的挤压缺陷。由于盖层材料(例如,第一盖层80b)和高介电常数介电层材料(例如,第一高介电常数介电层80a)的蚀刻速率显著不同,将第一盖层80b形成为大于2纳米的厚度可能导致上介电层80的顶表面不平坦以及后续工艺问题。

132.在一些实施例中,第一盖层80b的第二厚度t2与第一高介电常数介电层80a的第一厚度t1的比例在0.04至0.7,其可以有益于减少挤压缺陷。t2:t1的比例小于0.04会导致在上介电层80的顶表面上出现不希望的挤压缺陷。由于第一盖层80b和第一高介电常数介电层80a的蚀刻速率显著不同,t2:t1的比例大于0.7可能导致上介电层80的顶表面不平整(uneven)和后续工艺问题。

133.在图10a至图10b中,在第一盖层80b上方形成第二高介电常数介电层80c和第二盖层80d。第二高介电常数介电层80c可以填充密集区500的开口127。在一些实施例中,第二高介电常数介电层80c的外侧壁和底表面覆盖第一盖层80b的一部分,并且第二高介电常数介电层80c的部分插入(interposed)在第一高介电常数介电层80a的相应侧壁部分和第一盖

层80b的相应侧壁部分之间。第二高介电常数介电层80c和第二盖层80d可以分别使用与第一高介电常数介电层80a和第一盖层80b相同的材料和方法形成,如上文关于图9a至图9b。为了填充开口127而不因为第二高介电常数介电层80c的顶表面的早期合并及/或第一盖层80b的合并而形成空隙(voids),在形成第二高介电常数介电层80c之前,可以控制第一高介电常数介电层80a的第一厚度t1和第一盖层80b的第二厚度t2(参考以上图9a至图9b)以保持开口127的深宽比(aspect ratio)小于2。例如,当第一开口127的宽度在前述范围时,当开口127被第二高介电常数介电层80c或第一盖层80b的不期望的合并填充时,第一高介电常数介电层80a可以形成为3纳米至5纳米的厚度以减少空隙的形成。在一些实施例中,由于第二高介电常数介电层80c的合并以填充第一开口127,因而在第二高介电常数介电层80c中形成缝隙(seams)79。

134.在一些实施例中,第二高介电常数介电层80c形成为3纳米至12纳米的第三厚度t3,其可以有益于沉积具有相对均一的膜特性和质量的第二高介电常数介电层80c(例如,均一地非晶态),而不形成挤压缺陷。将第二高介电常数介电层80c形成为小于3纳米的厚度可能是不利的,因为在随后的退火工艺中导致第二高介电常数介电层80c的结晶不充分(参考以下图14a至图14e)。将第二高介电常数介电层80c形成为大于12纳米的厚度可能是不利的,导致来自第二高介电常数介电层80c的材料的局部裸片成长的挤压缺陷。在一些实施例中,第二盖层80d形成为0.5纳米至2纳米的第四厚度t4,其可以有益于减少挤压缺陷。将第二盖层80d形成为小于0.5纳米的厚度可能会导致在上介电层80的顶表面上出现不希望的挤压缺陷。由于盖层材料(例如,第二盖层80d)和高介电常数介电层材料(例如,第二高介电常数介电层80c)的蚀刻速率显著不同,将第二盖层80d形成为大于2纳米的厚度可能导致上介电层80的顶表面不平整以及后续工艺问题。

135.在一些实施例中,第二盖层80d的第四厚度t4与第二高介电常数介电层80c的第三厚度t3的比例在0.04至0.7,其可以有益于减少挤压缺陷。t4:t3的比例小于0.04会导致在上介电层80的顶表面上出现不希望的挤压缺陷。由于第二盖层80d和第二高介电常数介电层80c的蚀刻速率显著不同,t4:t3的比例大于0.7可能导致上介电层80的顶表面不平整和后续工艺问题。

136.在图11a至图11b中,在第二盖层80d上方形成第三高介电常数介电层80e和第三盖层80f。第三高介电常数介电层80e和第三盖层80f可以分别使用与第一高介电常数介电层80a和第一盖层80b相同的材料和方法形成,如上文关于图9a至图9b所述。在一些实施例中,第三高介电常数介电层80e形成为3纳米至12纳米的第五厚度t6,其可以有益于沉积具有相对均一的膜特性和质量的第三高介电常数介电层80e(例如,均一地非晶态),而不形成挤压缺陷。将第三高介电常数介电层80e形成为小于3纳米的厚度可能是不利的,因为在随后的退火工艺中导致第三高介电常数介电层80e的结晶不充分(参考以下图14a至图14e)。将第三高介电常数介电层80e形成为大于12纳米的厚度可能是不利的,导致来自第三高介电常数介电层80e的材料的局部裸片成长的挤压缺陷。在一些实施例中,第三盖层80f形成为0.5纳米至2纳米的第六厚度t6,其可以有益于减少挤压缺陷。将第三盖层80f形成为小于0.5纳米的厚度可能会导致在上介电层80的顶表面上出现不希望的挤压缺陷。由于盖层材料(例如,第三盖层80f)和高介电常数介电层材料(例如,第三高介电常数介电层80e)的蚀刻速率显著不同,将第三盖层80f形成为大于2纳米的厚度可能导致上介电层80的顶表面不平整以

及后续工艺问题。

137.在一些实施例中,第三盖层80f的第六厚度t6与第三高介电常数介电层80e的第五厚度t5的比例在0.04至0.7,其可以有益于减少挤压缺陷。t6:t5的比例小于0.04会导致在上介电层80的顶表面上出现不希望的挤压缺陷。由于第三盖层80f和第三高介电常数介电层80e的蚀刻速率显著不同,t6:t5的比例大于0.7可能导致上介电层80的顶表面不平整和后续工艺问题。

138.在图12a至图12b中,在第三盖层80f上方形成第四高介电常数介电层80g和第四盖层80h。在一些实施例中,在形成第四高介电常数介电层80g和第四盖层80h之后,开口129的底表面在后续平坦化结构上方(参考以下图14a至图14e)。在一些实施例中,第四高介电常数介电层80g形成为3纳米至12纳米的第七厚度t7,其可以有益于沉积具有相对均一的膜特性和质量的第四高介电常数介电层80g(例如,均一地非晶态),而不形成挤压缺陷。将第四高介电常数介电层80g形成为小于3纳米的厚度可能是不利的,因为在随后的退火工艺中导致第四高介电常数介电层80g的结晶不充分(参考以下图14a至图14e)。将第四高介电常数介电层80g形成为大于12纳米的厚度可能是不利的,导致来自第四高介电常数介电层80g的材料的局部裸片成长的挤压缺陷。在一些实施例中,第四盖层80h形成为0.5纳米至2纳米的第八厚度t8,其可以有益于减少挤压缺陷。将第四盖层80h形成为小于0.5纳米的厚度可能会导致在上介电层80的顶表面上出现不希望的挤压缺陷。由于盖层材料(例如,第四盖层80h)和高介电常数介电层材料(例如,第四高介电常数介电层80g)的蚀刻速率显著不同,将第四盖层80h形成为大于2纳米的厚度可能导致上介电层80的顶表面不平整以及后续工艺问题。

139.在一些实施例中,第四盖层80h的第八厚度t8与第四高介电常数介电层80g的第七厚度t7的比例在0.04至0.7,其可以有益于减少挤压缺陷。t8:t7的比例小于0.04会导致在上介电层80的顶表面上出现不希望的挤压缺陷。由于第四盖层80h和第四高介电常数介电层80g的蚀刻速率显著不同,t8:t7的比例大于0.7可能导致上介电层80的顶表面不平整和后续工艺问题。

140.在图13a至图13e中,在第四盖层80h上方形成第五高介电常数介电层80i、第五盖层80j和第六高介电常数介电层80k。在一些实施例中,第五高介电常数介电层80i、第五盖层80j和第六高介电常数介电层80k填充及/或覆盖开口129(参考以上图12b)。第五高介电常数介电层80i和第六高介电常数介电层80k可以使用与第一高介电常数介电层80a相同的材料和方法形成,并且第五盖层80j可以使用与第一盖层80b相同的材料和方法形成,如以上关于图9a至图9b所述。在一些实施例中,第五高介电常数介电层80i或第六高介电常数介电层80k在填充工艺期间合并并且由于合并而形成缝隙81。空隙83可以沿着缝隙81形成并且可以通过随后的平坦化去除(参考以下图14a至图14e)。在一些实施例中,第五高介电常数介电层80i形成为3纳米至12纳米的第九厚度t9,其可以有益于沉积具有相对均一的膜特性和质量的第五高介电常数介电层80i(例如,均一地非晶态),而不形成挤压缺陷。将第五高介电常数介电层80i形成为小于3纳米的厚度可能是不利的,因为在随后的退火工艺中导致第五高介电常数介电层80i的结晶不充分(参考以下图14a至图14e)。将第五高介电常数介电层80i形成为大于12纳米的厚度可能是不利的,导致来自第五高介电常数介电层80i的材料的局部裸片成长的挤压缺陷。在一些实施例中,第五盖层80j形成为0.5纳米至2纳米的

第十厚度t10,其可以有益于减少挤压缺陷。将第五盖层80j形成为小于0.5纳米的厚度可能会导致在上介电层80的顶表面上出现不希望的挤压缺陷。由于盖层材料(例如,第五盖层80j)和高介电常数介电层材料(例如,第五高介电常数介电层80i)的蚀刻速率显著不同,将第五盖层80j形成为大于2纳米的厚度可能导致上介电层80的顶表面不平整以及后续工艺问题。

141.在一些实施例中,第五盖层80j的第十厚度t10与第五高介电常数介电层80i的第九厚度t9的比例在0.04至0.7,其可以有益于减少挤压缺陷。t10:t95的比例小于0.04会导致在上介电层80的顶表面上出现不希望的挤压缺陷。由于第五盖层80j和第五高介电常数介电层80i的蚀刻速率显著不同,t10:t9的比例大于0.7可能导致上介电层80的顶表面不平整和后续工艺问题。

142.在一些实施例中,第六高介电常数介电层80k形成为3纳米至12纳米的第十一厚度t11,其可以有益于沉积具有相对均一的膜特性和质量的第六高介电常数介电层80k(例如,均一地非晶态),而不形成挤压缺陷。将第六高介电常数介电层80k形成为小于3纳米的厚度可能是不利的,因为在随后的退火工艺中导致第六高介电常数介电层80k的结晶不充分(参考以下图14a至图14e)。将第六高介电常数介电层80k形成为大于12纳米的厚度可能是不利的,导致来自第六高介电常数介电层80k的材料的局部裸片成长的挤压缺陷。

143.根据一些实施例,图13f接续图8f,示出的密集区500的区域,其具有四个半导体鳍片62以及设置在它们之间的三个sti区72。交替的高介电常数介电层80a、80c、80e、80g、80i和80k以及盖层80b、80d、80f、80h和80j形成在四个半导体鳍片62上方。然而,可以形成任何合适数量的交替的高介电常数介电层和盖层。在一些实施例中,第一盖层80b在顶部纳米结构66的顶表面下方延伸。在一些实施例中,盖层80b、80d、80f、80h和80j以及顶部高介电常数介电层,例如第六高介电常数介电层80k在衬层78a和填充材料78b的剩余部分上方具有凹的上表面。

144.在图14a至图14e中,应用去除工艺以去除上介电层80、牺牲间隔物76和纳米结构66上方的掩模58(若存在)的多余材料。在一些实施例中,可以利用平坦化工艺,例如化学机械研磨(cmp)、回蚀工艺、其组合等。上介电层80的交替高介电常数介电层和盖层可以增加上介电层80的膜均一性,其可以改善对cmp研磨速率的控制。平坦化工艺露出掩模58或纳米结构64、66,使得在平坦化工艺完成后,掩模58或纳米结构64、66、牺牲间隔物76和上介电层80的各别顶表面共平面(在工艺变化内)。在所示实施例中,在平坦化工艺之后保留掩模58。在另一实施例中,也可以通过平坦化工艺去除部分或全部的掩模58。上介电层80在平坦化时具有留在半导体鳍片62和纳米结构64、66之间的区域中的部分(因此与衬层78a和填充材料78b的剩余部分一起形成绝缘鳍片82)。在一些实施例中,平坦化将上介电层80、牺牲间隔物76和掩模58的多余材料去除至21纳米至23纳米的深度。平坦化可以执行到足够的深度,从而去除稀疏区600的上介电层80中的空隙83及/或缝隙81。

145.在一些实施例中,上介电层80在平坦化后具有24纳米至26纳米的高度h1,这有益于在随后去除掩模58期间保护绝缘鳍片82的衬层78a和填充材料78b(参考以下图21a至图21b),并且用于去除可能存在于平坦化高度上方的上介电层80中的空隙83。高度小于24纳米的上介电层80可能导致衬层78a和填充材料78b的蚀刻,其可能允许随后形成的源极/漏极区(参考以下图18a和图18c)不期望地合并。由于开口129的不完全填充产生的空隙83(参

考以上图13a至图13e)保留在平坦化高度以下的上介电层80中,高度大于26纳米的上介电层80会导致上介电层80的顶表面不平整。

146.在一些实施例中,在上介电层80平坦化之后执行退火以改善上介电层80的特性。例如,在上介电层80的高介电常数介电层包括氧化铪的实施例中,退火将非晶态氧化铪结晶成为结晶氧化铪。上介电层80的结晶氧化铪可以在随后去除掩模58期间保护衬层78a和填充材料78b(参考以下图21a至图21b)。在一些实施例中,在700℃至1000℃的温度下执行退火。

147.在掩模58保留在纳米结构64、66上的实施例中,去除工艺可以露出掩模58或去除掩模58。此外,在一些实施例中,在去除工艺之后,通过执行单独的工艺去除掩模58。可以执行任何可接受的蚀刻工艺,例如干式蚀刻、湿式蚀刻等或其组合,以去除掩模58。蚀刻可以是各向异性。在去除掩模58的一些实施例中,去除工艺也可以(或可以不)凹蚀牺牲间隔物76。

148.图15a至图25f示出在制造实施例装置和部件的各种额外步骤。出于说明目的,图15b接续图14c,示出稀疏区600。大抵相似的工艺和材料可用于密集区500,以较大距离分开半导体鳍片62和纳米结构64、66。

149.在图15a至图15c中,在绝缘鳍片82、牺牲间隔物76和掩模58(若存在)或纳米结构64、66上形成虚设栅极层84。虚设栅极层84可以被沉积之后平坦化,例如通过cmp。虚设栅极层84可以由导电或非导电材料形成,例如非晶硅、多晶硅(polysilicon)、多晶硅锗(poly-sige)、金属、金属氮化物、金属硅化物、金属氧化物等,其可以通过物理气相沉积(pvd)、cvd等沉积。虚设栅极层84也可以由半导体材料(例如选自基板50的候选半导体材料中的一种)形成,其可以通过工艺,例如气相外延(vpe)或分子束外延(mbe)成长,通过工艺,例如化学气相沉积(cvd)或原子层沉积(ald)等沉积。虚设栅极层84可以由对绝缘材料(例如绝缘鳍片82)的蚀刻具有高蚀刻选择性的材料形成。掩模层86可以沉积在虚设栅极层84上方。掩模层86可以由介电材料,例如氮化硅、氮氧化硅等形成。在此示例中,跨越n型区50n和p型区50p形成单一虚设栅极层84和单一掩模层86。

150.在图16a至图16c中,使用可接受的光刻和蚀刻技术图案化掩模层86以形成掩模96。然后通过任何可接受的蚀刻技术将掩模96的图案转移到虚设栅极层84以形成虚设栅极94。虚设栅极94覆盖纳米结构64、66的顶表面,纳米结构64、66将在后续工艺中露出以形成通道区。掩模96的图案可以用于实体地(physically)分离相邻的虚设栅极94。虚设栅极94还可以具有与半导体鳍片62的纵向(lengthwise direction)大抵垂直(在工艺变化内)的纵向。可以在图案化之后可选地(optionally)去除掩模96,例如通过任何可接受的蚀刻技术。

151.牺牲间隔物76和虚设栅极94共同沿着纳米结构66的部分延伸,其部分将被图案化以形成通道区68。随后形成的栅极结构将替换牺牲间隔物76和虚设栅极94。在牺牲间隔物76上方形成虚设栅极94允许随后形成的栅极结构具有更大的高度。

152.如上所述,虚设栅极94可以由半导体材料形成。在此类实施例中,纳米结构64、牺牲间隔物76和虚设栅极94各自由半导体材料形成。在一些实施例中,纳米结构64和牺牲间隔物76由第一半导体材料(例如,硅锗)形成,并且虚设栅极94由第二半导体材料(例如,硅)形成,使得在替换栅极工艺期间,可以在第一蚀刻步骤中去除虚设栅极94,并且可以在第二

蚀刻步骤中一起去除纳米结构64和牺牲间隔物76。当纳米结构64和牺牲间隔物76由硅锗形成时,纳米结构64和牺牲间隔物76可以具有相似的锗浓度,纳米结构64可以具有比牺牲间隔物76更大的锗浓度,或者牺牲间隔物76可以比纳米结构64具有更大的锗浓度。在一些实施例中,纳米结构64由第一半导体材料(例如,硅锗)形成,并且牺牲间隔物76和虚设栅极94由第二半导体材料(例如,硅)形成,使得在替换栅极工艺期间,可以在第一蚀刻步骤中一起去除牺牲间隔物76和虚设栅极94,并且可以在第二蚀刻步骤中去除纳米结构64。

153.此外,在掩模58(若存在)或纳米结构64、66上方以及在掩模96(若存在)和虚设栅极94露出的侧壁上形成栅极间隔物98。可以通过顺应地沉积一种或多种介电材料,之后蚀刻介电材料以形成栅极间隔物98。可接受的介电材料可包括氧化硅、氮化硅、氮氧化硅、碳氮氧化硅等,其可以通过顺应性沉积工艺形成,例如化学气相沉积(cvd)、等离子体辅助化学气相沉积(pecvd)、原子层沉积(ald)、等离子体辅助原子层沉积(plasma-enhanced ald,peald)等。可以使用通过任何可接受的工艺形成的其他绝缘材料。可以执行任何可接受的蚀刻工艺,例如干式蚀刻、湿式蚀刻等或其组合,以图案化介电材料。蚀刻可以是各向异性。介电材料在蚀刻时具有留在虚设栅极94的侧壁上的部分(从而形成栅极间隔物98)。在蚀刻之后,栅极间隔物98可以具有弯曲的侧壁或可以具有笔直的侧壁。

154.此外,可以执行用于轻掺杂的源极/漏极(lightly doped regions,ldd)区(未单独示出)的注入。在具有不同装置类型的实施例中,相似于上述对于阱的注入,可以在n型区50n上方形成掩模(未单独示出),例如光刻胶,同时露出p型区50p,并且可以将合适类型(例如,p型)的杂质注入到p型区50p中露出的半导体鳍片62及/或纳米结构64、66中。之后可以去除掩模。随后,可以在p型区50p上方形成掩模(未单独示出),例如光刻胶,同时露出n型区50n,并且可以将合适类型(例如,n型)的杂质注入到n型区50n中露出的半导体鳍片62及/或纳米结构64、66中。之后可以去除掩模。n型杂质可以是先前讨论的任何n型杂质,并且p型杂质可以是先前讨论的任何p型杂质。在注入期间,通道区68保持被虚设栅极94覆盖,使得通道区68保持大抵没有注入以形成ldd区的杂质。轻掺杂的源极/漏极区可以具有约10

15

cm-3

至约10

19

cm-3

的杂质浓度。退火可用于修复注入损坏并活化注入的杂质。

155.应注意的是,上述公开描述形成间隔物和ldd区的工艺。可以使用其他工艺和顺序。例如,可以使用更少或额外的间隔物,可以使用不同的步骤顺序,可以形成及移除额外的间隔物及/或等相似步骤。此外,可以使用不同的结构和步骤来形成n型和p型装置。

156.在图17a至图17c中,源极/漏极凹口104形成在掩模58(若存在)、纳米结构64、66和牺牲间隔物76中。在所示实施例中,源极/漏极凹口104延伸穿过纳米结构64 66并至半导体鳍片62之中。源极/漏极凹口104也可以延伸到基板50中。在各种实施例中,源极/漏极凹口104可以在不蚀刻基板50的情况下延伸到基板50的顶表面;蚀刻半导体鳍片62,使得源极/漏极凹口104的底表面位于sti区72的顶表面下方;或相似。可以通过使用各向异性蚀刻工艺,例如rie、nbe等,蚀刻纳米结构64、66和牺牲间隔物76以形成源极/漏极凹口104。在用于形成源极/漏极凹口104的蚀刻工艺期间,栅极间隔物98和虚设栅极94共同遮蔽部分半导体鳍片62及/或纳米结构64、66。可以使用单一蚀刻工艺蚀刻每个纳米结构64、66,或者可以使用多个蚀刻工艺蚀刻每个纳米结构64、66。在源极/漏极凹口104达到期望的深度之后,可以使用定时蚀刻工艺停止对源极/漏极凹口104的蚀刻。在一些实施例中,在源极/漏极凹口104的形成期间也可以蚀刻与绝缘鳍片82相邻的sti区72的部分。

157.可选地,内间隔物106形成在掩模58(若存在)和纳米结构64的剩余部分的侧壁上,例如,由源极/漏极凹口104露出的侧壁。如随后将更详细地描述,随后将在源极/漏极凹口104中形成源极/漏极区,并且随后将纳米结构64替换为相应的栅极结构。内间隔物106作为随后形成的源极/漏极区和随后形成的栅极结构之间的隔离部件。此外,内间隔物106可以用于大抵防止随后形成的源极/漏极区被随后的蚀刻工艺损坏,例如随后用于去除纳米结构64的蚀刻工艺。

158.作为形成内间隔物106的示例,源极/漏极凹口104可以横向扩展。详细而言,源极/漏极凹口104露出的纳米结构64的部分侧壁可以被凹蚀。尽管纳米结构64的侧壁被示为笔直的(straight),然而侧壁可以是凹的或凸的。侧壁可以通过任何可接受的蚀刻工艺凹蚀,例如对纳米结构64具有选择性的工艺(例如,以比蚀刻纳米结构66的材料更快的速率选择性地蚀刻纳米结构64的材料)。蚀刻可以为各向同性。例如,当纳米结构66由硅形成,并且纳米结构64由硅锗形成时,蚀刻工艺可以是湿式蚀刻,其使用四甲基氢氧化铵(tetramethylammonium hydroxide,tmah)、氢氧化铵(nh4oh)等。在另一实施例中,蚀刻工艺可以是干式蚀刻,其使用氟基气体,例如氟化氢(hf)气体。在一些实施例中,可以连续执行相同的蚀刻工艺以形成源极/漏极凹口104及凹蚀纳米结构64的侧壁。之后在纳米结构64凹陷的侧壁上形成内间隔物106。可以通过顺应地形成绝缘材料,并随后蚀刻绝缘材料以形成内间隔物106。绝缘材料可以是氮化硅或氮氧化硅,但可以使用任何合适的材料,例如低介电常数介电材料。绝缘材料可以通过顺应性沉积工艺,例如ald、cvd等沉积。绝缘材料的蚀刻可以是各向异性。例如,蚀刻工艺可以是干式蚀刻,例如rie、nbe等。尽管内间隔物106的外侧壁被示为与栅极间隔物98的侧壁齐平(flush),然而内间隔物106的外侧壁可以延伸超过栅极间隔物98的侧壁或从栅极间隔件98的侧壁凹陷。易言之,内间隔物106可以部分填充、完全填充或过度填充侧壁凹口。此外,虽然内间隔物106的侧壁被示为是笔直的,然而内间隔物106的侧壁可以是凹的或凸的。掩模58(若存在)的侧壁的部分也可以被凹蚀,并且内间隔物106也可以形成在掩模58凹陷的侧壁上。

159.在图18a至图18c中,外延源极/漏极区108形成在源极/漏极凹口104中。在源极/漏极凹口104中形成外延源极/漏极区108,使得每个虚设栅极94(以及相应的通道区68)设置在外延源极/漏极区108的各别相邻对之间。在一些实施例中,栅极间隔物98和内间隔物106用于将外延源极/漏极区108分别与虚设栅极94和纳米结构64分开适当的横向距离,使得外延源极/漏极区108不会与所得的纳米fets的随后形成的栅极产生短路。可以选择外延源极/漏极区108的材料以对各别通道区68施加应力,从而提高性能。

160.n型区50n中的外延源极/漏极区108可以通过遮蔽p型区50p形成。之后,在n型区50n中的源极/漏极凹口104中外延成长在n型区50n中的外延源极/漏极区108。外延源极/漏极区108可以包括任何适合于n型装置的可接受的材料。例如,如果纳米结构66是硅,则在n型区50n中的外延源极/漏极区108可以包括对通道区68施加拉伸应变的材料,例如硅、碳化硅、磷掺杂的碳化硅、磷化硅等。在n型区50n中的外延源极/漏极区108可以被称为“n型源极/漏极区”。在n型区50n中的外延源极/漏极区108可以具有表面,其表面从半导体鳍片62和纳米结构64、66的相应表面升高,并且可以具有刻面(facets)。

161.p型区50p中的外延源极/漏极区108可以通过遮蔽n型区50n形成。之后,在p型区50p中的源极/漏极凹口104中外延成长在p型区50p中的外延源极/漏极区108。外延源极/漏

极区108可以包括任何适合于p型装置的可接受的材料。例如,如果纳米结构66是硅,则在p型区50p中的外延源极/漏极区108可以包括对通道区68施加压缩应变的材料,例如硅锗、硼掺杂的硅锗、锗、锗锡等。在p型区50p中的外延源极/漏极区108可以被称为“p型源极/漏极区”。在p型区50p中的外延源极/漏极区108可以具有表面,其表面从半导体鳍片62和纳米结构64、66的相应表面升高,并且可以具有刻面。

162.外延源极/漏极区108、纳米结构64、66及/或半导体鳍片62可以注入掺质以形成源极/漏极区,与先前所讨论用于形成轻掺杂源极/漏极区并随后进行退火的工艺相似。源极/漏极区的杂质浓度可以在大约10

19

cm-3

至大约10

21

cm-3

之间。用于源极/漏极区的n型及/或p型杂质可以是先前讨论的任何杂质。在一些实施例中,外延源极/漏极区108可以在成长期间被原位掺杂。

163.外延源极/漏极区108可以包括一个或多个半导体材料层。例如,外延源极/漏极区108可以各自包括衬层108a、主层108b和完成层108c(或一般来说,第一半导体材料层、第二半导体材料层和第三半导体材料层)。可以将任何数量的半导体材料层用于外延源极/漏极区108。衬层108a、主层108b和完成层108c可以各自由不同的半导体材料形成,并且可以被掺杂至不同的杂质浓度。在一些实施例中,衬层108a的杂质浓度可以小于主层108b的杂质浓度,且完成层108c的杂质浓度可以大于衬层108a的杂质浓度并小于主层108b的杂质浓度。在外延源极/漏极区包括三个半导体材料层的实施例中,可以在源极/漏极凹口104中成长衬层108a,可以在衬层108a上成长主层108b,并且可以在主层108b上成长完成层108c。

164.作为用于形成外延源极/漏极区108的外延工艺的结果,外延源极/漏极区的上表面具有横向向外扩展超过半导体鳍片62和纳米结构64、66的侧壁的刻面。然而,绝缘鳍片82阻止横向外延成长。因此,如图18c所示,在外延工艺完成后,相邻的外延源极/漏极区108保持分离。外延源极/漏极区108接触绝缘鳍片82的侧壁。在所示的实施例中,外延源极/漏极区108成长使得外延源极/漏极区108的上表面设置在绝缘鳍片82的顶表面之下。在各种实施例中,外延源极/漏极区108的上表面设置在绝缘鳍片82的顶表面之上;外延源极/漏极区108的上表面具有设置在绝缘鳍片82的顶表面之上和之下的部分;或相似。

165.在图19a至图19c中,在外延源极/漏极区108、栅极间隔物98、掩模96(若存在)或虚设栅极94上方沉积第一层间电介质(inter-layer dielectric,ild)114。第一ild 114可以由介电材料形成,并且可以通过任何合适的方法,例如化学气相沉积、等离子体辅助化学气相沉积(pecvd)或流动式化学气相沉积(fcvd)等沉积。可接受的介电材料可以包括磷硅酸盐玻璃(phosphosilicate glass,psg)、硼硅酸盐玻璃(borosilicate glass,bsg)、掺硼磷硅酸盐玻璃(boron-doped phosphosilicate glass,bpsg)、未掺杂硅酸盐玻璃(undoped silicate glass,usg)等。可以使用通过任何可接受的工艺形成的其他绝缘材料。

166.在一些实施例中,接触蚀刻停止层(contact etch stop layer,cesl)112设置在第一ild 114与外延源极/漏极区108、栅极间隔物98、以及掩模96(若存在)或虚设栅极94之间。cesl 112可以由介电材料,例如氮化硅、氧化硅、氮氧化硅等形成,其对第一ild 114的蚀刻具有高蚀刻选择性。cesl 112可以通过任何合适的方法形成,例如cvd、ald等。

167.在图20a至图20c中,可以执行去除工艺以使第一ild 114的顶表面与掩模96(若存在)或虚设栅极94的顶表面齐平。在一些实施例中,可以利用平坦化工艺,例如化学机械研磨(cmp)、回蚀工艺、其组合等。平坦化工艺也可以去除虚设栅极94上的掩模96,以及沿着掩

模96侧壁的栅极间隔物98的部分。在平坦化工艺之后,栅极间隔物98、第一ild 114、cesl 112和掩模96(若存在)或虚设栅极94的顶表面共平面(在工艺变化内)。因此,虚设栅极94的顶表面通过第一ild 114露出。在所示实施例中,掩模96保留,并且平坦化工艺使第一ild 114的顶表面与掩模96的顶表面齐平。

168.在图21a至图21c中,在蚀刻工艺中去除掩模96(若存在)和虚设栅极94,从而形成凹口116。在一些实施例中,通过各向异性干式蚀刻工艺去除虚设栅极94。例如,蚀刻工艺可以包括使用反应气体的干式蚀刻工艺,其反应气体选择性地蚀刻虚设栅极94的速率快于蚀刻第一ild 114的速率或栅极间隔物98的速率。每个凹口116露出及/或覆盖通道区68的部分。纳米结构66作为通道区68的部分设置在外延源极/漏极区108的相邻对之间。

169.之后去除纳米结构64的剩余部分以扩大凹口116,从而在纳米结构66之间的区域中形成开口118。牺牲间隔物76的剩余部分也被去除以扩大凹口116,从而在半导体鳍片62和绝缘鳍片82之间的区域中形成开口120。纳米结构64和牺牲间隔物76的剩余部分可以通过任何可接受的蚀刻工艺去除,其以比蚀刻纳米结构66的材料更快的速率选择性地蚀刻纳米结构64和牺牲间隔物76的材料。蚀刻可以为各向同性。例如,当纳米结构64和牺牲间隔物76由硅锗形成,并且纳米结构66由硅形成时,蚀刻工艺可以是使用四甲基氢氧化铵(tmah)、氢氧化铵(nh4oh)等的湿式蚀刻。也可以去除掩模58(若存在)。在一些实施例中,执行修整工艺(未单独示出)以减小纳米结构66露出部分的厚度。

170.在图22a至图22c中,在凹口116中形成栅极介电层124。在栅极介电层124上形成栅极电极层126。栅极介电层124和栅极电极层126是用于替换栅极的膜层,并且各自包绕纳米结构66的所有(例如,四个)侧面。因此,栅极介电层124和栅极电极层126形成在开口118和开口120中(参考图21a和图21c)。

171.栅极介电层124设置在半导体鳍片62的侧壁及/或顶表面上;在纳米结构66的顶表面、侧壁和底表面上;在与外延源极/漏极区108相邻的内间隔物106的侧壁上以及在内间隔物106的顶表面上的栅极间隔物98的侧壁上;并且在绝缘鳍片82的顶表面和侧壁上。栅极介电层124也可以形成在第一ild 114和栅极间隔物98的顶表面上。栅极介电层124可以包括氧化物,例如氧化硅或金属氧化物、硅酸盐,例如金属硅酸盐、其组合、其多层等。栅极介电层124可以包括高介电常数介电材料(例如,介电常数值大于约7.0的介电材料),例如铪、铝、锆、镧、锰、钡、钛、铅及其组合的金属氧化物或硅酸盐。尽管图22a至图22c示出单层的栅极介电层124,然而栅极介电层124可以包括任意数量的界面层和任意数量的主层。

172.栅极电极层126可以包括含金属材料,例如氮化钛、氧化钛、钨、钴、钌、铝、其组合、其多层等。尽管图22a至图22c示出单层的栅极电极层126,然而栅极电极层126可以包括任意数量的功函数调整层、任意数量的阻挡层、任意数量的胶(glue)层和填充材料。

173.可以同时在n型区50n和p型区50p中形成栅极介电层124,使得每个区域中的栅极介电层124由相同的材料形成,并且可以同时形成栅极电极层126,使得每个区域中的栅极电极层126由相同的材料形成。在一些实施例中,每个区域中的栅极介电层124可以通过不同的工艺形成,使得栅极介电层124可以是不同的材料及/或具有不同数量的膜层,及/或每个区域中的栅极电极层126可以通过不同的工艺形成,使得栅极电极层126可以是不同的材料及/或具有不同数量的膜层。在使用不同的工艺时,可以使用各种掩模步骤以遮蔽和露出适当的区域。

174.在图23a至图23c中,执行去除工艺以去除栅极介电层124和栅极电极层126的材料的多余部分,其多余部分位于第一ild 114和栅极间隔物98的顶表面上方,从而形成栅极结构130。在一些实施例中,可以利用平坦化工艺,例如化学机械研磨(cmp)、回蚀工艺、其组合等。栅极介电层124在平坦化时具有留在凹口116中的部分(从而形成栅极结构130的栅极电介质)。栅极电极层126在平坦化时具有留在凹口116中的部分(从而形成栅极结构130的栅极电极)。栅极间隔物98、cesl 112、第一ild 114及栅极结构130的顶表面共平面(在工艺变化内)。栅极结构130为所得纳米fets的替换栅极,并且可以被称为“金属栅极”。每个栅极结构130沿着纳米结构66的通道区68的顶表面、侧壁和底表面延伸。

175.栅极结构130填充先前由纳米结构64、牺牲间隔物76和虚设栅极94占据的区域。在栅极结构形成之后,栅极结构130具有与牺牲间隔物76相同的轮廓形状。

176.在一些实施例中,隔离区132形成为延伸穿过一些栅极结构130。形成隔离区132以将栅极结构130划分(或“切割”)为多个栅极结构130。隔离区132可以由介电材料,例如氮化硅、氧化硅、氮氧化硅等形成,其可以通过沉积工艺,例如cvd、ald等形成。作为形成隔离区132的示例,可以在期望的栅极结构130中图案化开口。可以执行任何可接受的蚀刻工艺,例如干式蚀刻、湿式蚀刻等或其组合,以进行图案化开口。蚀刻可以为各向异性。一层或多层介电材料可以沉积在开口中。可以执行去除工艺以去除介电材料的多余部分,其多余部分位于栅极结构130的顶表面上方,从而形成隔离区132。

177.在图24a至图24c中,第二ild 136沉积在栅极间隔物98、cesl 112、第一ild 114和栅极结构130上方。在一些实施例中,第二ild 136是通过流动式cvd形成的可流动膜。在一些实施例中,第二ild 136由介电材料,例如psg、bsg、bpsg、usg等形成,其可以通过任何合适的方法,例如cvd、pecvd等沉积。

178.在一些实施例中,蚀刻停止层(etch stop layer,esl)134形成在第二ild 136和栅极间隔物98、cesl 112、第一ild 114和栅极结构130之间。esl 134可以包括介电材料,例如氮化硅、氧化硅、氮氧化硅等,具有对于第二ild 136的蚀刻的高蚀刻选择性。

179.在图25a至图25c中,形成栅极接触件142和源极/漏极接触件144以分别接触栅极结构130和外延源极/漏极区108。栅极接触件142实体地(physically)及电性地耦合至栅极结构130。源极/漏极接触件144实体地及电性地耦合至外延源极/漏极区108。

180.作为形成栅极接触件142和源极/漏极接触件144的示例,形成用于栅极接触件142的开口,其穿过第二ild 136和esl 134,形成用于源极/漏极接触件144的开口,其穿过第二ild 136、esl 134、第一ild 114和cesl 112。可以使用可接受的光刻和蚀刻技术形成开口。在开口中形成衬层(未单独示出),例如扩散阻挡层、粘着层等,以及导电材料。衬层可以包括钛、氮化钛、钽、氮化钽等。导电材料可以是铜、铜合金、银、金、钨、钴、铝、镍等。可以执行平坦化工艺,例如cmp以从第二ild 136的表面去除多余的材料。剩余的衬层和导电材料在开口中形成栅极接触件142和源极/漏极接触件144。栅极接触件142和源极/漏极接触件144可以在不同的工艺中形成,或者可以在相同的工艺中形成。虽然显示为形成在相同的剖面中,但是应当理解,栅极接触件142和源极/漏极接触件144可以各自形成在不同的剖面中,期可以避免接触件的短路。

181.可选地,在外延源极/漏极区108和源极/漏极接触件144之间的界面处形成金属-半导体合金区146。金属-半导体合金区146可以是由金属硅化物(例如,硅化钛、硅化钴、硅

化镍等)形成的硅化物区;由金属锗化物(例如,锗化钛、锗化钴、锗化镍等)形成的锗化区;由金属硅化物和金属锗化物形成的硅锗化物区等。通过在源极/漏极接触件144的开口中沉积金属然后执行热退火工艺,可以在源极/漏极接触件144的材料之前形成金属-半导体合金区146。金属可以是任何能够与外延源极/漏极区108的半导体材料(例如硅、硅锗、锗等)反应形成低电阻金属半导体合金的金属,如镍、钴、钛、钽、铂、钨、其他贵金属、其他耐火(refractory)金属、稀土金属或其合金。金属可以通过沉积工艺,例如ald、cvd、pvd等沉积。在热退火工艺之后,可以执行清洁工艺,例如湿式清洁,以从源极/漏极接触件144的开口,例如从金属-半导体合金区146的表面去除任何残留金属。之后可以在金属-半导体合金区146上形成源极/漏极接触件144的材料。

182.根据一些实施例,图25d接续图13f,示出密集区500的区域,其具有四个半导体鳍片62以及设置在它们之间的三个绝缘鳍片82。图25d所示的结构可以使用与图14a至图25c中描述的相似方法和材料从图13f所示的结构形成。在一些实施例中,隔离区132延伸穿过栅极结构130以实体接触绝缘鳍片82的上介电层80的顶表面,以电性隔离相邻的栅极结构130。

183.图25e示出如图25d所示的密集区500中的区域1004的视图,并且图25f示出如图25b所示的稀疏区600中的区域1002的视图。密集区500中的隔离区132落在绝缘鳍片82的上介电层80的顶表面上。在一些实施例中,隔离区132覆盖盖层80b和高介电常数介电层80c的顶表面。根据一些实施例,如图25e所示,密集区500中的上介电层80包括高介电常数介电层80a和80c以及盖层80b。然而,密集区500中的上介电层80可以包括任何合适数量的顺序沉积、交替的高介电常数介电层和盖层,例如,3层高介电常数介电层和2层盖层,4层高介电常数介电层和3层盖层,或5层高介电常数介电层和4层盖层。根据一些实施例,如图25f所示,稀疏区600中的上介电层80包括:高介电常数介电层80a、80c、80e和80g;以及盖层80b、80d和80f。然而,稀疏区600中的上介电层80可以包括任何合适数量的顺序沉积、交替的高介电常数介电层和盖层,例如,3层高介电常数介电层和2层盖层,5层高介电常数介电层和4层盖层,6层高介电常数介电层和5层盖层,或10层高介电常数介电层和9层盖层。

184.本公开的一些实施例可以具有一些益处。例如,在一些实施例中,在纳米结构的堆叠之间形成的绝缘鳍片可以减少源极/漏极区不期望的合并。由交替的高介电常数介电层和盖层形成的绝缘鳍片的顶部可以减少由高介电常数部分顶表面上的局部裸片成长引起的挤压缺陷,其可以通过盖层减少。交替的高介电常数介电层和盖层可以提供对膜质量和cmp研磨速率更好的控制能力。

185.根据一些实施例,本公开提供一种半导体装置,包括:第一通道区以及第二通道区,第一通道区以及第二通道区在基板上方;以及第一绝缘鳍片,在基板上,第一绝缘鳍片插入(interposed)在第一通道区与第二通道区之间,第一绝缘鳍片包括:下部,包括填充材料;以及上部,包括:第一介电层,在下部上,第一介电层为第一介电材料;第一盖层,在第一介电层上,第一盖层为第二介电材料,第二介电材料不同于第一介电材料;以及第二介电层,在第一盖层上,第二介电层为第一介电材料。

186.在一些实施例中,第一介电材料为氧化铪。

187.在一些实施例中,第二介电材料为氧化硅。

188.在一些实施例中,第一盖层覆盖第一介电层的内侧壁。

189.在一些实施例中,第二介电层插入在第一介电层的侧壁部分之间。

190.在一些实施例中,第一盖层覆盖第二介电层的外侧壁以及底表面。

191.在一些实施例中,第一介电层的顶表面与第一盖层的顶表面以及第二介电层的顶表面共平面。

192.在一些实施例中,第一通道区包括纳米结构的第一堆叠,并且第二通道区包括纳米结构的第二堆叠。

193.在一些实施例中,第一绝缘鳍片的下部还包括衬层,衬层覆盖填充材料的侧壁以及底表面。

194.根据另一些实施例,本公开提供一种半导体装置,包括:第一源极/漏极区,在第一半导体鳍片上;第二源极/漏极区,在第二半导体鳍片上;以及第一绝缘鳍片,在第一源极/漏极区以及第二源极/漏极区之间,第一绝缘鳍片包括:底部,底部包括衬层以及填充材料,填充材料插入在衬层的侧壁之间;以及顶部,在底部上,顶部包括:第一高介电常数介电层;第二高介电常数介电层,在第一高介电常数介电层的内侧壁之间;以及第一盖层,在第一高介电常数介电层以及第二高介电常数介电层之间。

195.在另一些实施例中,第一绝缘鳍片的顶部还包括:第二盖层,在第二高介电常数介电层上;以及第三高介电常数介电层,在第二盖层上。

196.在另一些实施例中,第一高介电常数介电层的顶表面、第二高介电常数介电层的顶表面、第三高介电常数介电层的顶表面、第一盖层的顶表面以及第二盖层的顶表面共平面。

197.在另一些实施例中,第一高介电常数介电层具有3纳米至12纳米的厚度。

198.在另一些实施例中,第一盖层具有0.5纳米至2纳米的厚度。

199.在另一些实施例中,还包括纳米结构的第一堆叠,在第一半导体鳍片上方,以及纳米结构的第二堆叠,在第二半导体鳍片上方,第一绝缘鳍片插入在纳米结构的第一堆叠以及纳米结构的第二堆叠之间。

200.根据又一些实施例,本公开提供一种半导体装置的形成方法,包括:在第一半导体鳍片以及第二半导体鳍片之间形成衬层;在衬层上方形成填充材料;凹蚀衬层以及填充材料,以在衬层以及填充材料上方定义第一开口;在第一开口的侧壁上以及底表面上形成第一高介电常数介电层;在第一高介电常数介电层上形成第一盖层;以及在第一盖层上形成第二高介电常数介电层。

201.在又一些实施例中,还包括去除第一高介电常数介电层的上部、第一盖层的上部以及第二高介电常数介电层的上部。

202.在又一些实施例中,第一高介电常数介电层的材料以大抵(substantially)非结晶态沉积。

203.在又一些实施例中,还包括以退火使第一高介电常数介电层结晶。

204.在又一些实施例中,第一高介电常数介电层包括铪,并且第一盖层包括硅。

205.以上概述数个实施例的特征,以使本发明所属技术领域中技术人员可以更加理解本发明实施例的观点。本发明所属技术领域中技术人员应理解,可轻易地以本发明实施例为基础,设计或修改其他工艺和结构,以达到与在此介绍的实施例相同的目的及/或优势。在本发明所属技术领域中技术人员也应理解,此类等效的结构并无悖离本发明的精神与范

围,且可在不违背本发明的精神和范围下,做各式各样的改变、取代和替换。因此,本发明的保护范围当视随附的权利要求所界定为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1