一种半导体芯片共晶烧结的方法与流程

1.本发明属于本发明属于半导体芯片装配领域,具体涉及一种半导体芯片共晶烧结的方法。

背景技术:

2.共晶焊接是在大功率器件中常用的一种工艺方法,但共晶焊接容易在芯片背面产生空洞,进而易造成芯片热失效,原因在于:焊片与芯片和热层之间均有空隙,与热层接触的部位,焊料会先熔化,在表面张力的作用下会拉扯未熔化的焊料,将原有位置抽干,则会在芯片背面形成空洞,而由于空洞的存在,这直接使得芯片在工作过程中产生的热量无法及时通过热层将该热量传导到空气中,特别是大功率芯片或者针对开关工作时,会瞬间产生较大热量,如果无法将热量排出,芯片则会因为过热致使其失效。另外,当芯片背面形成空洞后,键合时施加在劈刀上的超声,在高频的振动下,施加一定压力,不断摩擦芯片,该高频超声压力会相对空洞边缘,以空洞边缘形成一个支点,产生一较大力矩,该力矩会大大增加支点处受到的应力,由于超声振动的作用,会不断的给支点施加一个脉冲冲击力,而芯片材料非常脆,加之作用力影响则可能使芯片内部产生隐裂,进而造成芯片性能下降,甚至损坏,基于以上原因极大降低了芯片合格率,这也使得大功率产品的微组装工艺成为制约我们发展的问题。

3.共晶焊接由于烧结温度较高,一般在280℃以上,为后续产品再加工,进入回流焊使的低温度,形成一温度梯度,可以避免半导体芯片的焊料二次熔化,保证产品的可靠性。由于共晶温度较高,常用的焊料是铅锡银焊料或金锑焊料。当使用铅锡银焊料共晶时,一般的工艺方法是采用氮氢混气烧结而成,虽然采用氮气混气保护性能较佳,但该工艺方法有诸多缺点,如烧结炉的温度不可控,焊料熔化状态不可控。还有一种方法是采用回流焊接路,但一般的回流焊接路采用氮气保护,氮气仅有物理保护作用,并无还原作用。一般的回流焊接路采用的是普通的机械泵,机械泵的能力较弱,仅能抽到几帕,无法有效的保护焊料以及芯片不被氧化。而采用氢烧结工艺炉,无法精确控制产品的升温或冷却时间,这造成芯片焊片外溢严重,外溢的焊料可能使芯片背面失去焊料,加剧了空洞的形成。

4.专利公开号cn108461380a公开了一种大面积集成电路芯片烧结空洞率的控制结构和控制方法,所述控制方法包括(1)原材料处理:先对外壳进行预烘焙处理,预烘焙温度为100~150℃,预烘焙时间为1~4小时;然后对外壳、芯片和焊料片采用等离子清洗,以去除外壳、芯片和焊料片表面氧化物及沾污物;(2)预装配:将重块、过渡片、芯片、焊料片、外壳和载具叠装在一起,得到所述控制结构;(3)合金烧结粘片:所述合金烧结粘片过程具体包括如下步骤:(a)充入保护气:将预装配的控制结构放入焊接炉内,在室温条件下抽真空,使腔体内真空度为0.1mbar~1.5mbar,再充入氮气,至腔内真空度为3mbar~20mbar;最后充入保护气体;(b)预热过程:将焊接腔体从室温加热到预热温度t1,t1=230~290℃,加热到t1过程的升温速率为20~80℃/min;(c)保温过程:加热到预热温度后保温100s以上;(d)加热过程:将腔体从预热温度t1加热到焊接温度t2,t2=310~400℃,t1加热到t2过程的升

温速率为20~80℃/min;(e)反应过程:保持焊接腔体内温度为t2,焊料片充分熔化,并与芯片背面金属、外壳背面金完成共晶反应,形成共晶体;反应过程的时间为60s~400s;(f)排气过程:先对焊接腔体进行抽真空,至腔内真空度为0.1mbar~1.5mbar后,保持30s~300s,再充入氮气,以排除共晶体中残余的气泡,减小空洞率;(g)急速冷却过程:将腔体温度从t2降到t3,t3=100~300℃;腔体温度从t2降到t3过程的降温速率为20~80℃/min;(h)缓慢冷却过程:将腔体温度从t3降低到t4,t4=室温~100℃;缓慢冷却过程的降温速率为5~60℃/min。上述步骤(3)中的步骤(a)中,所充入的保护气体为氮气和甲酸,氮气和甲酸的体积比例为10:1~2:1;但该技术方案中需要采用重块、过渡片才能使焊片平整,进而保证烧结效果,而增加重块会降低生产效率,只适合较大的集成电路芯片,芯片尺寸一般过大,不适合小尺寸芯片。增加重块还会增加挤压焊料的风险,将内部的焊料挤出后,致使焊料溢出后,芯片背面的焊料不均匀,造成空洞的产生。

5.目前,小型化、大功率固体继电器产品所用的裸芯片需采用微组装加工,并且成品率低已极大困扰大功率器件的发展脚步,因此研究一种合格率高、烧结质量优的共晶焊接工艺至关重要。

技术实现要素:

6.本发明针对现有技术的不足,提出了一种半导体芯片共晶烧结的方法。

7.具体是通过以下技术方案来实现的:

8.一种半导体芯片共晶烧结的方法,所述共晶烧结是将预成型焊片的一面通过点焊方式与热层片连接,再将芯片叠放在预成型焊片的另一面,制成装配体后,将装配体放入预热的烧结设备内,抽真空并升温至120-130℃后,以甲酸为保护剂进行共晶烧结;所述共晶烧结采用恒温烧结和升温烧结相结合方式。

9.进一步地,所述半导体芯片共晶烧结的方法,包括如下步骤:

10.1)将银基焊料经裁剪、切割制成厚度为0.025mm的预成型焊片;

11.2)将预成型焊片压平,确保预成型焊片无翘曲、无拱翘、无凹凸;

12.3)先将预成型焊片的一面通过点焊方式与热层片连接,再将芯片叠放在预成型焊片的另一面,制成装配体后,然后将装配体放入预热的烧结设备内,抽真空并升温至120-130℃后,以甲酸为保护剂进行共晶烧结;

13.4)待共晶烧结完毕后,向烧结设备充入高纯氮气进行冷却,待温度降至150℃,打开烧结设备自然冷却。

14.所述银基焊料为pb92.5sn5ag2.5。

15.所述预成型焊片的面积与芯片面积保持同大小。

16.所述烧结设备的预热温度为25℃。

17.所述步骤3)的升温至120-130℃的时间为3-5min。

18.所述甲酸的充入速率为5l/min。

19.所述共晶烧结采用恒温烧结和升温烧结。

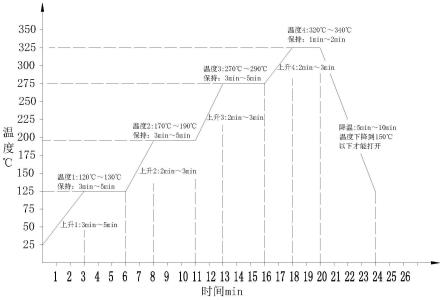

20.所述恒温烧结分为四个阶段,所述第一阶段是120-130℃保温3-5min,第二阶段是170-190℃保温3-5min,第三阶段是270-290℃保温3-5min,第四阶段是320-340℃保温1-2min。

21.所述升温烧结分为三个阶段,所述第一阶段是从120-130℃升温至170-190℃;第二阶段是从170-190℃升温至270-290℃;第三阶段是从270-290℃升温至320-340℃。

22.所述第一阶段升温烧结的时间为2-3min。

23.所述第二阶段升温烧结的时间为2-3min。

24.所述第三阶段升温烧结的时间为2-3min。

25.所述高纯氮气的充入量控制为保证在5-10min内将装配体温度从320-340℃降至150℃。

26.有益效果:

27.本发明创造通过采用pb92.5sn5ag2.5的焊料,该焊料的熔点为296℃,固相线为287℃,将其制备成预成型焊片,焊片大小与芯片面积相当,且焊片厚度采用0.025mm,通过压平工装,保证焊料的无翘曲、无拱翘、无凹凸,能与芯片完全贴紧,背面无气泡,共晶烧结时,采用甲酸作为保护剂,可以有效保护银基材料,将其氧化的银基环氧成银离子,提高焊料与芯片的浸润能力。另外,通过科学设置共晶烧结升温及恒温程序,能够在共晶烧结过程中将热量有效、均匀的传递到焊料和芯片上,使焊料能稳定熔化,不膨胀、不过流,且有利改善了焊料熔化时过渡流淌以及抽干芯片背面焊料的现象,减少空洞的形成,进而降低了空洞对焊片合格率的不利影响。

28.本发明创造通过将焊片点焊在热层上,改善了焊片在操作时易凸起、不平整而易形成气泡的情况,减少空洞形成;并且本发明创造无需采用重块等来确保焊片与芯片的充分接触,在准备成本上更低,并且降低了在共晶烧结过程中重块对焊片或芯片另一表面的不利影响。

29.本发明创造以甲酸为保护气,控制简单并起到良好的还原作用,而在传统方法中仅以氮气或惰性气体为保护剂,无法起到良好的还原作用;采用甲酸与氮气或惰性气体的混合气态为保护剂,控制难度大,并且容易造成体系不稳定,进而影响烧结质量、成品率。

30.本发明方法适用于小型、小面积半导体芯片的微组装生产。

附图说明

31.图1:本发明的共晶烧结温度控制曲线。

具体实施方式

32.下面对本发明的具体实施方式作进一步详细的说明,但本发明并不局限于这些实施方式,任何在本实施例基本精神上的改进或代替,仍属于本发明权利要求所要求保护的范围。

33.实施例1

34.一种半导体芯片共晶烧结的方法,包括如下步骤:

35.1)将银基焊料pb92.5sn5ag2.5经裁剪、切割制成与芯片面积同规格、厚度为0.025mm的预成型焊片;

36.2)将预成型焊片压平,确保预成型焊片无翘曲、无拱翘、无凹凸;

37.3)先将预成型焊片的一面通过点焊方式与热层片连接,再将裸芯片叠放在预成型焊片的另一面,制成装配体后,然后将装配体放入预热温度为25℃的烧结设备内,抽真空并

在3min内升温至120℃后,以甲酸为保护剂进行共晶烧结,所述甲酸的充入速率为5l/min;

38.4)待共晶烧结完毕后,向烧结设备充入高纯氮气,使得5min内装配体温度从320℃降至150℃,然后打开烧结设备自然冷却。

39.所述共晶烧结采用恒温烧结和升温烧结相结合的模式;所述恒温烧结分为四个阶段,所述第一阶段是120℃保温3min,第二阶段是170℃保温3min,第三阶段是270℃保温3min,第四阶段是320℃保温1min;所述升温烧结分为三个阶段,所述第一阶段是在2min内从120℃升温至170℃;第二阶段是在2min内从170℃升温至270℃;第三阶段是在2min从270℃升温至320℃。

40.将本实施例芯片采用微组装工艺制成jgx-1h10dma大功率固体继电器,加工合格品统计情况如下表:

41.型号装配数量不合格数量不合格率合格率jgx-1h10dma5024%96%

42.本实施例在同样测试条件下将传统方法制备的芯片采用微组装工艺制成jgx-1h10dma大功率固体继电器,并统计加工合格品,结果显示其合格率为40%,考虑到传统方法制备的芯片与本实施例不同点是:将保护剂甲酸替换为氮气,且焊料与热层片不采用点焊形式连接,而是直接将裸芯片、焊料、热层片由上至下按序叠放后用夹具夹紧即得装配体,其他条件同本实施例,考虑到传统方法中焊料与热层片和裸芯片之间均有孔隙,加之与热层片接触的一片焊料会先熔化,在表面张力的作用下会拉扯未熔化的焊料,将原有位置抽干并形成一个空洞,同时由于氮气不具有还原性,也会加重焊料氧化程度,因此使得合格率降低。

43.实施例2

44.一种半导体芯片共晶烧结的方法,包括如下步骤:

45.1)将银基焊料pb92.5sn5ag2.5经裁剪、切割制成与芯片面积同规格、厚度为0.025mm的预成型焊片;

46.2)将预成型焊片压平,确保预成型焊片无翘曲、无拱翘、无凹凸;

47.3)先将预成型焊片的一面通过点焊方式与热层片连接,再将裸芯片叠放在预成型焊片的另一面,制成装配体后,然后将装配体放入预热温度为25℃的烧结设备内,抽真空并在5min内升温至130℃后,以甲酸为保护剂进行共晶烧结,所述甲酸的充入速率为5l/min;

48.4)待共晶烧结完毕后,向烧结设备充入高纯氮气,使得5-10min内装配体温度从340℃降至150℃,然后打开烧结设备自然冷却。

49.所述共晶烧结采用恒温烧结和升温烧结相结合的模式;所述恒温烧结分为四个阶段,所述第一阶段是130℃保温5min,第二阶段是190℃保温5min,第三阶段是290℃保温5min,第四阶段是340℃保温2min;所述升温烧结分为三个阶段,所述第一阶段是在3min内从130℃升温至190℃;第二阶段是在3min内继续升温至290℃;第三阶段是在3min继续升温至340℃。

50.将本实施例芯片采用微组装工艺制成jzc-1h20dmc大功率固体继电器,加工合格品统计情况如下表:

51.型号装配数量不合格数量不合格率合格率jzc-1h20dmc4012.5%97.5%

52.本实施例在同样测试条件下将传统方法制备的芯片采用微组装工艺制成jzc-1h20dmc大功率固体继电器,并统计加工合格品,结果显示其合格率为15%,考虑到传统方法制备的芯片与本实施例不同点是:将保护剂甲酸替换为氮气,且焊料与热层片不采用点焊形式连接,而是直接将裸芯片、焊料、热层片由上至下按序叠放后用重块压实即得装配体,其他条件同本实施例,考虑到传统方法中焊料与热层片和裸芯片之间均有孔隙,加之与热层片接触的一片焊料会先熔化,在表面张力的作用下会拉扯未熔化的焊料,将原有位置抽干并形成一个空洞,同时由于氮气不具有还原性,也会加重焊料氧化程度,因此使得合格率降低。

53.实施例3

54.一种半导体芯片共晶烧结的方法,包括如下步骤:

55.1)将银基焊料pb92.5sn5ag2.5经裁剪、切割制成与芯片面积同规格、厚度为0.025mm的预成型焊片;

56.2)将预成型焊片压平,确保预成型焊片无翘曲、无拱翘、无凹凸;

57.3)先将预成型焊片的一面通过点焊方式与热层片连接,再将裸芯片叠放在预成型焊片的另一面,制成装配体后,然后将装配体放入预热温度为25℃的烧结设备内,抽真空并在4min内升温至125℃后,以甲酸为保护剂进行共晶烧结,所述甲酸的充入速率为5l/min;

58.4)待共晶烧结完毕后,向烧结设备充入高纯氮气,使得8min内装配体温度从330℃降至150℃,然后打开烧结设备自然冷却。

59.所述共晶烧结具体是:先125℃保温4min,然后以150s内升温180℃的速率进行升温并保温4min,再以150s内升温至280℃的速率进行升温并保温4min,最后以150s内升温至330℃的速率进行升温并保温90s。

60.将本实施例芯片采用微组装工艺制成jgx-1h10dma、jzc-1h20dmc大功率固体继电器,合格品率比传统方法效果显著。

61.实施例4

62.一种半导体芯片共晶烧结的方法,包括如下步骤:

63.1)将银基焊料pb92.5sn5ag2.5经裁剪、切割制成与芯片面积同规格、厚度为0.025mm的预成型焊片;

64.2)将预成型焊片压平,确保预成型焊片无翘曲、无拱翘、无凹凸;

65.3)先将预成型焊片的一面通过点焊方式与热层片连接,再将裸芯片叠放在预成型焊片的另一面,制成装配体后,然后将装配体放入预热温度为25℃的烧结设备内,抽真空并在5min内升温至120℃后,以甲酸为保护剂进行共晶烧结,所述甲酸的充入速率为5l/min;

66.4)待共晶烧结完毕后,向烧结设备充入高纯氮气,使得5min内装配体温度从340℃降至150℃,然后打开烧结设备自然冷却。

67.所述共晶烧结具体是:先120℃保温5min,然后以2min内升温190℃的速率进行升温并保温3min,再以3min内升温至270℃的速率进行升温并保温5min,最后以2min内升温至340℃的速率进行升温并保温1min。

68.将本实施例芯片采用微组装工艺制成jgx-1h10dma、jzc-1h20dmc大功率固体继电器,合格品率比传统方法效果显著。

69.实施例5

70.一种半导体芯片共晶烧结的方法,包括如下步骤:

71.1)将银基焊料pb92.5sn5ag2.5经裁剪、切割制成与芯片面积同规格、厚度为0.025mm的预成型焊片;

72.2)将预成型焊片压平,确保预成型焊片无翘曲、无拱翘、无凹凸;

73.3)先将预成型焊片的一面通过点焊方式与热层片连接,再将裸芯片叠放在预成型焊片的另一面,制成装配体后,然后将装配体放入预热温度为25℃的烧结设备内,抽真空并在3min内升温至130℃后,以甲酸为保护剂进行共晶烧结,所述甲酸的充入速率为5l/min;

74.4)待共晶烧结完毕后,向烧结设备充入高纯氮气,使得10min内装配体温度从330℃降至150℃,然后打开烧结设备自然冷却。

75.所述共晶烧结具体是:先130℃保温3min,然后以3min内升温170℃的速率进行升温并保温4min,再以2min内升温至290℃的速率进行升温并保温3min,最后以3min内升温至330℃的速率进行升温并保温1min。

76.将本实施例芯片采用微组装工艺制成jgx-1h10dma、jzc-1h20dmc大功率固体继电器,合格品率比传统方法效果显著。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1