具有不同工作电压的MOS晶体管的集成结构和制造方法与流程

本发明涉及半导体集成电路制造领域,特别涉及一种具有不同工作电压的mos晶体管的集成结构。本发明还涉及一种具有不同工作电压的mos晶体管的集成结构的制造方法。

背景技术:

1、如图1a至图1c所示,是现有具有不同工作电压的mos晶体管的集成结构和制造方法各步骤中的器件结构示意图;现有具有不同工作电压的mos晶体管的集成结构的制造方法包括如下步骤:

2、步骤一、如图1a所示,在半导体衬底101上的第一mos晶体管的形成区域、第二mos晶体管的形成区域和第三mos晶体管的形成区域分别形成第一栅极结构、第二栅极结构和第三栅极结构。

3、图1a中,区域1表示第一mos晶体管的形成区域;区域2表示第二mos晶体管的形成区域;区域3表示第三mos晶体管的形成区域。区域1中通常会形成多个所述第一mos晶体管,图1a中仅显示了一个所述第一mos晶体管。同样,区域2中会集成多个所述第二mos晶体管,区域3中会集成多个所述第三mos晶体管。

4、第一mos晶体管具有第一工作电压,第二mos晶体管具有第二工作电压,第三mos晶体管具有第三工作电压;所述第三工作电压大于所述第二工作电压以及所述第二工作电压大于所述第一工作电压。所述第三工作电压为高压(hv),所述第二工作电压为中压(mv),所述第一工作电压为低压(lv)。通常,将第一mos晶体管称为lv器件,将第二mos晶体管称为mv器件,将第三mos晶体管称为hv器件。lv器件通常应用于核心器件区域中如sram的存储区域中,lv器件具有工作电压降低和集成度较高的特点。mv器件则通常应用处输入输出(io)区域中。hv器件则应用于一些需要耐压的区域中。

5、所述第一栅极结构由第一栅介质层103a和第一栅极导电材料层104a叠加而成,所述第二栅极结构由第二栅介质层103b和第二栅极导电材料层104b叠加而成,所述第三栅极结构由第三栅介质层103c和第三栅极导电材料层104c叠加而成。

6、所述第二栅介质层103b的厚度大于所述第一栅介质层103a的厚度,所述第三栅介质层103c的厚度大于所述第二栅介质层103b的厚度。

7、所述第一栅介质层103a、所述第二栅介质层203b和所述第三栅介质层103c通常独立形成,以满足各自的厚度要求。

8、通常,所述第一栅极导电材料层104a、所述第二栅极导电材料层104b和所述第三栅极导电材料层104c都为多晶硅栅,且是采用多晶硅沉积加图形化刻蚀工艺同时形成。

9、步骤二、如图1a所示,在所述第一栅极结构、所述第二栅极结构和所述第三栅极结构的侧面形成第一子侧墙105。

10、通常,所述第一子侧墙105的材料包括氧化硅。直接对所述多晶硅栅进行氧化即可形成所述第一子侧墙105,由于所述第一栅极结构、所述第二栅极结构和所述第三栅极结构的所述第一子侧墙105是采用相同的工艺同时形成,仅是位置不同,故都采用标记105表示。

11、步骤三、如图1b所示,沉积第二子侧墙材料层106a。所述第二子侧墙材料层106a会覆盖在第一至第三栅极结构的顶部表面和侧面以及外部表面。

12、步骤四、如图1c所示,对所述第二子侧墙材料层106a进行全面刻蚀使所述第二子侧墙材料层106a自对准保留在所述第一栅极结构、所述第二栅极结构和所述第三栅极结构的侧面并组成第二子侧墙106。

13、由图1c所示可知,所述第一栅极结构、所述第二栅极结构和所述第三栅极结构的侧墙都是由所述第一子侧墙105和所述第二子侧墙106叠加而成。

14、通常所述侧墙的厚度需要满足核心器件区域的要求,通过降低所述侧墙的厚度能减少lv器件的尺寸,从而提高核心器件区域的集成度。在mv器件中,现有集成结构容易产生栅诱导漏极漏电(gate-induced drain leakage,gidl)。通常,mv器件的ioff需要小于10pa/μm,但是实际ioff会大于100pa/μm。而ioff主要是由gidl漏电贡献,所以,需要进一步降低mv器件的gidl漏电。

技术实现思路

1、本发明所要解决的技术问题是提供一种具有不同工作电压的mos晶体管的集成结构,能保证较低的第一工作电压的第一mos晶体管的第一侧墙的厚度较薄的条件下,单独增加中间的第二工作电压的第二mos晶体管的第二侧墙厚度,从而能减少第二mos晶体管的gidl漏电。为此,本发明还提供一种具有不同工作电压的mos晶体管的集成结构的制造方法。

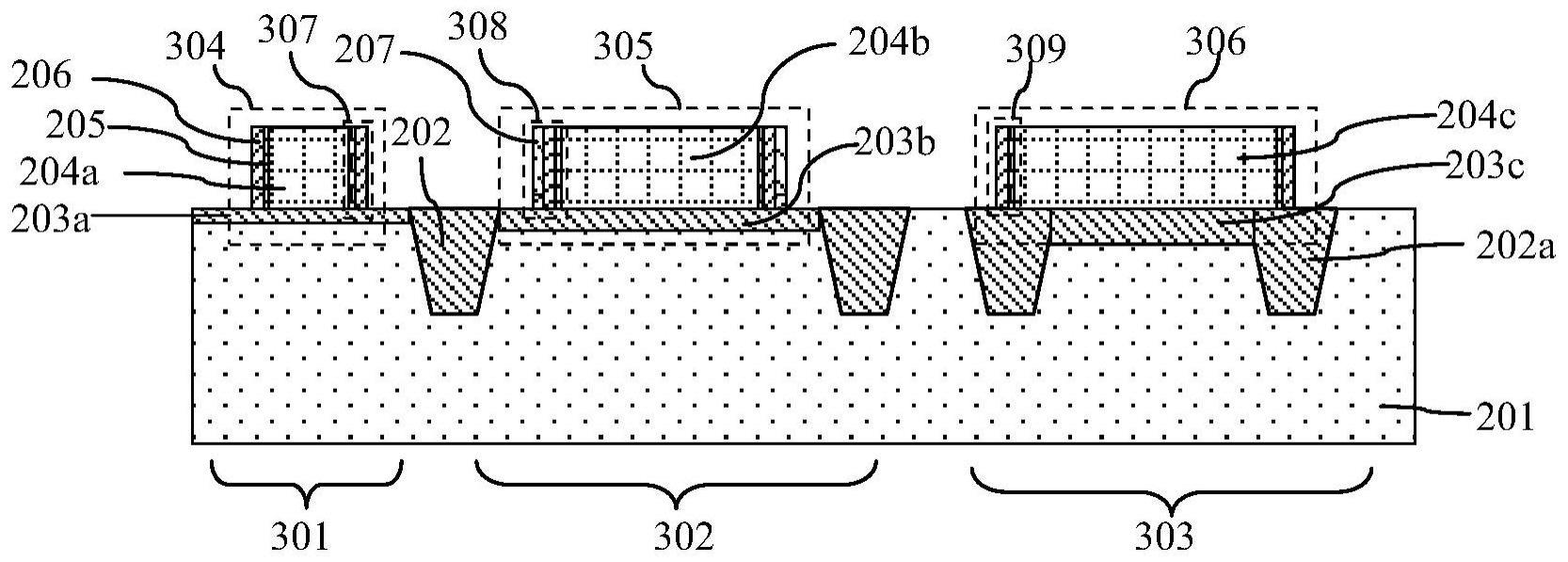

2、为解决上述技术问题,本发明提供的具有不同工作电压的mos晶体管的集成结构中,在半导体衬底上同时集成有第一工作电压的第一mos晶体管、第二工作电压的第二mos晶体管以及第三工作电压的第三mos晶体管;所述第三工作电压大于所述第二工作电压以及所述第二工作电压大于所述第一工作电压。

3、所述第一mos晶体管具有第一栅极结构,所述第二mos晶体管具有第二栅极结构,所述第三mos晶体管具有第三栅极结构。

4、所述第一栅极结构由第一栅介质层和第一栅极导电材料层叠加而成,所述第二栅极结构由第二栅介质层和第二栅极导电材料层叠加而成,所述第三栅极结构由第三栅介质层和第三栅极导电材料层叠加而成。

5、所述第二栅介质层的厚度大于所述第一栅介质层的厚度,所述第三栅介质层的厚度大于所述第二栅介质层的厚度。

6、在所述第一栅极结构的侧面自对准形成有由第一子侧墙和第二子侧墙叠加形成的第一侧墙。

7、在所述第二栅极结构的侧面自对准形成有由第一子侧墙、第二子侧墙和第三子侧墙叠加形成的第二侧墙。

8、在所述第三栅极结构的侧面自对准形成有第三侧墙,所述第三侧墙由第一子侧墙和第二子侧墙叠加而成或者由第一子侧墙、第二子侧墙和第三子侧墙叠加而成。

9、在所述第一侧墙的厚度的基础上,所述第二侧墙的厚度通过所述第三子侧墙调节,用以保证在所述第二工作电压下所述第二mos晶体管的gidl漏电满足要求,所述第二侧墙的厚度越厚,所述第二mos晶体管的gidl漏电越小。

10、进一步的改进是,所述第二mos晶体管还包括:

11、第二漂移区,形成在所述第二栅极结构两侧的所述半导体衬底中,所述第二漂移区和所述第一子侧墙的侧面自对准,所述第二漂移区还扩散延伸到所述第二栅极结构的底部。

12、第二源漏区,形成在所述第二栅极结构两侧的所述第二漂移区中,所述第二源漏区和所述第二侧墙的侧面自对准,所述第二漂移区的结深大于所述第二源漏区的结深,所述第二源漏区的掺杂浓度大于所述第二漂移区的掺杂浓度。

13、进一步的改进是,所述第二mos晶体管的gidl漏电满足要求的条件为:所述第二mos晶体管的gidl漏电小于10pa/μm。

14、进一步的改进是,所述第一mos晶体管还包括:

15、第一轻掺杂漏区,形成在所述第一栅极结构两侧的所述半导体衬底中且所述第一轻掺杂漏区和所述第一子侧墙的侧面自对准。

16、第一源漏区,形成在所述第一栅极结构两侧的所述半导体衬底中且所述第一源漏区和所述第一侧墙的侧面自对准;所述第一轻掺杂漏区的结深小于所述第一源漏区的结深,所述第一源漏区的掺杂浓度大于所述第一轻掺杂漏区的掺杂浓度。

17、进一步的改进是,所述第一栅极结构的宽度小于所述第二栅极结构的宽度。

18、所述第一栅极结构之间的间距小于所述第二栅极结构之间的间距。

19、在所述第一mos晶体管的形成区域中,所述第一mos晶体管周期性分布,所述第一侧墙的厚度保证所述第一mos晶体管在沿沟道长度方向上的单元尺寸满足要求,以提升所述第一mos晶体管的集成度;所述第一侧墙的厚度越小,所述第一mos晶体管在沿沟道长度方向上的单元尺寸越小。

20、进一步的改进是,所述第三mos晶体管还包括:

21、第三漂移区,形成在所述第三栅极结构两侧的所述半导体衬底中,所述第三漂移区和所述第一子侧墙的侧面自对准,所述第三漂移区还扩散延伸到所述第三栅极结构的底部。

22、第三源漏区,形成于所述第三漂移区中,所述第三漂移区的结深大于所述第三源漏区的结深,所述第三源漏区的掺杂浓度大于所述第三漂移区的掺杂浓度。

23、在所述第三源漏区和所述第三栅极结构的侧面之间的所述第三漂移区中形成有漂移区场氧。

24、进一步的改进是,所述第一子侧墙的材料包括氧化硅。

25、所述第二子侧墙的材料包括氮化硅或低介电常数材料。

26、所述第三子侧墙的材料保护氧化硅。

27、进一步的改进是,所述第一栅极导电材料层、所述第二栅极导电材料层和所述第三栅极导电材料层都为多晶硅栅或者都为金属栅。

28、为解决上述技术问题,本发明提供的具有不同工作电压的mos晶体管的集成结构的制造方法包括如下步骤:

29、步骤一、在半导体衬底上的第一mos晶体管的形成区域、第二mos晶体管的形成区域和第三mos晶体管的形成区域分别形成第一栅极结构、第二栅极结构和第三栅极结构。

30、第一mos晶体管具有第一工作电压,第二mos晶体管具有第二工作电压,第三mos晶体管具有第三工作电压;所述第三工作电压大于所述第二工作电压以及所述第二工作电压大于所述第一工作电压。

31、所述第一栅极结构由第一栅介质层和第一栅极导电材料层叠加而成,所述第二栅极结构由第二栅介质层和第二栅极导电材料层叠加而成,所述第三栅极结构由第三栅介质层和第三栅极导电材料层叠加而成。

32、所述第二栅介质层的厚度大于所述第一栅介质层的厚度,所述第三栅介质层的厚度大于所述第二栅介质层的厚度。

33、步骤二、在所述第一栅极结构、所述第二栅极结构和所述第三栅极结构的侧面形成第一子侧墙。

34、步骤三、依次沉积第二子侧墙材料层和第三子侧墙材料层。

35、步骤五、对所述第三子侧墙材料层进行全面刻蚀使所述第三子侧墙材料层自对准保留在所述第一栅极结构、所述第二栅极结构和所述第三栅极结构的侧面并组成第三子侧墙。

36、步骤六、形成掩膜层将所述第二mos晶体管的形成区域覆盖、将所述第一mos晶体管的形成区域打开以及将所述第三mos晶体管的形成区域覆盖或打开。

37、步骤七、进行湿法刻蚀将所述掩膜层打开区域的所述第三子侧墙都去除。

38、步骤八、对所述第二子侧墙材料层进行全面刻蚀使所述第二子侧墙材料层自对准保留在所述第一栅极结构、所述第二栅极结构和所述第三栅极结构的侧面并组成第二子侧墙。

39、第一侧墙由自对准形成在所述第一栅极结构的侧面的所述第一子侧墙和所述第二子侧墙叠加而成。

40、第二侧墙由自对准形成在所述第二栅极结构的侧面的所述第一子侧墙、所述第二子侧墙和所述第三子侧墙叠加而成。

41、所述第三侧墙由第一子侧墙和第二子侧墙叠加而成或者由第一子侧墙、第二子侧墙和第三子侧墙叠加而成。

42、在所述第一侧墙的厚度的基础上,所述第二侧墙的厚度通过所述第三子侧墙调节,用以保证在所述第二工作电压下所述第二mos晶体管的gidl漏电满足要求,所述第二侧墙的厚度越厚,所述第二mos晶体管的gidl漏电越小。

43、进一步的改进是,所述第二mos晶体管的形成工艺还包括:

44、在完成步骤二的形成所述第一子侧墙之后,采用离子注入加退火扩散工艺在所述第二栅极结构两侧的所述半导体衬底中形成第二漂移区,所述第二漂移区的离子注入以所述第一子侧墙的侧面为自对准条件,所述第二漂移区在退火扩散后延伸到所述第二栅极结构的底部。

45、在完成步骤八之后,进行源漏注入在所述第二栅极结构两侧的所述第二漂移区中形成第二源漏区,所述第二源漏区和所述第二侧墙的侧面自对准,所述第二漂移区的结深大于所述第二源漏区的结深,所述第二源漏区的掺杂浓度大于所述第二漂移区的掺杂浓度。

46、进一步的改进是,所述第二mos晶体管的gidl漏电满足要求的条件为:所述第二mos晶体管的gidl漏电小于10pa/μm。

47、进一步的改进是,所述第一mos晶体管的形成工艺还包括:

48、在完成步骤二的形成所述第一子侧墙之后,进行轻掺杂漏注入在所述第一栅极结构两侧的所述半导体衬底中形成第一轻掺杂漏区,所述第一轻掺杂漏区的轻掺杂漏注入以所述第一子侧墙的侧面为自对准条件。

49、在完成步骤八之后,进行源漏注入在所述第一栅极结构两侧的所述半导体衬底中形成第一源漏区,所述第一源漏区和所述第一侧墙的侧面自对准,所述第一轻掺杂漏区的结深小于所述第一源漏区的结深,所述第一源漏区的掺杂浓度大于所述第一轻掺杂漏区的掺杂浓度。

50、进一步的改进是,所述第一栅极结构的宽度小于所述第二栅极结构的宽度。

51、所述第一栅极结构之间的间距小于所述第二栅极结构之间的间距。

52、在所述第一mos晶体管的形成区域中,所述第一mos晶体管周期性分布,所述第一侧墙的厚度保证所述第一mos晶体管在沿沟道长度方向上的单元尺寸满足要求,以提升所述第一mos晶体管的集成度;所述第一侧墙的厚度越小,所述第一mos晶体管在沿沟道长度方向上的单元尺寸越小。

53、进一步的改进是,所述第三mos晶体管还包括:

54、在步骤一之前,还包括在所述半导体衬底上形成所述第三mos晶体管的漂移区场氧的步骤。

55、在完成步骤二的形成所述第一子侧墙之后,采用离子注入加退火扩散工艺在所述第三栅极结构两侧的所述半导体衬底中形成第三漂移区,所述第三漂移区的离子注入以所述第一子侧墙的侧面为自对准条件,所述第三漂移区在退火扩散后延伸到所述第三栅极结构的底部。

56、在完成步骤八之后,进行源漏注入在所述第三栅极结构两侧的所述第三漂移区中形成第三源漏区,所述第三漂移区的结深大于所述第三源漏区的结深,所述第三源漏区的掺杂浓度大于所述第三漂移区的掺杂浓度;所述漂移区场氧形成在所述第三源漏区和所述第三栅极结构的侧面之间的所述第三漂移区中。

57、进一步的改进是,所述第一子侧墙的材料包括氧化硅。

58、所述第二子侧墙的材料包括氮化硅或低介电常数材料。

59、所述第三子侧墙的材料保护氧化硅。

60、进一步的改进是,步骤六中,采用步骤一中定义所述第二栅介质层的形成区域的光罩定义所述掩膜层的图形结构。

61、本发明的第二工作电压的第二mos晶体管的第二侧墙是在第一工作电压的第一mos晶体管的第一侧墙所具有的第一子侧墙和第二子侧墙的基础上增加了第三子侧墙形成的,在通过第一子侧墙和第二子侧墙能保证使第一侧墙的厚度较薄从而能减少第一mos晶体管的尺寸并提升第一mos晶体管的形成区域的器件密度的条件下,能通过第三子侧墙单独调节第二侧墙的厚度,从而能增加第二mos晶体管的第二源漏区和第二栅极导电材料层之间的间距,能减少第二mos晶体管的gidl漏电。

62、本发明的第二mos晶体管的第三子侧墙能通过第三子侧墙材料层的沉积加全面刻蚀后再增加一层光罩和湿法刻蚀得到。

63、本发明中,形成第二mos晶体管的第三子侧墙所增加的光罩能借用定义第二栅介质层的形成区域的光罩,这样就不必要增加额外的光罩。定义第二栅介质层的形成区域的光罩也称为双栅(dual gate,dg)层光罩。

- 还没有人留言评论。精彩留言会获得点赞!