导通电流可编程的二极管器件及其阵列制备方法

1.本发明属于半导体与集成电路领域,具体涉及一种基于半导体结构,能够应用于大规模存储器阵列的导通电流可编程的二极管器件,半导体的引入使其与cmos工艺有很好的兼容性,同时其简易的结构也易于三维集成。

背景技术:

2.阻变存储器(resistance random access memory,简称rram)通常具有金属-阻变层-金属的三明治结构,通过改变上下两层金属电极中间阻变材料的电阻来存储信息。相比传统的嵌入式闪存技术,这类存储器具有操作电压低、开关比高、功耗小、耐久性和保持特性好等优异的存储性能够,且具有很好的scaling优势。

3.rram集成时存在严重的读干扰问题,故需要增加选通管来抑制旁路漏电流的干扰。常见的阵列结构有1d1r和1t1r,是由二极管或晶体管和阻变单元组成,这样的结构尽管能够较好的解决器件之间的串扰问题,却使器件面积增大从而削弱了集成度。另一方面,考虑到与cmos工艺兼容的问题,常用的rram底电极技术一般采用惰性金属pt,其刻蚀难度较大,附着性不强等特点使其与cmos兼容的工艺更加复杂。本发明针对以上的读干扰、集成度和cmos兼容三个问题提出了解决方案。

技术实现要素:

4.本发明的目的在于针对rram阵列中旁路电流的干扰、集成度的削弱、cmos工艺兼容性的不足,提出了一种基于半导体结构的导通电流可编程的二极管器件,利用半导体结构与阻变结构中氧空位导电通道的肖特基接触来抑制旁路电流,与cmos工艺完全兼容且易于三维集成。

5.本发明通过以下技术方案实现:

6.本发明提供一种导通电流可编程的二极管器件,包括金属结构、阻变结构和半导体结构;所述阻变结构的电阻能够调节,实现导通电流可编程;所述半导体结构由半导体组成,半导体的态密度函数包含至少一个峰,使得峰能级附近的态密度远大于所述半导体结构除峰之外的能级的态密度;所述金属结构、所述阻变结构和所述半导体结构依次直接相连。

7.进一步地,所述金属结构由一种或多种金属组成,包括但不限于tin、ni、w、ti、al、pd、pt、au、ru;

8.进一步地,所述阻变结构为一种单极型阻变氧化层,由一种或多种氧化物组成,包括但不限于tio2、nio、ni2o3、y2o3、hfo2、wo3、zro2、ta2o5。

9.进一步地,通过调节施加在所述金属结构上的电压和限流大小,所述阻变结构能够在电流导通方向从低阻态转换为高阻态,也能够从高阻态转换为低阻态。

10.进一步地,对于未操作的器件,通过施加较高的正电压,在阻变结构中形成金属性氧空位导电细丝(metallic conductive filament,简称cf),器件变成低阻态(lrs),这个

过程称为forming;对于处于lrs的器件,通过施加较小的正电压使cf在阻变结构和金属结构界面处断开,器件回到高阻态(hrs),这个过程称为reset;对于处于hrs的器件,通过施加较大的正电压使cf断开的部分重新连上,器件回到低阻态(lrs),这个过程称为set。

11.进一步地,所述半导体结构的半导体材料包括但不限于ge、sige、gaas、gan、sic、ga2o3,且态密度函数包含至少一个峰的位置在禁带附近。

12.进一步地,所述阻变结构中局部存在的金属性氧空位导电细丝cf能够与半导体结构直接相连,形成肖特基接触,器件表现为自整流阻变存储器(self-rectifying rram),具有cmos兼容性高和阵列集成度高的优点。

13.进一步地,所述半导体结构的半导体材料采用能将与其直接相连的金属的费米能级钉扎到半导体价带附近,而不受金属本身功函数的影响的半导体时(例如ge材料),半导体表面处肖特基势垒的大小主要取决于半导体自身的性质,使得阻变结构中的氧化物种类和金属结构中的金属种类的可选范围更广。

14.进一步地,由于肖特基势垒的存在,无论阻变结构处于hrs还是lrs,其反向电流都极小,对于数值相同正反电压的整流比可高达105以上,能有效抑制旁路电流,适用于大规模的阵列集成。

15.进一步地,肖特基势垒的反向漏电流密度一般为定值,其反向漏电流大小与器件面积和cf的密度相关,而阻变结构的低阻态电流主要来自于cf的传导,对器件面积的变化不敏感,故可通过调节器件面积大小和cf的密度来调控整流比的大小。

16.进一步地,单极型阻变氧化层使器件可以在电流导通实现set和reset操作。一方面避免了由于反向电流被抑制,无法通过反向电压进行操作的问题,另一方面避免了对肖特基结施加反向电压导致其退化,提高了肖特基结的可靠性。

17.本发明还提供了两种基于上述导通电流可编程的二极管器件的在半导体衬底上的阵列制备方法,具体步骤如下。

18.制备方案一:

19.s1:在p型半导体衬底上通过离子注入或旋涂掺杂形成间隔排列的条状n型半导体作为位线,生长隔离层,将隔离层刻蚀形成间隔排列的沟槽,所述沟槽的范围在所述位线内;

20.s2:在s1得到的结构上生长阻变结构;

21.s3:在s2得到的结构上生长金属结构,并将所述金属结构刻蚀形成间隔排列的字线;

22.s4:在s3得到的结构上,在每条位线的同一端生长金属,形成位线的引出电极。

23.制备方案二:

24.s1:在绝缘层上生长n型半导体,将n型半导体刻蚀形成间隔排列的条状区,作为位线;

25.s2:在s1得到的结构上生长阻变结构;

26.s3:在s2得到的结构上生长金属结构,并将所述金属结构刻蚀形成间隔排列的字线;

27.s4:在s3得到的结构上,在每条位线的同一端生长金属,形成位线的引出电极。

28.本发明还提供了一种基于上述导通电流可编程的二极管器件的3d集成的阵列制

备方法,以ge为例,具体步骤如下:

29.s1:在半导体硅衬底上生长ge的应力缓冲层(ge srb),再依次循环生长sige、重掺杂ge(掺杂浓度大于10

18

cm-3

),最顶层为sige;重掺杂ge作为位线;循环次数大于等于2次;以下为一循环3次的示例:在半导体硅衬底上生长ge的应力缓冲层,再依次生长sige/ge/sige/ge/sige/ge/sige;

30.s2:在s1得到的结构上选择性刻蚀sige,并填充隔离层,隔离层可以采用sio2;

31.s3:在s2得到的结构上选择性刻蚀重掺杂ge,填充轻掺杂ge(掺杂浓度小于10

18

cm-3

);

32.s4:在s3得到的结构上生长阻变结构和保护层,保护层可以采用sin;

33.s5:在s4得到的结构上的器件区选择性刻蚀保护层,并生长金属结构,形成字线;在每条位线的同一端生长金属,形成位线的引出电极。

34.进一步地,所述位线的引出电极直接相连的位线区域为重掺杂半导体,使隧穿电流占主导地位,从而确保欧姆接触,此时所述引出电极为常用金属即可;

35.或者,所述位线的引出电极为能够与半导体结构形成欧姆接触的金属(包括但不限于铋等自由电子数偏低的金属),此时与引出电极直接相连的位线区域不要求是重掺杂半导体。

36.进一步地,本发明所述的器件结构能够基于半导体ge实现,ge由于其远高于si的电子和空穴迁移率,被认为是目前最具前景的晶体管衬底材料之一,目前基于ge的cmos应用备受业界重视,在ge上实现优异的存储器性能具有很大的应用前景。

37.本发明的有益效果是:第一,本发明达到了超高的自整流比,能够应用于大规模的阵列集成;第二,本发明无需外加二极管,利用了半导体自身的整流特性,结构简单,易于三维集成;第三,本发明的导通电流偏小,操作电压均低于5v,大大降低了功耗;第四,本发明可直接在半导体上制备,与先进cmos工艺完全兼容,适合快速发展的半导体集成电路。综上,本发明具有制备工艺简单、制备成本低、集成度高、操作电压低、功耗小、抗干扰能力强、可三维集成、cmos兼容性高的优点。

附图说明

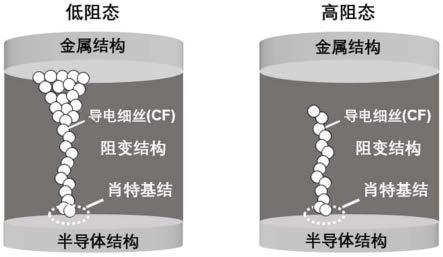

38.图1为本发明中导通电流可编程的二极管器件在hrs和lrs的结构示意图;

39.图2为本发明中导通电流可编程的二极管器件的电流-电压特性图;

40.图3为本发明中基于锗(ge)的阵列制备流程图;

41.图4为本发明中基于绝缘层上锗(goi)的阵列制备流程图;

42.图5为本发明中阵列的操作方式;

43.图6为本发明中阵列的读干扰测试结果;

44.图7为本发明中阵列的擦写干扰测试结果;

45.图8为本发明中阵列的自整流可靠性测试结果;

46.图9为本发明中基于锗(ge)的3d阵列制备流程图和三维立体结构图。

具体实施方式

47.下面结合附图及具体实施例对本发明的技术方案进行详细说明。旨在提供本发明

的基本了解,并不旨在确认本发明的关键或决定性的要素或所要保护的范围。容易理解,在不变更本发明的实质精神下,本领域的技术人员在不脱离本发明及所附的权利要求的精神和范围内,各种替换、变化和修改都是可能够的。因此,以下具体实施方式以及附图仅是对本发明的技术方案的示例性说明,而不应当视为本发明的全部或者是为本发明技术方案的限定或限制。

48.图1为本发明中导通电流可编程的二极管器件在hrs和lrs的结构示意图。本发明提供的导通电流可编程的二极管器件,包括金属结构、阻变结构和半导体结构。阻变结构的电阻能够调节,实现导通电流可编程。半导体结构由半导体组成,半导体的态密度函数包含至少一个峰,使得峰能级附近的态密度远大于半导体结构除峰之外的能级的态密度;金属结构、阻变结构和半导体结构依次直接相连。阻变结构中的cf与半导体结构形成肖特基结。

49.图2为本发明中导通电流可编程的二极管器件的电流-电压特性图。具体为:处于lrs的阻变结构在金属结构施加较小正电压且不限流时,cf在阻变结构和金属结构界面处断开使阻变结构转为hrs;处于hrs的阻变结构在施加较大正电压且限流时,cf重新连接起来使阻变结构转为lrs。由于半导体结构与cf之间势垒的存在,处于hrs和lrs的器件反向电流都极低。

50.自整流比定义为在处于lrs的器件上施加幅值相同,极性相反的读电压时,其正向电流与反向电流的比值。在本实施例中,读取电压为0.8v时,自整流比大于105,大幅度抑制了旁路电流。如前所述,若器件面积进一步缩小,自整流比可进一步提高。器件面积和自整流比不受本实施例限制。

51.进一步地,金属结构由一种或多种金属组成,包括但不限于tin、ni、w、ti、al、pd、pt、au、ru。阻变结构为一种单极型阻变氧化层,由一种或多种氧化物组成,包括但不限于tio2、nio、ni2o3、y2o3、hfo2、wo3、zro2、ta2o5。半导体结构的半导体材料包括但不限于ge、sige、gaas、gan、sic、ga2o3,且态密度函数包含至少一个峰的位置在禁带附近。

52.图3为本发明中基于锗(ge)的阵列制备流程图。

53.以下分别对本实施例的各个组成部分和具体步骤进行详细阐述:

54.101——衬底

ꢀꢀꢀꢀꢀꢀ

102——条状区(位线)

ꢀꢀꢀꢀꢀ

201——隔离层

55.202——阻变结构

ꢀꢀ

301——金属结构(字线)

ꢀꢀꢀ

302——位线引出电极

56.s1:对101进行前处理清洗;

57.s2:在s1清洗后的结构上通过离子注入形成间隔排列的条状区102;

58.s3:在s2得到的结构上生长201,作用为隔离器件,减小寄生电容和提供金属层的接触,将201刻蚀形成间隔排列的条状沟槽;

59.s4:在s3得到的结构上生长202;

60.s5:在s4得到的结构上生长301,并刻蚀形成间隔排列的条状字线。

61.s6:在s5得到的结构中的每条102的同一端形成重掺杂区域并在该区域内生长302,与102形成欧姆接触。

62.s1步骤中,本实施例所述101为p型ge。

63.s2步骤中,本实施例所述102为n型ge。

64.s3步骤中,本实施例所述201为300纳米sio2。

65.s4步骤中,本实施例所述202为5纳米单极性氧化物。在器件forming后其中存在稳

定导电的cf通道,并与102形成肖特基接触。

66.s5步骤中,本实施例所述301为100纳米金属。

67.s6步骤中,本实施例所述302为100纳米金属,能够与102中的重掺杂区域形成欧姆接触。

68.图4为本发明中基于绝缘层上锗(goi)的阵列制备流程图。

69.以下分别对本实施例的各个组成部分和具体步骤进行详细阐述:

70.401——衬底402——条状区(位线)501——阻变结构

71.601——金属结构(字线)602——位线引出电极

72.s1:在401上通过刻蚀形成间隔排列的条状区402。

73.s2:在s1得到的结构上生长501。

74.s3:在s2得到的结构上生长601,并刻蚀形成间隔排列的条状字线。

75.s4:在s5得到的结构中的每条402的同一端形成重掺杂区域并在该区域内生长602,与402形成欧姆接触。

76.s1步骤中,本实施例所述401为绝缘层(si/sio2),所述402为n型ge。

77.s2步骤中,本实施例所述501为5纳米单极性氧化物。在器件forming后单极性氧化物中存在稳定导电的cf通道,并与402形成肖特基接触。

78.s3步骤中,本实施例所述601为100纳米金属。

79.s5步骤中,本实施例所述602为100纳米金属,能够与402中的重掺杂区域形成欧姆接触。

80.所述金属结构、阻变结构、半导体结构的制备方法包括但不限于热蒸发、溅射、原子层沉积、化学气相沉积、电子束蒸发、分子束外延、脉冲激光沉积。

81.图5为本发明中阵列的操作方式。

82.读取操作:选中器件单元对应的字线施加读取电压v

read

,选中器件单元对应的位线施加0v。其他端口接0v或悬空。

83.擦写操作:选中器件单元对应的字线施加操作电压v

write

,选中器件单元对应的位线施加0v。其他字线接0v或悬空,其他位线接v

write

。

84.图6为本发明中阵列的读干扰测试结果。

85.器件具有很强的抗读干扰能力,能有效避免读取器件单元的状态时对阵列中其他器件的干扰。

86.图7为本发明中阵列的擦写干扰测试结果。

87.擦写操作采用v操作电压方案,阵列中只有反向选择的器件单元两端存在反向电压。在反向电压达到4v时,反向选择的器件单元仍保持较好的抗干扰能力,可以满足阵列中器件的擦写操作。

88.图8为本发明中阵列的自整流可靠性测试结果。

89.擦写操作采用v操作电压方案,阵列中器件被反向选择时会受到反向电压,可能会使肖特基结退化。在反向电压达到4v时,器件仍保持稳定的自整流比,保证了在擦写过程中整流特性的可靠性。

90.图9为本发明中基于锗(ge)的3d阵列制备流程图和三维立体结构图。

91.以下分别对本实施例的各个组成部分和具体步骤进行详细阐述:

92.801——衬底802——ge的应力缓冲层803——sige

93.804——重掺杂ge(位线)901——隔离层902——半导体结构

94.903——阻变结构904——阻变结构保护层905——金属结构(字线)

95.s1:在801上生长802,再依次生长803/804/803/804/803/804/803。

96.s2:在s1得到的结构上选择性刻蚀803,并填充901。

97.s3:在s2得到的结构上选择性刻蚀804,填充902。

98.s4:在s3得到的结构上生长903和904。

99.s5:在s4得到的结构上的器件区选择性刻蚀904,并生长905,形成字线。

100.s1步骤中,本实施例所述801为si衬底,所述802为ge的应力缓冲层(gesrb)。

101.s2步骤中,本实施例所述901为二氧化硅。

102.s3步骤中,本实施例所述902为n型ge。

103.s4步骤中,本实施例所述903为5纳米单极性氧化物。在器件forming后其中存在稳定导电的cf通道,并与902形成肖特基接触;所述904为sin保护层,能够保护器件区外的903。

104.s5步骤中,本实施例所述905为100纳米金属。

105.所述金属结构、阻变结构、半导体结构的制备方法包括但不限于热蒸发、溅射、原子层沉积、化学气相沉积、电子束蒸发、分子束外延、脉冲激光沉积。

106.以上所述仅是本发明的优选实施方式,虽然本发明已以较佳实施例披露如上,然而并非用以限定本发明。任何熟悉本领域的技术人员,在不脱离本发明技术方案范围情况下,都可利用上述揭示的方法和技术内容对本发明技术方案做出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何的简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1