一种拼接屏及其制备方法与流程

1.本技术涉及显示技术领域,具体涉及一种拼接屏及其制备方法。

背景技术:

2.显示面板按照驱动方式可以分为无源矩阵(passive matrix,pm)和有源矩阵(active matrix,am)两大类,即直接寻址和薄膜晶体管(thin film transistor,tft)矩阵寻址两类。

3.传统印刷电路板(printed circuit board,简称pcb板)上的led格栅产品采用无源驱动方式,会导致显示面板的,分辨率低,无法满足高端近距离观看需求,观感体验差,难以匹配高端场景需求。玻璃背板上的led采用有源驱动方式,可以实现高分辨率,高解析度需求,满足更多的场景需求,且在透明显示领域有先天优势,可以给观众带来更佳的观感体验,更能匹配高端透明场景需求。

4.目前,led显示屏幕包括miniled和microled,由于led芯片巨量转移技术限制,无法直接做到大屏幕显示,因此拼接屏技术应运而生。其中,拼接屏是采用多个显示屏拼接在一起,形成一个大的显示屏。为实现无缝拼接,在切割为拼接单元尺寸时,会切除玻璃背板上的部分线路,例如将防静电检测线(esd line)及面板检测线(cell test line)切掉,如此会造成玻璃背板的金属裸露在空气中,继而发生金属的腐蚀,造成玻璃基板信赖性问题。

技术实现要素:

5.为实现上述目的,本发明提供一种拼接屏及其制备方法,以解决现有玻璃背板的金属裸露在空气中,金属腐蚀到显示模组内部,引起面内的信号短路或者金属传输信号不良,从而导致面板显示不良的技术问题。

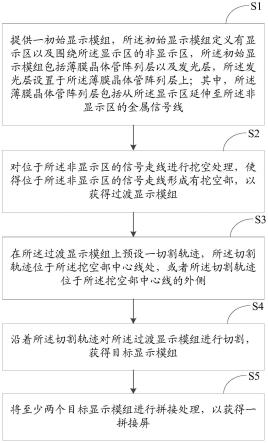

6.为实现上述目的,本发明提供一种拼接屏的制备方法,包括如下步骤:

7.s1、提供一初始显示模组,所述初始显示模组定义有显示区以及围绕所述显示区的非显示区,所述初始显示模组包括薄膜晶体管阵列层以及发光层,所述发光层设置于所述薄膜晶体管阵列层上;其中,所述薄膜晶体管阵列层包括从所述显示区延伸至所述非显示区的金属信号线;

8.s2、对位于所述非显示区的信号走线进行挖空处理,使得位于所述非显示区的信号走线形成有挖空部,以获得过渡显示模组;

9.s3、在所述过渡显示模组上预设一切割轨迹,所述切割轨迹位于所述挖空部中心线处,或者所述切割轨迹位于所述挖空部中心线的外侧;以及

10.s4、沿着所述切割轨迹对所述过渡显示模组进行切割,获得目标显示模组。

11.进一步地,在步骤s2中,所述挖空部的宽度为位于所述非显示区的金属信号线长度的1/3-2/3。

12.进一步地,在步骤s2中,采用激光器对位于所述非显示区的信号走线进行挖空处理,所述金属信号线被分割成第一信号线段及第二信号线段,所述第一信号线段位于所述

非显示区的内边缘处且靠近所述显示区,所述第二信号线段位于所述非显示区的外边缘处且远离所述显示区;其中,所述第一信号线段的长度大于或等于20μm。

13.进一步地,在步骤s1中,所述薄膜晶体管阵列层还包括防护层,所述防护层设置于位于所述非显示区的金属信号线上;其中,所述防护层的长度小于或等于位于所述非显示区的金属信号线的长度。

14.进一步地,所述防护层所用的材质为透明聚酰亚胺聚合物、黄色聚酰亚胺聚合物、含有炭黑的有机光阻材料中的一种。

15.进一步地,在步骤s1中,所述初始显示模组还包括封装层,所述封装层设置于所述发光层上,且从所述显示区延伸至所述非显示区;所述发光层包括呈阵列分布的两个以上led芯片,所述led芯片与所述薄膜晶体管阵列层电连接;所述薄膜晶体管阵列层包括衬底基板以及驱动电路,所述驱动电路设置于所述衬底基板上,所述led芯片与所述驱动电路电连接。

16.进一步地,所述封装层所用的材质包括硅胶、环氧胶、丙烯酸类树脂中的一种;所述封装层的厚度为所述led芯片高度的1.2-2倍。

17.进一步地,在步骤s4之后,还包括:s5、将至少两个目标显示模组进行拼接处理,以获得一拼接屏。

18.为实现上述目的,本发明还提供一种根据前文所述的拼接屏的制备方法制备的拼接屏,包括:目标显示模组,所述目标显示模组包括薄膜晶体管阵列层以及发光层,所述发光层设置于所述薄膜晶体管阵列层上;其中,所述薄膜晶体管阵列层包括从所述显示区延伸至所述非显示区的金属信号线;以及位于所述非显示区的挖空部,所述挖空部与所述信号走线相邻接;当至少两个目标显示模组相互拼接时,一目标显示模组的挖空部与另一目标显示模组的挖空部相邻接。

19.进一步地,所述目标显示模组还包括封装层,所述封装层设置于所述发光层上,且从所述显示区延伸至所述非显示区;所述发光层包括呈阵列分布的两个以上led芯片,所述led芯片与所述薄膜晶体管阵列层电连接;所述薄膜晶体管阵列层包括衬底基板以及驱动电路,所述led芯片与所述驱动电路电连接。

20.上述技术方案中的任一个,具有如下优点或有益效果:提供一种拼接屏及其制备方法,首先通过对位于所述非显示区的信号走线进行挖空处理,使得位于所述非显示区的信号走线形成有挖空部,以获得过渡显示模组;然后,设定所述切割轨迹位于所述挖空部中心线处,或者所述切割轨迹位于所述挖空部中心线的外侧,并且沿着所述切割轨迹对所述过渡显示模组进行切割,获得目标显示模组;最后将至少两个目标显示模组进行拼接处理,获得一个无缝拼接屏。如此,该无缝拼接屏中的任意一个目标显示模组能够避免金属信号线被裸露在空气中,降低了金属信号线会被腐蚀的风险,提高了拼接屏的信赖性。

附图说明

21.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

22.图1为本技术一实施例提供的拼接屏的制备方法的流程图。

23.图2为本技术一实施例提供的初始显示模组的结构示意图。

24.图3为本技术一实施例提供的初始显示模组的平面图。

25.图4为本技术一实施例提供的过渡显示模组的结构示意图。

26.图5为本技术一实施例提供的过渡显示模组的切割示意图。

27.图6为本技术一实施例提供的目标显示模组的结构示意图。

28.图7为本技术一实施例提供的拼接屏的结构示意图。

29.图8为本技术一实施例提供的保护层设置于金属信号走线上的结构示意图。

30.附图标记说明:

31.101、初始显示模组;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

102、过渡显示模组;

32.103、目标显示模组;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

aa、显示区;

33.na、非显示区;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1、薄膜晶体管阵列层;

34.2、发光层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

3、封装层;

35.4、防护层;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11、衬底基板;

36.12、驱动电路;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

110、金属信号线;

37.110a、第一信号线段;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

110b、第二信号线段;

38.121、栅极信号线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

122、源极信号线;

39.10、挖空部;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20、切割轨迹;

40.123、防静电检测线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

124、面板检测线。

具体实施方式

41.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

42.在本技术的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接或可以相互通讯;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本技术中的具体含义。

43.在本技术中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一和第二特征直接接触,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征水平高度小于第二特征。

44.如图1所示,本实施例提供一种拼接屏的制备方法,包括如下步骤s1-s5。

45.s1、如图2所示,提供一初始显示模组101,所述初始显示模组101定义有显示区aa以及围绕所述显示区aa的非显示区na,所述初始显示模组101包括薄膜晶体管阵列层1以及

发光层2,所述发光层2设置于所述薄膜晶体管阵列层1上;其中,所述薄膜晶体管阵列层1包括从所述显示区aa延伸至所述非显示区na的金属信号线110。

46.需要说明的是,所述初始显示模组101为经过防静电检测(esd test)、点灯检测(cell test)等检测,且被判定为合格的显示模组。

47.如图2所示,在步骤s1中,所述薄膜晶体管阵列层1包括衬底基板11以及驱动电路12,所述驱动电路12设置于所述衬底基板11上,所述驱动电路12设有若干个顶栅结构(top gate)的薄膜晶体管(图未示),薄膜晶体管包括有源层、源极、漏极以及栅极等部件,且这些部件之间设有绝缘材料,具体可以参见现有顶栅结构的薄膜晶体管,在此不一一赘述。其中,有源层可以为a-si、a-igzo、a-izo、a-zto、a-itzo、ltps、有机材料或碳纳米管,当有源层为双有源层时,双有源层为a-igzo和a-izo的复合层。本实施例中,所述金属信号线110可以包括多条金属信号线110,这些金属信号线110可以同层设置,也可以不同层设置。

48.如图3所示,本实施例的金属信号线110为不同层设置,所述金属信号线110可以包括沿着第一方向排布的栅极信号线121以及沿着第二方向排布的源极信号线122。其中,所述薄膜晶体管阵列层1还包括防静电检测线123及面板检测线124,防静电检测线123可以是由栅极信号线121延伸至非显示区na的一部分走线,以及由于源极信号线122延伸至非显示区na的一部分走线构成,该防静电检测线123可以连接至一个防静电结构(图未示);面板检测线124可以是由栅极信号线121延伸至非显示区na的一部分走线,该面板检测线124与短路棒(图未示)连接。如此设置,有利于实现初始显示模组101的防静电检测、点灯检测,并且在检测完毕后,可以通过简单切割的方式就能够去除,便于实现无边框的显示模组。

49.所述发光层2包括呈阵列分布的两个以上led芯片,所述led芯片与所述薄膜晶体管阵列层1电连接。本实施例中,所述led芯片与所述驱动电路12电连接。所述led芯片可以为mini led芯片或者micro led芯片。其中,当所述led芯片为mini led芯片时,可以通过表面贴装(smt)工艺把mini led芯片转移到所述薄膜晶体管阵列层1,使得每一个mini led芯片与所述驱动电路12电连接。当所述led芯片为micro led芯片时,可以通过巨量转移工艺把micro led芯片转移到所述薄膜晶体管阵列层1,使得每一个micro led芯片与所述驱动电路12电连接。

50.进一步地,所述薄膜晶体管阵列层1还包括封装层3,所述封装层3设置于所述发光层2上,且从所述显示区aa延伸至所述非显示区na。所述封装层3所用的材质包括硅胶、环氧胶、丙烯酸类树脂中的一种。所述封装层3的厚度为所述led芯片高度的1.2-2倍,可以有效地对所述led芯片进行封装,防止水氧从外界入侵影响所述led芯片的性能。所述封装层3的透光率大于95%,也就是说,所述led芯片所发出的光基本上能够从所述封装层3出射,并且不会影响显示模组的显示效果。

51.s2、对位于所述非显示区na的信号走线进行挖空处理,使得位于所述非显示区na的信号走线形成有挖空部10,以获得过渡显示模组102。

52.具体的,如图4所示,采用激光器对位于所述非显示区na的信号走线进行挖空处理,所述金属信号线110被分割成第一信号线段110a及第二信号线段110b,所述第一信号线段110a位于所述非显示区na的内边缘处且靠近所述显示区aa,所述第二信号线段110b位于所述非显示区na的外边缘处且远离所述显示区aa。激光器为能量较高发热小的激光器,如半导体激光器、准分子激光器。其中,半导体激光器可以发射蓝光、绿光、近紫外光源,准分

子激光器可以发射紫外激光。

53.s3、在所述过渡显示模组102上预设一切割轨迹20,所述切割轨迹20位于所述挖空部10中心线处,或者所述切割轨迹20位于所述挖空部10中心线的外侧。

54.结合图3及图5所示,所述挖空部10的宽度a为位于所述非显示区na的金属信号线110长度b的1/3-2/3,并且所述切割轨迹20位于所述挖空部10中心线处,或者所述切割轨迹20位于所述挖空部10中心线的外侧,如此,第一信号线段110a不会被直接裸露出来,避免了其与空气直接接触的可能性,进而避免了金属信号线110会被腐蚀的风险,提高了目标显示模组103的信赖性。

55.进一步地,所述第一信号线段110a的长度c大于或等于20μm。优选地,所述第一信号线段110a的长度c为18μm、19μm、20μm,如此,过渡显示模组102被切割后,可以尽可能地实现无边框的显示模组。

56.s4、如图5所示,沿着所述切割轨迹20,采用刀轮或者激光器对所述过渡显示模组102进行切割,获得如图6所示的目标显示模组103。

57.s5、将至少两个目标显示模组103进行拼接处理,以获得一拼接屏。

58.如图7所示,当至少两个目标显示模组103相互拼接时,一目标显示模组103的挖空部10与另一目标显示模组103的挖空部10相邻接。拼接屏沿第一方向设置有目标显示模组和第二目标显示模组,其中第一目标显示模组的挖空部与第二目标显示模组的非显示区相匹配,也就是说,第一目标显示模组与第二目标显示模组相互拼接时,第一目标显示模组的显示区与第二目标显示模组的显示区相邻接,从而进一步地实现无缝拼接屏。

59.需要说明的是,本实施例所制备的初始显示模组101,由于该初始显示模组101内的防静电检测线123、面板检测线124未被切割,若直接将多个初始显示模组101拼接在一起,则无法实现无缝拼接屏。此外,若直接将初始显示模组101的部分线路(如防静电检测线123、面板检测线124)直接切掉,会造成金属裸露在空气中,金属腐蚀到显示模组内部,引起面内的信号短路或者金属传输信号不良,从而导致拼接屏显示不良的技术问题。

60.因此,为解决上述问题,本实施例首先通过对位于所述非显示区na的信号走线进行挖空处理,使得位于所述非显示区na的信号走线形成有挖空部10,以获得过渡显示模组102;然后,设定所述切割轨迹20位于所述挖空部10中心线处,或者所述切割轨迹20位于所述挖空部10中心线的外侧,并且沿着所述切割轨迹20对所述过渡显示模组102进行切割,获得目标显示模组103;最后将至少两个目标显示模组103进行拼接处理,获得一个无缝拼接屏,即形成一个大显示屏。此外,该无缝拼接屏中的任意一个目标显示模组103都能够避免金属信号线110被裸露在空气中,避免了金属信号线110会被腐蚀的风险,提高了目标显示模组103的信赖性。

61.结合图6-图7所示,本实施例还提供一种拼接屏,其包括至少两个目标显示模组103,每一目标显示模组103包括薄膜晶体管阵列层1以及发光层2,所述发光层2设置于所述薄膜晶体管阵列层1上。其中,所述薄膜晶体管阵列层1包括从所述显示区aa延伸至所述非显示区na的金属信号线110,以及位于所述非显示区na的挖空部10,所述挖空部10与所述信号走线相邻接。当至少两个目标显示模组103相互拼接时,一目标显示模组103的挖空部10与另一目标显示模组103的挖空部10相邻接。拼接屏沿第一方向设置有目标显示模组和第二目标显示模组,其中第一目标显示模组的挖空部与第二目标显示模组的非显示区相匹

配,也就是说,第一目标显示模组与第二目标显示模组相互拼接时,第一目标显示模组的显示区与第二目标显示模组的显示区相邻接,从而进一步地实现无缝拼接屏。

62.在另一实施例中,如图8所示,所述薄膜晶体管阵列层1还包括防护层4,所述防护层4设置于位于所述非显示区na的金属信号线110上表面。其中,所述防护层4的长度小于或等于位于所述非显示区na的金属信号线110的长度,如此在采用激光器对金属信号走线进行挖空处理时,可以有效避免因激光损伤设置于金属信号走线上方的膜层,从而保证显示模组的性能。所述防护层4为不透过激光的有机膜层,即所述防护层4为透过率较低的有机膜层。所述防护层4所用的材质可以为透明聚酰亚胺聚合物、黄色聚酰亚胺聚合物、含有炭黑的有机光阻材料中的一种。

63.以上对本技术实施例所提供的一种拼接屏及其制备方法进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1