屏蔽电路与半导体装置的制作方法

本发明系关于一种用于降低辐射的屏蔽电路,特别是应用于电感电容电路之屏蔽电路。

背景技术:

1、在集成电路(ic)芯片中,电感是一种被动组件,它将能量储存于由通过它的电流所产生的磁场中。电感可包括一或多个线圈,以形成一或多个回路,而这些回路在线圈内部产生磁场。取决于通过电感的电流,线圈内的磁场可随时间变化。

2、电感通常搭配电容以形成一谐振电路,例如,一电感电容共振腔(lc tank)电路,用以作为电谐振器,以储存电路共振时振荡的能量。举例而言,于一射频电路中搭配电感电容共振腔(lc tank)电路,可使整体电路容易操作在较高的频率,且具有较佳的相位噪声表现,但这样的应用容易因为电感所感应出的磁场而产生不乐见的辐射问题,使得信号透过电感被辐射出去。此外,电感电容共振腔电路的其他部分也会产生辐射,造成干扰。

3、为了解决电子电路带来的辐射问题,需要一种新的屏蔽电路,特别是应用于包含电感之电子电路的屏蔽电路,以降低或消除因电感或其他电子组件而产生的辐射。

技术实现思路

1、本发明之一目的在于提供一种新的屏蔽电路,应用于电感及包含电感之电子电路,以降低或消除因电感或其他电子组件而产生的辐射,解决上述问题。

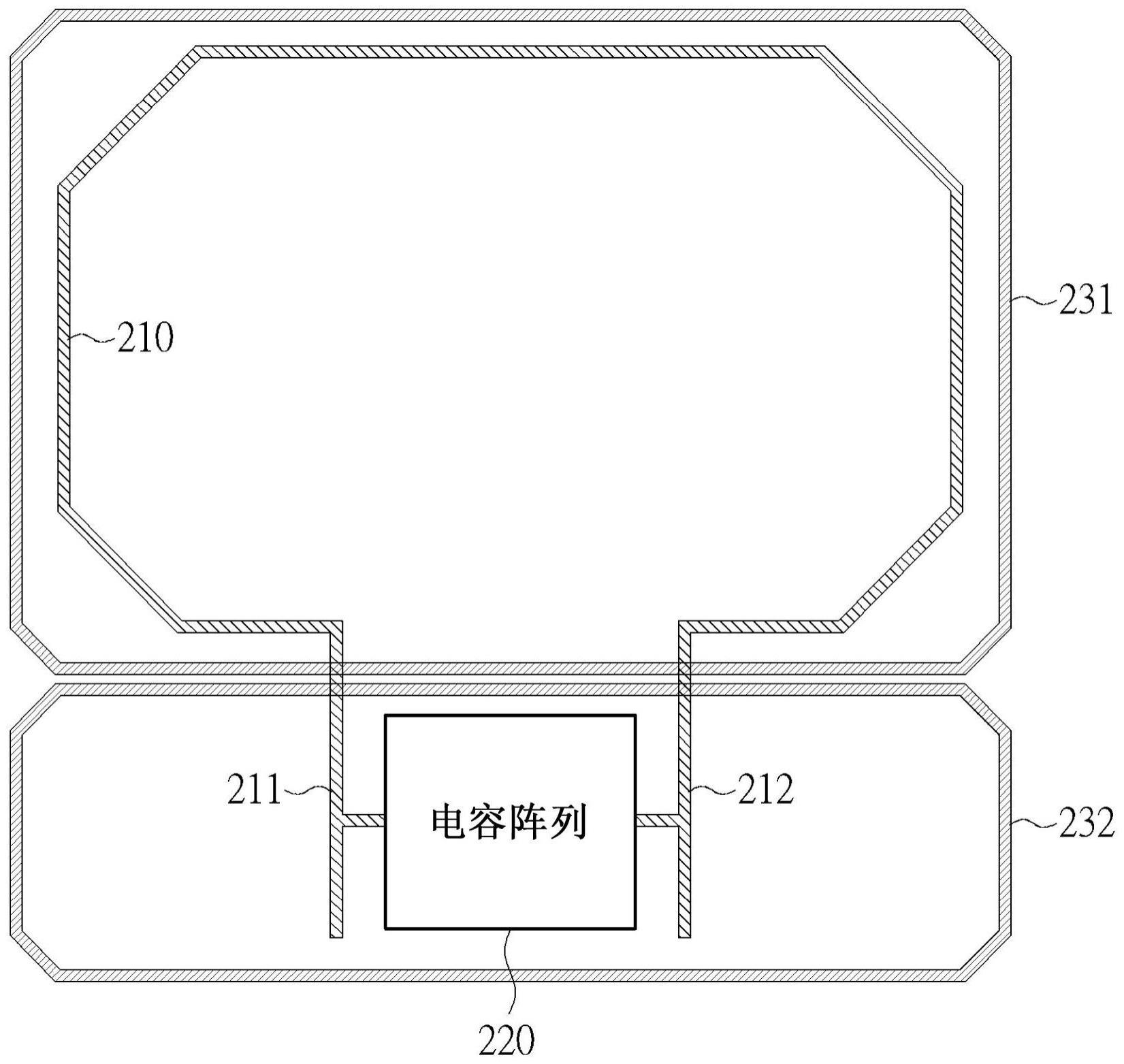

2、根据本发明之一实施例,一种屏蔽电路,应用于一半导体装置,包括一第一屏蔽结构与一第二屏蔽结构。第一屏蔽结构形成一第一封闭回路,并且被设置在半导体装置内之一电感附近。第二屏蔽结构形成一第二封闭回路,并且被设置在耦接电感的一电子组件附近。

3、根据本发明之另一实施例,一种半导体装置,包括一屏蔽电路与一电子组件。屏蔽电路包括至少二个屏蔽结构,各屏蔽结构形成一封闭回路。电子组件耦接一电感,所述至少二个屏蔽结构之其中一个被设置在电子组件附近。

技术特征:

1.一种屏蔽电路,应用于一半导体装置,包括:

2.根据权利要求1所述的屏蔽电路,其中,该第一屏蔽结构环绕该电感。

3.根据权利要求1所述的屏蔽电路,其中,沿着一垂直方向,该第一屏蔽结构在一既定平面上的一投影包围该电感在该既定平面上的一投影。

4.根据权利要求1所述的屏蔽电路,其中,该第二屏蔽结构环绕该电子组件。

5.根据权利要求1所述的屏蔽电路,其中,沿着一垂直方向,该第二屏蔽结构在一既定平面上的一投影包围该电子组件在该既定平面上的一投影。

6.一种半导体装置,包括:

7.根据权利要求6所述的半导体装置,其中,该屏蔽电路包括:

8.根据权利要求7所述的半导体装置,其中,该第一屏蔽结构环绕该电感。

9.根据权利要求7所述的半导体装置,其中,该第一屏蔽结构在该既定平面上的一投影包围该电感在该既定平面上的一投影。

10.根据权利要求7所述的半导体装置,其中,该第二屏蔽结构环绕该电子组件。

技术总结

本申请涉及一种屏蔽电路与半导体装置。一种屏蔽电路,应用于一半导体装置,包括一第一屏蔽结构与一第二屏蔽结构。第一屏蔽结构形成一第一封闭回路,并且被设置在半导体装置内的一电感附近。第二屏蔽结构形成一第二封闭回路,并且被设置在耦接电感的一电子组件附近。

技术研发人员:陈韵中

受保护的技术使用者:瑞昱半导体股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!