部分屏蔽的半导体器件和其制作方法与流程

本申请总体上涉及半导体技术,更具体地,涉及一种部分屏蔽的半导体器件及一种用于制造半导体器件的方法。

背景技术:

1、对于电子产品中的电子元件,需要实施电磁干扰(emi)屏蔽,以防止受到电磁场、静电场等的干扰。此外,电子元件的emi屏蔽一般要求通过emi屏蔽外的接触垫接地。然而,这种外部接触垫增加了屏蔽电子元件与同一基板、例如印刷电路板上其他非屏蔽电子元件的距离,这阻碍了半导体封装集成度的进一步提高。

2、因此,需要一种用于制造具有屏蔽层的半导体器件的改进方法。

技术实现思路

1、本申请的一个目的是提供一种部分屏蔽的半导体器件和制造这种半导体器件的方法。

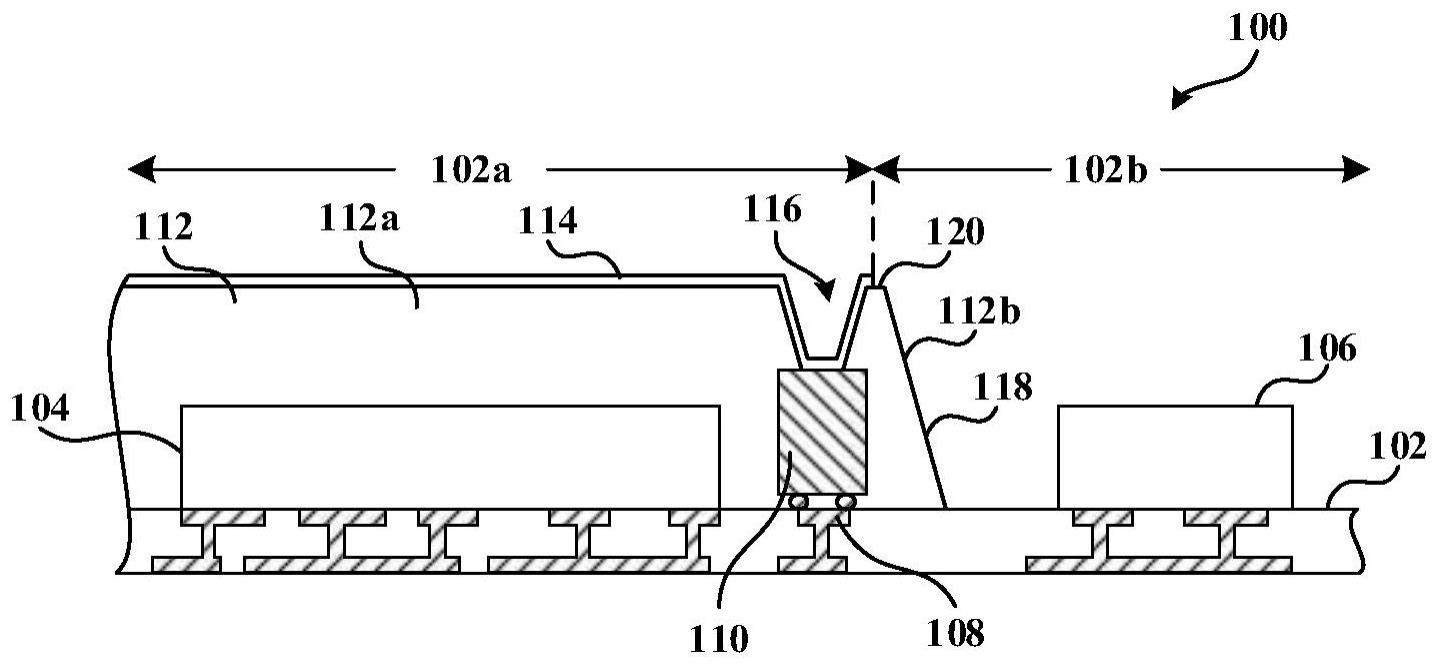

2、根据本申请的一个方面,提供了一种用于制造半导体器件的方法。该方法包括:提供具有第一区域和第二区域的基板,其中第一区域包括至少一个电子元件和形成于其中的导电图案;在导电图案上形成导电条;在基板的第一区域中形成密封层以覆盖至少一个电子元件、导电条和导电图案;移除位于导电条上方的密封层的一部分以暴露导电条并将密封层分为主体部分和周边部分,其中周边部分相对于主体部分邻近基板的第二区域;在基板上方设置沉积掩模以覆盖第二区域;以及在基板上沉积导电材料,以在未被沉积掩模覆盖的基板上形成屏蔽层。

3、根据本申请的另一方面,提供了一种部分屏蔽的半导体器件。部分屏蔽的半导体器件包括:基板,其具有第一区域和与第一区域相邻的第二区域,其中第一电子元件设置在第一区域内,且第二电子元件设置在第二区域内;形成于基板上且覆盖第一电子元件的密封层;屏蔽层,其形成在第一区域中的密封层上,但不形成在第二区域中;形成于基板上及密封层内的导电图案;以及导电条,其形成于密封层内并从密封层暴露,其中导电条的至少一部分被屏蔽层屏蔽并与屏蔽层连接,以将屏蔽层与基板上的导电图案电耦接。

4、应当理解,前面的一般性描述和下面的详细描述都只是示例性和说明性的,而不是对本发明的限制。此外,并入并构成本说明书一部分的附图示出了本发明的实施例并且与说明书一起用于解释本发明的原理。

技术特征:

1.一种用于制造半导体器件的方法,其特征在于,包括:

2.根据权利要求1所述的方法,其特征在于,所述密封层的周边部分包括倾斜的侧壁。

3.根据权利要求1所述的方法,其特征在于,移除在所述导电条上方的所述密封层的一部分包括:

4.根据权利要求1所述的方法,其特征在于,移除在所述导电条上方的所述密封层的一部分包括:

5.根据权利要求1所述的方法,其特征在于,所述密封层的周边部分包括部分位于所述导电条上方的倾斜侧壁,并且其中移除在所述导电条上方的所述密封层的一部分包括:

6.根据权利要求1所述的方法,其特征在于,在所述基板上方设置沉积掩模以至少覆盖所述第二区域包括:

7.根据权利要求1所述的方法,其特征在于,在所述基板上方设置沉积掩模以至少覆盖所述第二区域包括:

8.根据权利要求1所述的方法,其特征在于,在所述基板上方设置沉积掩模以至少覆盖所述第二区域包括:

9.根据权利要求1所述的方法,其特征在于,在所述基板上方设置沉积掩模以至少覆盖所述第二区域包括:

10.根据权利要求1所述的方法,其特征在于,移除所述导电条上方的所述密封层的一部分包括:

11.根据权利要求10所述的方法,其特征在于,将所述沉积掩模突悬在所述沟槽上方并暴露所述导电条的一部分包括:

12.根据权利要求1所述的方法,其特征在于,所述第二区域包括至少一个另外的电子元件。

13.一种部分屏蔽的半导体器件,其特征在于,包括:

14.根据权利要求13所述的部分屏蔽的半导体器件,其特征在于,所述密封层包括在所述导电条上方的沟槽以从所述密封层暴露所述导电条。

15.根据权利要求13所述的部分屏蔽的半导体器件,其特征在于,所述屏蔽层沉积在所述沟槽内,但不覆盖所述沟槽的整个内表面。

技术总结

本申请提供一种用于制造半导体器件的方法,其包括:提供具有第一区域和第二区域的基板,其中第一区域包括至少一个电子元件和形成于其中的导电图案;在导电图案上形成导电条;在基板的第一区域中形成密封层以覆盖至少一个电子元件、导电条和导电图案;移除位于导电条上方的密封层的一部分以暴露导电条并将密封层分为主体部分和周边部分,其中周边部分相对于主体部分邻近基板的第二区域;在基板上方设置沉积掩模以覆盖第二区域;以及在基板上沉积导电材料,以在未被沉积掩模覆盖的基板上形成屏蔽层。

技术研发人员:李勋择,宋相镐,李娟芝,李喜秀

受保护的技术使用者:星科金朋私人有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!