显示装置的制作方法

1.本发明的实施方式之一涉及显示装置。特别是,本发明的实施方式之一涉及使用具有氧化物半导体的晶体管的显示装置。

背景技术:

2.最近,正在开发将氧化物半导体代替非晶硅、低温多晶硅及单晶硅用于通道的晶体管(例如,专利文献1、2)。将氧化物半导体用于通道的晶体管与将非晶硅用于通道的晶体管相同,通过简单的结构及低温工艺形成。已知将氧化物半导体用于通道的晶体管具有比将非晶硅用于通道的晶体管更高的迁移性,而且关态电流非常低。

3.近年来,为了进一步提高显示装置的分辨率,不断缩小像素尺寸。随着像素尺寸的缩小,探讨了缩小布线宽度及晶体管尺寸。但是,它们的缩小有限,且构成像素电路的金属层及半导体层的配置导致开口率变小。因而,正在进行开发将在通道中使用即使晶体管尺寸小也能够获得足以驱动像素电路的特性的氧化物半导体层的晶体管用于像素电路的晶体管。

4.现有技术文献

5.专利文献

6.专利文献1:日本特开2014-146819号公报

7.专利文献2:日本特开2015-159315号公报

技术实现要素:

8.发明所要解决的技术问题

9.随着像素尺寸的缩小,配置像素电路中使用的电容元件的区域受限。因此,存在难以形成大小足以驱动像素电路的电容元件的问题。在其影响下,存在像素电路中的电荷的保持特性降低,显示装置的显示动作变得不稳定的问题。

10.本发明的实施方式之一的一个课题在于实现显示装置中稳定的显示动作。

11.用于解决技术问题的技术方案

12.本发明的一种实施方式所涉及的显示装置具有:第一晶体管,具备氧化物半导体层、与所述氧化物半导体层对置的第一栅极电极、及所述氧化物半导体层和所述第一栅极电极之间的第一栅极绝缘层;第一透明导电层,设于所述第一晶体管的上方;第二透明导电层,设于所述第一透明导电层的上方,与所述第一透明导电层绝缘,与所述第一透明导电层对置;以及第三透明导电层,设于所述第二透明导电层的上方,与所述第二透明导电层绝缘,连接于所述第一透明导电层,与所述第二透明导电层对置。

13.本发明的一种实施方式所涉及的显示装置具有:第一晶体管,具备氧化物半导体层、与所述氧化物半导体层对置的第一栅极电极、及所述氧化物半导体层和所述第一栅极电极之间的第一栅极绝缘层;第一透明导电层,设于所述第一晶体管的上方;第二透明导电层,设于所述第一透明导电层的上方,与所述第一透明导电层绝缘,在像素的透光区域中与

所述第一透明导电层重叠;以及第三透明导电层,设于所述第二透明导电层的上方,与所述第二透明导电层绝缘,连接于所述第一透明导电层,在所述透光区域中与所述第二透明导电层重叠。

附图说明

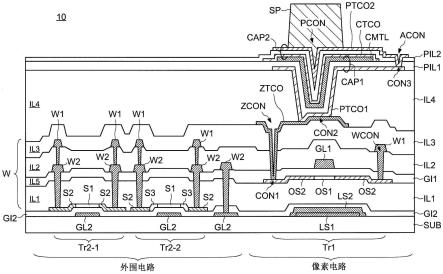

14.图1是示出本发明的一种实施方式所涉及的显示装置的概要的剖面图。

15.图2是示出本发明的一种实施方式所涉及的显示装置的概要的俯视图。

16.图3是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

17.图4是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

18.图5是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

19.图6是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

20.图7是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

21.图8是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

22.图9是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

23.图10是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

24.图11是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

25.图12是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

26.图13是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

27.图14是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。

28.图15是示出本发明的一种实施方式所涉及的显示装置的概要的俯视图。

29.图16是示出本发明的一种实施方式所涉及的显示装置的电路构成的框图。

30.图17是示出本发明的一种实施方式所涉及的显示装置的像素电路的电路图。

具体实施方式

31.下面,参考附图对本发明的各实施方式进行说明。下面的公开仅为示例。本领域技术人员在保持发明的主旨的同时通过适当变更实施方式的构成而容易想到的构成当然也包含在本发明的范围内。附图中,为了更明确说明,与实际方案相比,可能仅示意性示出各

部分的宽度、厚度、形状等。但是,图示的形状仅为示例,并不限定本发明的解释。在本说明书及各个图中,作为与已提及的图中所述的前述构成相同的构成,在相同符号的后面带有阿拉伯字母,可能适当省略详细说明。

32.在本发明的各实施方式中,将从基板面向氧化物半导体层的方向称为上或上方。相反地,将从氧化物半导体层面向基板的方向称为下或下方。如此一来,为了方便说明,虽然使用上方或下方这些表达进行说明,但例如基板和氧化物半导体层的上下关系也可以配置为与图示不同的朝向。在下面的说明中,如上所述,例如基板上的氧化物半导体层这一表述仅说明了基板和氧化物半导体层的上下关系,也可以在基板和氧化物半导体层之间配置其它部件。上方或下方表示多个层层叠而成的结构中的层叠顺序,在表述为晶体管的上方的像素电极的情况下,也可以为在俯视观察时晶体管与像素电极不重叠的位置关系。另一方面,在表述为晶体管的铅直上方的像素电极的情况下,表示在俯视观察时晶体管和像素电极重合的位置关系。

[0033]“显示装置”是指使用光电层来显示影像的结构体。例如,显示装置这一术语有时也指包括光电层的显示面板、或在显示单元上安装其它光学部件(例如,偏光部件、背光、触控面板等)而成的结构体。只要不会导致技术冲突,则“光电层”可以包括液晶层、电致发光(el)层、电致变色(ec)层、电泳层。因此,在后述的实施方式中,作为显示装置,示例包括液晶层的液晶显示装置进行说明,但本实施方式中的结构也可以应用于包括上述的其它光电层的显示装置。

[0034]

在本说明书中,只要没有明确指明,“α包括a、b或c”、“α包括a、b及c中的任意一者”、“α包括选自由a、b及c构成的组中的一个”的表述并不排除α包括a~c的多个组合的情况。并且,这些表述也不排除α包括其它要素的情况。

[0035]

需要说明的是,只要不会导致技术冲突,下面的各实施方式能够彼此组合。

[0036]

[1.第一种实施方式]

[0037]

[1-1.显示装置10的构成]

[0038]

使用图1~图14对本发明的一种实施方式所涉及的显示装置10的构成进行说明。图1是示出本发明的一种实施方式所涉及的显示装置的概要的剖面图。图2是示出本发明的一种实施方式所涉及的显示装置的概要的俯视图。图3~图14是对本发明的一种实施方式所涉及的显示装置中的各层的布局进行说明的俯视图。图1的剖面图是用于对显示装置10的层结构进行说明的剖面图,有时也与图2的俯视图不完全一致。

[0039]

如图1所示,显示装置10设于基板sub的上方。显示装置10具有晶体管tr1、晶体管tr2(tr2-1、tr2-2)、布线w(w1、w2)、连接电极ztco、像素电极ptco1、公用辅助电极cmtl、公用电极ctco、以及像素电极ptco2。tco是transparent conductive oxide(透明导电性氧化物)的简称。晶体管tr1是显示装置10的像素电路中所包括的晶体管(例如,选择晶体管)。晶体管tr2是外围电路中所包括的晶体管。外围电路是驱动像素电路的驱动电路,详细内容将在下文叙述。

[0040]

[1-2.晶体管tr1的构成]

[0041]

晶体管tr1具有氧化物半导体层os(os1、os2)、栅极绝缘层gi1、及栅极电极gl1。栅极电极gl1与氧化物半导体层os对置。栅极绝缘层gi1设于氧化物半导体层os和栅极电极gl1之间。在本实施方式中,示例了在设于显示区域的像素电路中,相对于栅极电极gl1在基

板sub侧设有氧化物半导体层os的顶栅型晶体管,但也可以使用栅极电极gl1和氧化物半导体层os的位置关系相反的底栅型晶体管。有时将栅极绝缘层gi1称为“第一栅极绝缘层”。有时将栅极电极gl1称为“第一栅极电极”。

[0042]

氧化物半导体层os包括氧化物半导体层os1、os2。氧化物半导体层os1是在俯视观察时与栅极电极gl1重叠的区域的氧化物半导体层。氧化物半导体层os1作为半导体层发挥功能,根据提供给栅极电极gl1的电压在导通状态和非导通状态之间切换。即,氧化物半导体层os1作为晶体管tr1的通道发挥功能。氧化物半导体层os2作为导电层发挥功能。氧化物半导体层os1、os2是由相同的氧化物半导体层形成的层。例如,氧化物半导体层os2是通过向物性与氧化物半导体层os1相同的层中掺杂杂质来进行低电阻化的氧化物半导体层。

[0043]

绝缘层il2设于栅极电极gl1之上。布线w1设于绝缘层il2之上。布线w1经由设于绝缘层il2及栅极绝缘层gi1的开口wcon与氧化物半导体层os2连接。向连接于氧化物半导体层os2的布线w1传递与像素的灰度相关的数据信号。绝缘层il3设于绝缘层il2及布线w1之上。

[0044]

连接电极ztco设于绝缘层il3之上。连接电极ztco经由设于绝缘层il3、il2、以及栅极绝缘层gi1的开口zcon与氧化物半导体层os2连接。连接电极ztco在开口zcon的底部与氧化物半导体层os2相接。连接电极ztco是透明导电层。

[0045]

将连接电极ztco与氧化物半导体层os2相接的区域称为第一触点区域con1。有时将连接电极ztco称为“第四透明导电层”。详细内容将在下文叙述,在俯视观察时,连接电极ztco具备:与栅极电极gl1及氧化物半导体层os1重叠的部分(第一部分pt1)、以及在与栅极电极gl1及布线w1不重叠的第一触点区域con1中与氧化物半导体层os2相接的部分(第二部分pt2)(参见图9)。在俯视观察时,第一触点区域con1包括在像素的显示区域(透光区域)中。

[0046]

如上所述,在第一触点区域con1中,连接电极ztco与氧化物半导体层os2直接相接。与硅层等半导体层相接地形成例如ito层等透明导电层之后,半导体层的表面因ito成膜时的工艺气体及氧离子而氧化。形成于半导体层的表面的氧化层的电阻高,因此,半导体层和透明导电层间的接触电阻变高。结果导致半导体层和透明导电层的电接触产生故障。另一方面,即使与氧化物半导体层相接地形成上述透明导电层,也不会在氧化物半导体层的表面上形成如上所述那样的高电阻氧化层。因此,氧化物半导体层和透明导电层之间的电接触不会产生故障。

[0047]

绝缘层il4设于连接电极ztco之上。通过在较绝缘层il4更下层处设置的结构体而形成高度差。绝缘层il4缓和该高度差。有时将绝缘层il4称为平坦化膜。像素电极ptco1设于绝缘层il4之上。即,像素电极ptco1设于晶体管tr1的上方。开口pcon设于绝缘层il4。像素电极ptco1经由开口pcon与连接电极ztco连接。将连接电极ztco与像素电极ptco1相接的区域称为第二触点区域con2。在俯视观察时,第二触点区域con2与栅极电极gl1重叠(参见图10)。更具体而言,在俯视观察时,第二触点区域con2与栅极电极gl1的图案端部重叠。像素电极ptco1是透明导电层。就上述的构成而言,像素电极ptco1经由连接电极ztco连接于晶体管tr1。有时将像素电极ptco1称为“第一透明导电层”。

[0048]

绝缘层pil1设于像素电极ptco1之上。公用辅助电极cmtl及公用电极ctco设于绝缘层pil1之上。公用电极ctco与像素电极ptco1绝缘,并与像素电极ptco1对置。公用电极

ctco以多个像素公用的方式而设置。详细内容将在下文叙述,在本实施方式中,公用电极ctco以沿行方向排列的像素公用的方式而设置(参见图13)。有时将公用电极ctco称为“第二透明导电层”。详细内容将在下文叙述,公用辅助电极cmtl和公用电极ctco具有不同的平面图案(参见图12及图13)。

[0049]

公用辅助电极cmtl是金属层。公用电极ctco是透明导电层。公用辅助电极cmtl的电阻小于公用电极ctco的电阻。公用辅助电极cmtl也作为遮光层发挥功能。就上述的构成而言,在晶体管tr1的上方,遮光层(公用辅助电极cmtl)设为限定多个像素各自的区域。该遮光层通过阻断来自邻接的像素的光来抑制混色的发生。另外,公用辅助电极cmtl具有与公用电极ctco相同的功能。因此,有时将公用辅助电极cmtl和公用电极ctco一同称为“公用电极”。

[0050]

绝缘层pil2设于公用电极ctco之上。像素电极ptco2设于绝缘层pil2之上。像素电极ptco2与公用电极ctco绝缘,且与公用电极ctco对置。像素电极ptco2经由设于绝缘层pil1、pil2的开口acon与像素电极ptco1连接。有时将像素电极ptco2称为“第三透明导电层”。将像素电极ptco2与像素电极ptco1相接的区域称为第三触点区域con3。在俯视观察时,第三触点区域con3与公用辅助电极cmtl不重叠(参见图12)。即,像素电极ptco2在像素的透光区域中与像素电极ptco1相接。

[0051]

如上所述,在对置的像素电极ptco1和公用电极(公用电极ctco及公用辅助电极cmtl)之间,形成设有绝缘层pil1的第一电容元件cap1作为电介质。在对置的像素电极ptco2和公用电极(公用电极ctco及公用辅助电极cmtl)之间,形成设有绝缘层pil2的第二电容元件cap2作为电介质。第一电容元件cap1与第二电容元件cap2层叠。详细内容将在下文叙述,在俯视观察时,第一电容元件cap1与第二电容元件cap2重叠(参见图14)。这些电容元件作为像素电路中的保持电容发挥功能。

[0052]

间隔物sp设于像素电极ptco2之上。针对部分像素设置间隔物sp。例如,可以针对蓝色像素、红色像素、绿色像素中的任意一像素设置间隔物sp。其中,间隔物sp也可以设于全部像素。间隔物sp的高度为液晶盒高度的一半高。需要说明的是,对置基板上也设有间隔物,在俯视观察时,对置基板的间隔物与上述间隔物sp重叠。

[0053]

晶体管tr1和基板sub之间设有遮光层ls。在本实施方式中,作为遮光层ls,设有遮光层ls1、ls2。其中,遮光层ls也可以仅由遮光层ls1或仅由ls2形成。在俯视观察时,遮光层ls设于栅极电极gl1与氧化物半导体层os重叠的区域。即,在俯视观察时,遮光层ls设于与氧化物半导体层os1重叠的区域(参见图5)。遮光层ls抑制从基板sub侧射入的光到达氧化物半导体层os1。在使用导电层作为遮光层ls的情况下,可以向遮光层ls施加电压以控制氧化物半导体层os1。在向遮光层ls施加电压的情况下,遮光层ls和栅极电极gl1可以在像素电路的周边区域连接。在俯视观察时,上述第一触点区域con1设于与遮光层ls不重叠的区域(参见图2)。

[0054]

[1-3.晶体管tr2的构成]

[0055]

晶体管tr2具有p型的晶体管tr2-1及n型的晶体管tr2-2。

[0056]

p型的晶体管tr2-1及n型的晶体管tr2-2均具有栅极电极gl2、栅极绝缘层gi2、半导体层s(s1、s2、s3)。栅极电极gl2与半导体层s对置。栅极绝缘层gi2设于半导体层s和栅极电极gl2之间。在本实施方式中,作为这些外围电路中使用的晶体管tr2,示例了在较半导体

层s更靠近基板sub侧处设有栅极电极gl2的底栅型晶体管,但也可以使用半导体层s和栅极电极gl2的位置关系相反的顶栅型晶体管。有时将栅极电极gl2称为“第二栅极电极”。有时将栅极绝缘层gi2称为“第二栅极绝缘层”。

[0057]

p型的晶体管tr2-1的半导体层s包括半导体层s1、s2。n型的晶体管tr2-2的半导体层s包括半导体层s1、s2、s3。半导体层s1是在俯视观察时与栅极电极gl2重叠的区域的半导体层。半导体层s1作为晶体管tr2-1及tr2-1的通道发挥功能。半导体层s2作为导电层发挥功能。半导体层s3作为电阻高于半导体层s2的导电层发挥功能。半导体层s3通过使朝向半导体层s1侵入的热载子衰减来抑制热载子劣化。

[0058]

绝缘层il1及绝缘层il5设于半导体层s之上。绝缘层il5是与晶体管tr1的栅极绝缘层gi1相同的层。即,绝缘层il5直接与栅极绝缘层gi1不经由界面地连续。布线w2设于绝缘层il5之上。布线w2经由设于绝缘层il1及绝缘层il5的开口与半导体层s2连接。绝缘层il2设于布线w2之上。布线w1设于绝缘层il2之上。布线w1经由设于绝缘层il2的开口与布线w2连接。有时将绝缘层il5称为“第一绝缘层”。

[0059]

栅极电极gl2和遮光层ls2是相同的层。布线w2和栅极电极gl1是相同的层。相同的层表示设于基板上的不同位置的多个部件是由相同工艺形成的部件。因此,表述为相同的层的多个部件是相同的材质,且,与某一公用的层相接。相同的材质表示该多个部件由相同的单一材质形成。或者,表示在该多个部件通过层叠多个层而形成的情况下,该多个层各自的材质相同,并且该多个层的层叠构成也相同。

[0060]

图1中,栅极电极gl2和遮光层ls2与栅极绝缘层gi2相接。布线w2和栅极电极gl1与栅极绝缘层gi1及绝缘层il5相接。换而言之,栅极电极gl2和遮光层ls2与不经由界面地连续的层或部件相接。同样地,布线w2和栅极电极gl1与不经由界面地连续的层或部件相接。

[0061]

[1-4.显示装置10的平面布局]

[0062]

使用图2~图14来说明显示装置10的像素的平面布局。图2中,省略了像素电极ptco1、ptco2、公用辅助电极cmtl、公用电极ctco及间隔物sp。它们的平面布局分别示于图11~图14。

[0063]

如图2及图3所示,遮光层ls沿d1方向延伸。遮光层ls的形状根据像素而不同。在本实施方式中,设有从沿d1方向延伸的遮光层ls的一部分向d2方向突出的突出部pjt。如图5所示,在俯视观察时,遮光层ls设于包括栅极电极gl1与氧化物半导体层os重叠的区域在内的区域。也可以将栅极电极gl1称为“栅极线”。

[0064]

如图2、图4及图5所示,氧化物半导体层os沿d2方向延伸。栅极电极gl1以与氧化物半导体层os交叉的方式沿d1方向延伸。栅极电极gl1的图案设于遮光层ls的图案的内侧。换而言之,氧化物半导体层os形成为与栅极电极gl1交叉的条状。

[0065]

如图2、图6及图7所示,开口wcon在氧化物半导体层os的图案的上端附近设于与布线w1(w1-1、w1-2)重叠的区域。氧化物半导体层os的图案的主要部分在邻接的布线w1之间(w1-1和w1-2之间)沿d2方向延伸。氧化物半导体层os的图案的剩余部分从该主要部分沿相对于d1方向及d2方向倾斜方向延伸,并与开口wcon重叠。

[0066]

如图2及图7所示,多个布线w1沿d2方向延伸。在需要将邻接的布线w1分别区分而进行说明的情况下,将邻接的布线w1称为布线w1-1(第一布线)及布线w1-2(第二布线)。在该情况下,氧化物半导体层os的主要部分在第一布线w1-1和第二布线w1-2之间沿d2方向延

伸,可以与栅极电极gl1交叉。就上述的构成而言,氧化物半导体层os沿d2方向设为条状(具有长边的形状),在氧化物半导体层os在长边方向上的一端部与布线w1-1(第一布线)连接。

[0067]

如图2、图8及图9所示,开口zcon设于氧化物半导体层os的图案的下端附近。开口zcon设于与氧化物半导体层os的图案重叠的区域、且与栅极电极gl1不重叠的区域。开口zcon设于与连接电极ztco重叠的区域。连接电极ztco的第一部分pt1在第一布线w1-1和第二布线w1-2之间与栅极电极gl1及氧化物半导体层os重叠。由此,连接电极ztco的第二部分pt2在与栅极电极gl1及布线w1不重叠的开口zcon(第一触点区域con1)与氧化物半导体层os相接。

[0068]

就上述的构成而言,氧化物半导体层os在氧化物半导体层os在长边方向上的另一端部与连接电极ztco连接。连接电极ztco与氧化物半导体层os相同地形成为沿d2方向延伸的条状。在d1方向上,连接电极ztco的宽度小于氧化物半导体层os的宽度。

[0069]

如图2、图7及图8所示,氧化物半导体层os相对于栅极电极gl1在开口zcon的相反侧与布线w1相接。开口zcon与遮光层ls不重叠。

[0070]

如图2、图10及图11所示,开口pcon设于连接电极ztco的图案的上端附近。开口pcon设于包括栅极电极gl1的图案端部的区域。同样地,开口pcon设于包括连接电极ztco的图案端部的区域。换而言之,开口pcon设于与栅极电极gl1及连接电极ztco两者的图案重叠的区域、仅与栅极电极gl1的图案重叠的区域、或仅与连接电极ztco的图案重叠的区域、以及与栅极电极gl1及连接电极ztco的任一图案均不重叠的区域。针对各像素设置开口pcon。详细而言,开口pcon设于与像素电极ptco1重叠的区域。像素电极ptco1在布线w1-1和布线w1-2之间与栅极电极gl1的一部分、氧化物半导体层os的一部分、以及连接电极ztco重叠。由此,像素电极ptco1在开口pcon(第二触点区域con2)与连接电极ztco相接。

[0071]

像素电极ptco1延伸至下述透光区域。就上述的构成而言,像素电极ptco1与氧化物半导体层os及布线w1-1(第一布线)同样地形成为沿d2方向延伸的条状。在d1方向上,设有开口pcon的部分上的像素电极ptco1的宽度大于氧化物半导体层os的宽度。

[0072]

如图11所示,连接电极ztco形成为沿布线w1-1延伸的条状。在d1方向上,构成第二触点区域con2的开口pcon的宽度大于连接电极ztco的宽度。在俯视观察时,连接电极ztco整体与像素电极ptco1重叠。

[0073]

如图11所示,像素电极ptco1沿d2方向排列。有时将在d2方向上邻接的像素中的一个像素称为“第一像素”,将另一个像素称为“第二像素”。例如,第一像素是与图11中沿d2方向排列的像素电极ptco1中的上面的像素电极ptco1对应的像素,第二像素是与沿d2方向排列的像素电极ptco1中的下面的像素电极ptco1对应的像素。在该情况下,从布线w1-1向第一像素及第二像素提供像素信号。

[0074]

另外,像素电极ptco1沿d1方向排列。将与上述第一像素在d1方向上邻接的像素称为“第三像素”,将与第二像素在d1方向上邻接的像素称为“第四像素”。第三像素和第四像素在d2方向上邻接。从与布线w1-1相邻的布线w1-2(第二布线)向第三像素及第四像素提供像素信号。

[0075]

如上所述,第一像素、第二像素、第三像素、以及第四像素分别具有晶体管tr1(像素晶体管)、连接电极ztco、以及像素电极ptco1。

[0076]

晶体管tr1具备氧化物半导体层os、与氧化物半导体层os对置的栅极电极gl1、及

氧化物半导体层os和栅极电极gl1之间的栅极绝缘层gi1。在俯视观察时,连接电极ztco与栅极电极gl1及氧化物半导体层os重叠,且在与栅极电极gl1不重叠的开口zcon(第一触点区域con1)处与氧化物半导体层os相接。在俯视观察时,像素电极ptco1与栅极电极gl1、氧化物半导体层os及连接电极ztco重叠,且在与栅极电极gl1重叠的开口pcon(第二触点区域con2)处与连接电极ztco连接。

[0077]

在俯视观察时,设于图11的上侧的第一像素的像素电极ptco1与该第一像素的氧化物半导体层os及设于第一像素的下侧的第二像素的氧化物半导体层os重叠。另外,在俯视观察时,第一像素的像素电极ptco1也与第四像素的氧化物半导体层os的一部分重叠。

[0078]

如图12所示,公用辅助电极cmtl以围绕像素区域的周围的方式设为网格状。即,公用辅助电极cmtl针对多个像素公用地设置,并以限定多个像素各自的区域的方式设置。换而言之,公用辅助电极cmtl具有与各像素(透光区域)对应的开口op。开口op以露出像素电极ptco1的方式设置。开口acon设于公用辅助电极cmtl的开口op的下端附近。设有开口op的区域相当于显示区域。即,开口zcon(第一触点区域con1)及开口acon(第三触点区域con3)包括在开口区域中。开口区域表示通过透射来自基板sub的下方的光(例如背光)而有助于图像显示的区域。另一方面,例如通过金属层遮光而不透过上述光的区域不包括在开口区域中。有时将上述开口区域称为“透光区域”。

[0079]

如图13所示,公用电极ctco针对多个像素公用地设置。在本实施方式中,公用电极ctco针对沿d1方向排列的像素(或像素电极ptco1)公用地设置。即,公用电极ctco在d1方向上具有长边,并沿d2方向排列。在d2方向上邻接的公用电极ctco之间设有狭缝sl。在俯视观察时,狭缝sl与开口acon重叠。换而言之,在俯视观察时,在开口acon处,从绝缘层pil1及pil2露出的像素电极ptco1也从公用电极ctco露出。参考图12及图13,在俯视观察时,在与公用辅助电极cmtl不重叠的区域中,像素电极ptco1与公用电极ctco不重叠。被狭缝sl上下分离的公用电极ctco(参见图13)通过设置为网格状的公用辅助电极cmtl(参考图12)而电连接。

[0080]

如图14所示,针对各像素设置像素电极ptco2。即,像素电极ptco1和像素电极ptco2成对设置。在俯视观察时,像素电极ptco2与开口pcon及开口acon重叠。即,像素电极ptco2在俯视观察时在与开口pcon重叠的区域与公用电极ctco对置,在俯视观察时在与开口acon重叠的区域中与像素电极ptco1相接。

[0081]

参考图12及图14,在俯视观察时,在与公用辅助电极cmtl不重叠的区域中,像素电极ptco2与公用电极ctco重叠。在像素电极ptco2,从沿d2方向延伸的第一边ed1侧朝向与第一边ed1相反的一侧的第二边ed2侧,设有一个或多个切口ct。

[0082]

在本实施方式中,在d2方向上,像素电极ptco2上设有两个切口ct。该构成使像素电极ptco2呈现出设于第一边ed1侧的矩形部分和设于第二边ed2侧的矩形部分通过臂部arm与中央部cent相连而成的形状。换而言之,该臂部arm设于与切口ct对应的位置。进一步换而言之,在d1方向上,该臂部arm略微向形成该切口ct的一侧的相反侧(d1方向的反方向)突出。

[0083]

关于上述方面,在观看d1方向上邻接的两个像素电极ptco2时,臂部arm具备朝向邻接的像素电极ptco2的切口ct略微突出的凸部conv。在俯视观察时,该凸部conv与公用辅助电极cmtl重叠。有时将上述凸部conv称为架桥。有时将在d2方向上邻接的一对凸部conv

称为一对架桥。由该一对架桥(一对凸部conv)形成的若干凹部conc与邻接的像素电极ptco2的中央部cent对置。通过上述的构成,沿着切口ct的边缘部,在像素电极ptco2的上方形成横向的电场。如上所述,通过形成架桥的凸部及凹部,能够提高液晶分子的响应速度。

[0084]

[1-5.显示装置10的各部件的材质]

[0085]

作为基板sub,可以使用玻璃基板、石英基板及蓝宝石基板等具有透光性但不具有柔性的刚性基板。另一方面,在基板sub需要具有柔性的情况下,作为基板sub,能够使用聚酰亚胺基板、丙烯酸基板、硅氧烷基板或氟系树脂基板等包含树脂且具有柔性的柔性基板。为了提高基板sub的耐热性,也可以向上述树脂中导入杂质。

[0086]

作为栅极电极gl1、gl2、布线w1、w2、遮光层ls、及公用辅助电极cmtl,能够使用普通的金属材料。例如,作为以上电极等部件,使用例如:铝(al)、钛(ti)、铬(cr)、钴(co)、镍(ni)、钼(mo)、铪(hf)、钽(ta)、钨(w)、铋(bi)、及银(ag)、或它们的合金或化合物。作为上述电极等部件,上述材料可以以单层使用,也可以层叠后使用。

[0087]

例如,作为栅极电极gl1,使用ti/al/ti的层叠结构。在本实施方式中,具有上述层叠结构的栅极电极gl1的图案端部的剖面形状为正锥形的形状。

[0088]

作为栅极绝缘层gi1、gi2及绝缘层il1~il5、pil1~pil2,能够使用普通的绝缘层性材料。例如,作为绝缘层il1~il3、il5、pil1~pil2,能够使用氧化硅(sio

x

)、硅氧氮化物(sio

x

ny)、氮化硅(sin

x

)、氮氧化硅(sin

x

oy)、氧化铝(alo

x

)、铝氧氮化物(alo

x

ny)、氮氧化铝(aln

x

oy)、氮化铝(aln

x

)等无机绝缘层。作为这些绝缘层,能够使用缺陷较少的绝缘层。

[0089]

上述sio

x

ny及alo

x

ny是含有比率比氧(o)更少(x》y)的氮(n)的硅化合物及铝化合物。另外,sin

x

oy及aln

x

oy是含有比率比氮更少(x》y)的氧的硅化合物及铝化合物。

[0090]

作为绝缘层il4,能够使用聚酰亚胺树脂、丙烯酸树脂、环氧树脂、有机硅树脂、氟系树脂、或硅氧烷树脂等有机绝缘材料。需要说明的是,作为栅极绝缘层gi1、gi2及绝缘层il1~il3、il5,可以使用上述有机绝缘材料。作为上述绝缘层等部件,上述材料可以以单层使用,也可以层叠后使用。

[0091]

作为上述绝缘层的例子,能够使用厚度为100nm的sio

x

作为栅极绝缘层gi1。使用总厚度为600nm~700nm的sio

x

/sin

x

/sio

x

作为绝缘层il1。使用总厚度为60~100nm的sio

x

/sin

x

作为栅极绝缘层gi2。使用总厚度为300nm~500nm的sio

x

/sin

x

/sio

x

作为绝缘层il2。使用总厚度为200nm~500nm的sio

x

(单层)、sin

x

(单层)、或它们的层叠作为绝缘层il3。使用厚度为2μm~4μm的有机层作为绝缘层il4。使用厚度为50nm~150nm的sin

x

(单层)作为绝缘层pil1~pil2。

[0092]

作为氧化物半导体层os,能够使用具有半导体特性的氧化金属。氧化物半导体层os具有透光性。能够使用例如包含铟(in)、镓(ga)、锌(zn)、及氧(o)的氧化物半导体。特别是,能够使用具有in:ga:zn:o=1:1:1:4的组成比的氧化物半导体。其中,本实施方式中使用的包含in、ga、zn、及o的氧化物半导体并不限定于上述组成,也可以使用与上述不同的组成的氧化物半导体。例如,为了提高迁移性,可以使in的比率大于上述比率。另外,为了增大带隙,减少光照的影响,可以使ga的比率大于上述比率。

[0093]

还可以向包含in、ga、zn及o的氧化物半导体中添加其它元素。例如,可以向该氧化物半导体中添加al、sn等金属元素。除上述氧化物半导体以外,还可以使用包含in及ga的氧化物半导体(igo)、包含in及zn的氧化物半导体(izo)、包含in、sn及zn的氧化物半导体

(itzo)、以及包含in及w的氧化物半导体等作为氧化物半导体层os。氧化物半导体层os可以为非晶性,还可以为结晶性。氧化物半导体层os还可以为非晶和结晶的混相。

[0094]

作为连接电极ztco、像素电极ptco1、ptco2、及公用电极ctco,使用透明导电层。作为该透明导电层,能够使用氧化铟及氧化锡的混合物(ito)及氧化铟及氧化锌的混合物(izo)。作为该透明导电层,还可以使用除上述以外的材料。

[0095]

综上所述,根据本实施方式所涉及的显示装置10,可以在选择晶体管(晶体管tr1)的上方层叠像素电路的保持电容(第一电容元件cap1及第二电容元件cap2)。其结果,能够形成面积较小且具有更大电容的电容元件。因此,即使是像素尺寸缩小化的显示装置,也能够实现稳定的显示动作。

[0096]

并且,通过使晶体管tr1的氧化物半导体层os和连接电极ztco直接接触,能够确保两者之间导通。因此,无需在氧化物半导体层os和连接电极ztco之间设置金属层。通过该构成,即使在为了在开口zcon(第一触点区域con1)处不遮光而将开口zcon设于显示区域的情况下,也能够抑制开口率的降低。氧化物半导体层具有透光性。因此,在本实施方式中,虽然在像素区域中的开口区域设有氧化物半导体层,但从背光射入基板sub的光通过该氧化物半导体层。因此,尽可能减少因氧化物半导体层设于开口区域所导致的该开口区域的透射率的降低。氧化物半导体层os具有透光性,所以与硅层不同,不易使透射光产生不均。通过在显示区域中设置氧化物半导体层os,能够抑制显示不均的产生。

[0097]

[2.第二实施方式]

[0098]

使用图15~图17,对上述第一种实施方式中所说明的显示装置的整体构成进行说明。

[0099]

[2-1.显示装置20的概要]

[0100]

图15是示出本发明的一种实施方式所涉及的显示装置的概要的俯视图。如图15所示,显示装置20具有阵列基板300、密封部400、对置基板500、柔性印刷电路基板600(fpc600)、及ic芯片700。阵列基板300及对置基板500通过密封部400贴合。在由密封部400围成的显示区域22中,以矩阵状配置有多个像素电路310。显示区域22中设有多个像素电路且有助于图像显示的部分是显示区域。另外,显示区域是在俯视观察时与后述的液晶元件410重叠的区域。另外,将包围显示区域的区域称为周边区域。上述晶体管tr1(第一晶体管)设于液晶区域22b(显示区域)。

[0101]

显示装置20在周边区域具备设有密封部400的密封区域24。显示区域22由密封区域24包围。fpc600设于作为周边区域的一部分的端子区域26。端子区域26形成于阵列基板300中与对置基板500不重叠的区域。ic芯片700设于fpc600上。ic芯片700提供用于驱动各像素电路310的信号。密封区域24或密封区域24与端子区域26合并而成的区域是包围显示区域22的区域。有时将这些区域称为“边框区域”。上述晶体管tr2(第二晶体管)设于该边框区域。

[0102]

[显示装置20的电路构成]

[0103]

图16是示出本发明的一种实施方式所涉及的显示装置的电路构成的框图。如图16所示,针对周边区域中配置有像素电路310的显示区域22,在沿d2方向(列方向)邻接的位置上设有源极驱动电路320。另外,针对周边区域中的显示区域22,在沿d1方向(行方向)邻接的位置上设有栅极驱动电路330。源极驱动电路320及栅极驱动电路330可以重叠设于上述

密封区域24。其中,设置源极驱动电路320及栅极驱动电路330的区域并不限定于密封区域24,只要为设有像素电路310的区域的外侧(周边区域)即可,可以为任意区域。

[0104]

源极布线321从源极驱动电路320沿d2方向延伸,并与沿d2方向排列的多个像素电路310连接。栅极布线331从栅极驱动电路330沿d1方向延伸,并与沿d1方向排列的多个像素电路310连接。

[0105]

端子区域26内设有端子部333。端子部333和源极驱动电路320通过连接布线341连接。同样地,端子部333和栅极驱动电路330通过连接布线341连接。通过fpc600连接于端子部333,连接有fpc600的外部设备和显示装置20连接,通过来自外部设备的信号驱动设于显示装置20的各像素电路310。

[0106]

第一种实施方式所示的晶体管tr1用于像素电路310。第一种实施方式所示的晶体管tr2用于源极驱动电路320及栅极驱动电路330中所包括的晶体管。

[0107]

[显示装置20的像素电路310]

[0108]

图17是示出本发明的一种实施方式所涉及的显示装置的像素电路的电路图。如图17所示,像素电路310包括晶体管800、保持电容890及液晶元件410等元件。保持电容890包括第一电容元件cap1及第二电容元件cap2。第一电容元件cap1的晶体管800侧的电极为像素电极ptco1。第二电容元件cap2的晶体管800侧的电极为像素电极ptco2。第一电容元件cap1及第二电容元件cap2的gnd电位侧的电极为公用电极ctco。

[0109]

液晶元件410的一个(晶体管800侧)电极为像素电极ptco2,另一个电极为公用电极ctco。晶体管800具有第一栅极电极810、第一源极电极830及第一漏极电极840。第一栅极电极810连接于栅极布线331。第一源极电极830连接于源极布线321。第一漏极电极840连接于保持电容890及液晶元件410。第一种实施方式所示的晶体管tr1适用于图17所示的晶体管800。需要说明的是,在本实施方式中,为了方便说明,将830称为源极电极,将840称为漏极电极,每个电极作为源极的功能和作为漏极的功能可以进行替换。

[0110]

上面作为本发明的实施方式所述的各实施方式只要彼此不矛盾,则能够适当组合实施。另外,只要具备本发明的精神,则本领域技术人员可以基于各实施方式的显示装置适当进行组件添加、删除或设计变更、或工序的添加、省略或者条件変更,这些也包含在本发明的范围内。

[0111]

关于与上述的各实施方式的方案所带来的作用效果不同的其它作用效果,只要是由本说明书的记载可以明确的、或本领域技术人员容易想到的,则当然也可以理解为它们是由本发明带来的。

[0112]

附图标记说明

[0113]

10:显示装置;20:显示装置;22:显示区域;24:密封区域;26:端子区域;300:阵列基板;310:像素电路;320:源极驱动电路;321:源极布线;330:栅极驱动电路;331:栅极布线;333:端子部;341:连接布线;400:密封部;410:液晶元件;500:对置基板;600:柔性印刷电路基板;700:芯片;800:晶体管;810:第一栅极电极;830:第一源极电极;840:第一漏极电极;890:保持电容;cmtl:公用辅助电极;con1:第一触点区域;con2:第二触点区域;ctco:公用电极;gi1、gi2:栅极绝缘层;gl1、gl2:栅极电极;il1~il5:绝缘层;ls:遮光层;op:开口;os:氧化物半导体层;acon、pcon、wcon、zcon:开口;pjt:突出部;ptco1、ptco2:像素电极;s:半导体层;sl:狭缝;sp:间隔物;sub:基板;tr1、tr2:晶体管;w:布线;ztco:连接电极。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1