逆变器的制作方法

1.本发明涉及一种逆变器。

背景技术:

2.逆变器是一种能够把直流电转变为交流电的装置。常见的逆变器包括n型逆变器以及p型逆变器,其中n型逆变器包括n型晶体管,而p型逆变器则包括p型晶体管。

3.目前,硅半导体材料常被用于制作电源装置中使用的晶体管。在逆变器的一些应用中,通常会包括一个或多个nmos晶体管或pmos晶体管。金属氧化物半导体材料(例如铟镓锌氧化物)具有容易大面积制造与工艺温度低的优点,因此,近几年许多厂商致力于以金属氧化物半导体材料取代硅半导体材料作为晶体管的通道。然而,要如何将金属氧化物半导体材料应用于逆变器中仍然是许多厂商致力于发展的课题。

技术实现要素:

4.本发明提供一种逆变器,具有面积小的优点。

5.本发明的至少一实施例提供一种逆变器。逆变器包括基板、第一薄膜晶体管以及第二薄膜晶体管。第一薄膜晶体管以及第二薄膜晶体管位于基板之上。第一薄膜晶体管包括第一栅极、第一半导体结构、第一源极以及第一漏极。第一半导体结构包括第一源极区、第一漏极区以及位于第一源极区与第一漏极区之间的第一通道区。第一栅极重叠于第一通道区。第一源极区的厚度大于第一通道区的厚度以及第一漏极区的厚度。第一源极电性连接第一源极区。第一漏极电性连接第一漏极区以及第一栅极。第二薄膜晶体管包括第二栅极、第二半导体结构、第二源极以及第二漏极。第二半导体结构包括第二源极区、第二漏极区以及位于第二源极区与第二漏极区之间的第二通道区。第二栅极重叠于第二通道区。第二通道区的厚度大于第二源极区的厚度以及第二漏极区的厚度。第二源极电性连接第二源极区。第二漏极电性连接第二漏极区以及第一源极。

6.本发明的至少一实施例提供一种逆变器。逆变器包括基板、第一薄膜晶体管以及第二薄膜晶体管。第一薄膜晶体管以及第二薄膜晶体管位于基板之上。第一薄膜晶体管包括第一栅极、第一半导体结构、第一源极以及第一漏极。第一半导体结构包括第一源极区、第一漏极区以及位于第一源极区与第一漏极区之间的第一通道区。第一栅极重叠于第一通道区。第一通道区的厚度大于第一源极区的厚度以及第一漏极区的厚度。第一源极电性连接第一源极区以及第一栅极。第一漏极电性连接第一漏极区。第二薄膜晶体管包括第二栅极、第二半导体结构、第二源极以及第二漏极。第二半导体结构包括第二源极区、第二漏极区以及位于第二源极区与第二漏极区之间的第二通道区。第二栅极重叠于第二通道区,且第二源极区的厚度大于第二通道区的厚度以及第二漏极区的厚度。第二源极电性连接第二源极区。第二漏极电性连接第二漏极区以及第一源极。

附图说明

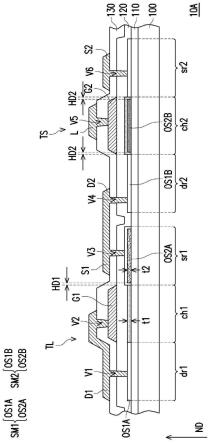

7.图1是依照本发明的一实施例的一种逆变器的剖面示意图。

8.图2a至图2d是图1的逆变器的制造方法的剖面示意图。

9.图3是依照本发明的一实施例的一种逆变器的剖面示意图。

10.图4a至图4d是图3的逆变器的制造方法的剖面示意图。

11.图5是依照本发明的一实施例的一种逆变器的剖面示意图。

12.图6是依照本发明的一实施例的一种逆变器的剖面示意图。

13.图7a是依照本发明的一实施例的一种逆变器的电路示意图。

14.图7b是图7a的逆变器的输出电压与输入电压的示意图。

15.图8a是依照本发明的一实施例的一种逆变器的电路示意图。

16.图8b是图8a的逆变器的输出电压与输入电压的示意图。

17.附图标记说明:

18.10a,10b,10c,10d:逆变器

19.100:基板

20.110:缓冲层

21.120:栅介电层

22.130:层间介电层

23.tl:第一薄膜晶体管

24.ts:第二薄膜晶体管

25.ch1:第一通道区

26.ch2:第二通道区

27.d1第一漏极

28.d2第二漏极

29.dr1:第一漏极区

30.dr2:第二漏极区

31.g1:第一栅极

32.g2:第二栅极

33.hd1,hd2:水平距离

34.l:信号线

35.nd:法线方向

36.os1a,os1a’:第一金属氧化物层

37.os1b,os1b’:第二金属氧化物层

38.os2a,os2a’:第一金属氧化物图案

39.os2b:第二金属氧化物图案

40.r

l

,rs:等效阻值

41.s1:第一源极

42.s2:第二源极

43.sm1:第一半导体结构

44.sm2:第二半导体结构

45.sr1:第一源极区

46.sr2:第二源极区

47.t1,t2:厚度

48.v1:第一接触孔

49.v2:第二接触孔

50.v3:第三接触孔

51.v4:第四接触孔

52.v5:第五接触孔

53.v6:第六接触孔

[0054]vdd

:电压

[0055]vin

:输入电压

[0056]vout

:输出电压

[0057]

gnd:接地电压

具体实施方式

[0058]

图1是依照本发明的一实施例的一种逆变器的剖面示意图。

[0059]

请参考图1,逆变器10a包括基板100、第一薄膜晶体管tl及第二薄膜晶体管ts。

[0060]

基板100的材质可为玻璃、石英、有机聚合物或是不透光/反射材料(例如:导电材料、金属、晶圆、陶瓷或其他可适用的材料)或是其他可适用的材料。若使用导电材料或金属时,则在基板100上覆盖一层绝缘层(未示出),以避免短路问题。在一些实施例中,基板100为柔性基板,且基板100的材料例如为聚乙烯对苯二甲酸酯(polyethylene terephthalate,pet)、聚二甲酸乙二醇酯(polyethylene naphthalate,pen)、聚酯(polyester,pes)、聚甲基丙烯酸甲酯(polymethylmethacrylate,pmma)、聚碳酸酯(polycarbonate,pc)、聚酰亚胺(polyimide,pi)或金属软板(metal foil)或其他柔性材质。

[0061]

缓冲层110位于基板100上,缓冲层110为单层或多层结构,且缓冲层110的材料可以包括氧化硅、氮氧化硅或其他合适的材料或上述材料的堆叠层。

[0062]

第一薄膜晶体管tl以及第二薄膜晶体管ts位于基板100之上。在本实施例中,第一薄膜晶体管tl以及第二薄膜晶体管ts位于缓冲层110上。

[0063]

第一薄膜晶体管tl包括第一栅极g1、第一半导体结构sm1、第一源极s1以及第一漏极d1。第二薄膜晶体管ts包括第二栅极g2、第二半导体结构sm2、第二源极s2以及第二漏极d2。

[0064]

第一半导体结构sm1位于缓冲层110上。第一半导体结构sm1包括第一源极区sr1、第一漏极区dr1以及位于第一源极区sr1与第一漏极区dr1之间的第一通道区ch1。第一源极区sr1的厚度(例如为厚度t2加上厚度t1)大于第一通道区ch1的厚度(例如为厚度t1)以及第一漏极区dr1的厚度(例如为厚度t1)。

[0065]

第一半导体结构sm1包括第一金属氧化物层os1a以及第一金属氧化物图案os2a的堆叠。第一金属氧化物层os1a设置于第一源极区sr1、第一漏极区dr1以及第一通道区ch1中。第一金属氧化物图案os2a设置于第一源极区sr1中。第一金属氧化物图案os2a未延伸至

第一漏极区dr1以及第一通道区ch1。在本实施例中,第一金属氧化物层os1a包覆第一金属氧化物图案os2a的侧壁与顶面,且第一金属氧化物图案os2a位于第一金属氧化物层os1a与基板100之间。

[0066]

第二半导体结构sm2包括第二源极区sr2、第二漏极区dr2以及位于第二源极区sr2与第二漏极区dr2之间的第二通道区ch2。第二通道区ch2的厚度(例如为厚度t2加上厚度t1)大于第二源极区sr2的厚度(例如为厚度t1)以及第二漏极区dr2的厚度(例如为厚度t1)。

[0067]

第二半导体结构sm2包括第二金属氧化物层os1b以及第二金属氧化物图案os2b的堆叠。第二金属氧化物层os1b设置于第二源极区sr2、第二漏极区dr2以及第二通道区ch2中。第二金属氧化物图案os2b设置于第二通道区ch2中。第二金属氧化物图案os2b未延伸至第二源极区sr2以及第二漏极区dr2。在本实施例中,第二金属氧化物层os1b包覆第二金属氧化物图案os2b的侧壁与顶面,且第二金属氧化物图案os2b位于第二金属氧化物层os1b与基板100之间。

[0068]

在一些实施例中,第一金属氧化物图案os2a与第二金属氧化物图案os2b属于相同膜层。换句话说,第一金属氧化物图案os2a与第二金属氧化物图案os2b是于同一次图案化工艺中所定义出来的。第一金属氧化物图案os2a与第二金属氧化物图案os2b包括相同的厚度与相同的材料。在一些实施例中,第一金属氧化物图案os2a与第二金属氧化物图案os2b的厚度t2为5纳米至25纳米。在一些实施例中,第一金属氧化物图案os2a与第二金属氧化物图案os2b的材料包括铟钨锌氧化物、铟镓锌氧化物或其他金属氧化物。在一些实施例中,第一金属氧化物图案os2a经掺杂而具有低于第二金属氧化物图案os2b的电阻率。

[0069]

在一些实施例中,第一金属氧化物层os1a与第二金属氧化物层os1b属于相同膜层。换句话说,第一金属氧化物层os1a与第二金属氧化物层os1b是于同一次图案化工艺中所定义出来的。第一金属氧化物层os1a与第二金属氧化物层os1b包括相同的厚度与相同的材料。在一些实施例中,第一金属氧化物层os1a与第二金属氧化物层os1b的厚度t1为15纳米至25纳米。在一些实施例中,第一金属氧化物层os1a与第二金属氧化物层os1b的材料包括铟镓锌氧化物或其他金属氧化物。在一些实施例中,在第一金属氧化物层os1a中,第一漏极区dr1以及第一源极区dr1经掺杂而具有低于第一通道区ch1的电阻率。类似地,在第二金属氧化物层os1b中,第二漏极区dr2以及第二源极区dr2经掺杂而具有低于第二通道区ch2的电阻率。另外,在第二通道区ch2中,第二金属氧化物图案os2b的载子迁移率大于或等于第二金属氧化物层os1b的载子迁移率。

[0070]

基于上述,通过于第二通道区ch2中设置第二金属氧化物图案os2b,可以降低第二薄膜晶体管ts的等效阻值rs,因此,不需要增加第一薄膜晶体管tl的第一通道区ch1的长度就可以提升第一薄膜晶体管tl的等效阻值r

l

与第二薄膜晶体管ts的等效阻值rs的比值(r

l

/rs),使逆变器10a具有面积小的优点。

[0071]

栅介电层120位于第一半导体结构sm1与第二半导体结构sm2之上。在本实施例中,栅介电层120直接形成于第一半导体结构sm1与第二半导体结构sm2上。在一些实施例中,栅介电层120的材料包括氧化硅、氮氧化硅、氧化铪或其他合适的材料或上述材料的堆叠层。

[0072]

第一栅极g1与第二栅极g2位于栅介电层120之上。在本实施例中,第一栅极g1与第二栅极g2直接形成于栅介电层120上。第一栅极g1在基板100的上表面的法线方向nd上重叠

于第一通道区ch1。第二栅极g2在基板100的上表面的法线方向nd上重叠于第二通道区ch2。在一些实施例中,第一金属氧化物图案os2a的侧壁与第一栅极g1的侧壁之间的水平距离hd1小于300纳米,且第二金属氧化物图案os2b的侧壁与第二栅极g2的侧壁之间的水平距离hd2小于300纳米。

[0073]

在一些实施例中,第一栅极g1与第二栅极g2的材料可包括金属,例如铬(cr)、金(au)、银(ag)、铜(cu)、锡(sn)、铅(pb)、铪(hf)、钨(w)、钼(mo)、钕(nd)、钛(ti)、钽(ta)、铝(al)、锌(zn)或上述金属的任意组合的合金或上述金属及/或合金的叠层,但本发明不以此为限。第一栅极g1与第二栅极g2也可以使用其他导电材料,例如:金属的氮化物、金属的氧化物、金属的氮氧化物、金属与其它导电材料的堆叠层或是其他具有导电性质的材料。

[0074]

层间介电层130位于第一栅极g1、第二栅极g2以及栅介电层120之上。在一些实施例中,层间介电层130的材料包括氮化硅、氧化硅、氮氧化硅、氧化铪或其他合适的材料或上述材料的堆叠层。

[0075]

层间介电层130具有第一接触孔v1、第二接触孔v2、第三接触孔v3、第四接触孔v4、第五接触孔v5以及第六接触孔v6。在本实施例中,第一接触孔v1、第三接触孔v3、第四接触孔v4以及第六接触孔v6贯穿层间介电层130以及栅介电层120,而第二接触孔v2以及第五接触孔v5贯穿层间介电层130。

[0076]

第一源极s1、第一漏极d1、第二源极s2、第二漏极d2以及信号线l位于层间介电层130上。第一漏极d1填入第一接触孔v1以电性连接第一漏极区dr1,且第一漏极d1填入第二接触孔v2以电性连接该第一栅极g1。第一源极s1填入第三接触孔v3以电性连接第一源极区sr1。第二漏极d2填入第四接触孔v4以电性连接第二漏极区dr2,且第二漏极d2电性连接第一源极s1。信号线l填入第五接触孔v5以电性连接第二栅极g2。第二源极s2填入第六接触孔v6以电性连接第二源极区sr2。

[0077]

在本实施例中,由于第一金属氧化物图案os2a的设置,第一源极区sr1具有较低的电阻率,借此减少第一源极s1与第一源极区sr1之间的阻抗。另外,通过于第一源极区sr1中设置第一金属氧化物图案os2a,第一源极区sr1的厚度大于第一通道区ch1的厚度,可以分散第一通道区ch1与第一源极s1之间的电场,借此降低第一源极s1与第一金属氧化物图案os2a的接触阻抗。此外,通过于第二通道区ch2中设置第二金属氧化物图案os2b,第二通道区ch1的厚度大于第二漏极区dr2的厚度,可以分散第二漏极d2与第二通道区ch2之间的电场,借此减少热载子效应。

[0078]

图2a至图2d是图1的逆变器的制造方法的剖面示意图。

[0079]

请参考图2a,形成第一金属氧化物图案os2a’与第二金属氧化物图案os2b于基板100之上。在一些实施例中,形成第一金属氧化物图案os2a’与第二金属氧化物图案os2b的方法包括光刻蚀刻工艺。第一金属氧化物图案os2a’与第二金属氧化物图案os2b属于相同膜层,且第一金属氧化物图案os2a’与第二金属氧化物图案os2b包括相同的材料与相同的厚度。

[0080]

请参考图2b,形成第一金属氧化物层os1a’与第二金属氧化物层os1b’于第一金属氧化物图案os2a’、第二金属氧化物图案os2b以及基板100之上,其中第一金属氧化物层os1a’覆盖第一金属氧化物图案os2a’,且第二金属氧化物层os1b’覆盖第二金属氧化物图案os2b。在一些实施例中,形成第一金属氧化物层os1a’与第二金属氧化物层os1b’的方法

包括光刻蚀刻工艺。

[0081]

举例来说,形成毯覆于第一金属氧化物图案os2a’、第二金属氧化物图案os2b以及缓冲层110上的金属氧化物材料层(未绘出);于金属氧化物材料层表面形成图案化的光刻胶(未绘出);以图案化的光刻胶为遮罩蚀刻金属氧化物材料层,以形成第一金属氧化物层os1a’与第二金属氧化物层os1b’;移除图案化的光刻胶。第一金属氧化物层os1a’与第二金属氧化物层os1b’属于相同膜层,且第一金属氧化物层os1a’与第二金属氧化物层os1b’包括相同的材料与相同的厚度。

[0082]

在本实施例中,由于第一金属氧化物层os1a’覆盖第一金属氧化物图案os2a’,且第二金属氧化物层os1b’覆盖第二金属氧化物图案os2b,蚀刻金属氧化物材料层时所用的蚀刻液不会对第一金属氧化物图案os2a’以及第二金属氧化物图案os2b的表面造成损伤,借此提升半导体结构的良率。

[0083]

请参考图2b与2c,形成栅介电层120于第一金属氧化物层os1a’与第二金属氧化物层os1b’上。形成第一栅极g1与第二栅极g2于栅介电层120上。以第一栅极g1与第二栅极g2为掩模,执行掺杂工艺p,以形成包括第一源极区sr1、第一漏极区dr1以及第一通道区ch1的第一半导体结构sm1以及包括第二源极区sr2、第二漏极区dr2以及第二通道区ch2的第二半导体结构sm2。在本实施例中,由于第一金属氧化物图案os2a未被栅极遮蔽,第一金属氧化物图案os2a经掺杂而具有低于第二金属氧化物图案os2b的电阻率。在一些实施例中,掺杂工艺p例如为氢等离子体掺杂或其他合适的工艺。

[0084]

请参考图2d,形成层间介电层130于第一栅极g1、第二栅极g2以及栅介电层120之上。于层间介电层130中形成第一接触孔v1至第六接触孔v6。

[0085]

最后请回到图1,形成第一源极s1、第一漏极d1、第二源极s2、第二漏极d2以及信号线l位于层间介电层130上。在本实施例中,第一源极s1以及第一漏极d1连接至第一金属氧化物层os1a,而第二源极s2以及第二漏极d2连接至第二金属氧化物层os1b。至此,逆变器10a大致完成。

[0086]

图3是依照本发明的一实施例的一种逆变器的剖面示意图。在此必须说明的是,图3的实施例沿用图1的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

[0087]

图3的逆变器10b与图1的半导体装置10a的主要差异在于:逆变器10b的第一金属氧化物层os1a位于第一金属氧化物图案os2a与基板100之间,且第二金属氧化物层os1b位于第二金属氧化物图案os2b与基板100之间。

[0088]

图4a至图4d是图3的逆变器的制造方法的剖面示意图。

[0089]

请参考图4a,形成第一金属氧化物层os1a’与第二金属氧化物层os1b’于基板100之上。在一些实施例中,形成第一金属氧化物层os1a’与第二金属氧化物层os1b’的方法包括光刻蚀刻工艺。第一金属氧化物层os1a’与第二金属氧化物层os1b’属于相同膜层,且第一金属氧化物层os1a’与第二金属氧化物层os1b’包括相同的材料与相同的厚度。

[0090]

请参考图2b,形成第一金属氧化物图案os2a’与第二金属氧化物图案os2b于第一金属氧化物层os1a’与第二金属氧化物层os1b’之上,其中第一金属氧化物图案os2a’暴露出第一金属氧化物层os1a’的部分上表面,且第二金属氧化物图案os2b暴露出第二金属氧

化物层os1b’的部分上表面。在一些实施例中,形成第一金属氧化物图案os2a’与第二金属氧化物图案os2b的方法包括光刻蚀刻工艺。

[0091]

举例来说,形成毯覆于第一金属氧化物层os1a’、第二金属氧化物层os1b’以及缓冲层110上的金属氧化物材料层(未绘出);于金属氧化物材料层表面形成图案化的光刻胶(未绘出);以图案化的光刻胶为遮罩蚀刻金属氧化物材料层,以形成第一金属氧化物图案os2a’与第二金属氧化物图案os2b;移除图案化的光刻胶。第一金属氧化物图案os2a’与第二金属氧化物图案os2b属于相同膜层,且第一金属氧化物图案os2a’与第二金属氧化物图案os2b包括相同的材料与相同的厚度。

[0092]

请参考图4b与4c,形成栅介电层120于第一金属氧化物层os1a’、第二金属氧化物层os1b’、第一金属氧化物图案os2a’与第二金属氧化物图案os2b上。形成第一栅极g1与第二栅极g2于栅介电层120上。以第一栅极g1与第二栅极g2为掩模,执行掺杂工艺p,以形成包括第一源极区sr1、第一漏极区dr1以及第一通道区ch1的第一半导体结构sm1以及包括第二源极区sr2、第二漏极区dr2以及第二通道区ch2的第二半导体结构sm2。在本实施例中,由于第一金属氧化物图案os2a未被栅极遮蔽,第一金属氧化物图案os2a经掺杂而具有低于第二金属氧化物图案os2b的电阻率。在一些实施例中,掺杂工艺p例如为氢等离子体掺杂或其他合适的工艺。

[0093]

请参考图4d,形成层间介电层130于第一栅极g1、第二栅极g2以及栅介电层120之上。于层间介电层130中形成第一接触孔v1至第六接触孔v6。

[0094]

最后请回到图3,形成第一源极s1、第一漏极d1、第二源极s2、第二漏极d2以及信号线l位于层间介电层130上。在本实施例中,第一源极s1连接至第一金属氧化物图案os2a,第一漏极d1连接至第一金属氧化物层os1a,且第二源极s2以及第二漏极d2连接至第二金属氧化物层os1b。至此,逆变器10b大致完成。

[0095]

图5是依照本发明的一实施例的一种逆变器的剖面示意图。在此必须说明的是,图5的实施例沿用图1的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

[0096]

图5的逆变器10c与图1的半导体装置10a的主要差异在于:在逆变器10c中,第一通道区ch1的厚度(例如为厚度t2加上厚度t1)大于第一源极区sr1的厚度(例如为厚度t1)以及第一漏极区dr1的厚度(例如为厚度t1),第二源极区sr2的厚度(例如为厚度t2加上厚度t1)大于第二通道区ch2的厚度(例如为厚度t1)以及第二漏极区dr2的厚度(例如为厚度t1),且第一源极s1电性连接第一栅极g1。

[0097]

请参考图5,第一半导体结构sm1包括第一金属氧化物层os1a以及第一金属氧化物图案os2a的堆叠。第一金属氧化物层os1a设置于第一源极区sr1、第一漏极区dr1以及第一通道区ch1中。第一金属氧化物图案os2a设置于第一通道区ch1中。第一金属氧化物图案os2a未延伸至第一漏极区dr1以及第一源极区sr1。在本实施例中,第一金属氧化物层os1a包覆第一金属氧化物图案os2a的侧壁与顶面,且第一金属氧化物图案os2a位于第一金属氧化物层os1a与基板100之间。

[0098]

第二半导体结构sm2包括第二金属氧化物层os1b以及第二金属氧化物图案os2b的堆叠。第二金属氧化物层os1b设置于第二源极区sr2、第二漏极区dr2以及第二通道区ch2

中。第二金属氧化物图案os2b设置于第二源极区sr2中。第二金属氧化物图案os2b未延伸至第二漏极区dr2以及第二通道区ch2。在本实施例中,第二金属氧化物层os1b包覆第二金属氧化物图案os2b的侧壁与顶面,且第二金属氧化物图案os2b位于第二金属氧化物层os1b与基板100之间。

[0099]

在一些实施例中,第一金属氧化物图案os2a与第二金属氧化物图案os2b属于相同膜层。换句话说,第一金属氧化物图案os2a与第二金属氧化物图案os2b是于同一次图案化工艺中所定义出来的。第一金属氧化物图案os2a与第二金属氧化物图案os2b包括相同的厚度与相同的材料。在一些实施例中,第一金属氧化物图案os2a与第二金属氧化物图案os2b的厚度t2为5纳米至25纳米。在一些实施例中,第一金属氧化物图案os2a与第二金属氧化物图案os2b的材料包括铟钨锌氧化物、铟镓锌氧化物或其他金属氧化物。在一些实施例中,第二金属氧化物图案os2b经掺杂而具有低于第一金属氧化物图案os2a的电阻率。

[0100]

在一些实施例中,第一金属氧化物层os1a与第二金属氧化物层os1b属于相同膜层。换句话说,第一金属氧化物层os1a与第二金属氧化物层os1b是于同一次图案化工艺中所定义出来的。第一金属氧化物层os1a与第二金属氧化物层os1b包括相同的厚度与相同的材料。在一些实施例中,第一金属氧化物层os1a与第二金属氧化物层os1b的厚度t1为15纳米至25纳米。在一些实施例中,第一金属氧化物层os1a与第二金属氧化物层os1b的材料包括铟镓锌氧化物或其他金属氧化物。在一些实施例中,在第一金属氧化物层os1a中,第一漏极区dr1以及第一源极区dr1经掺杂而具有低于第一通道区ch1的电阻率。类似地,在第二金属氧化物层os1b中,第二漏极区dr2以及第二源极区dr2经掺杂而具有低于第二通道区ch2的电阻率。另外,在第一通道区ch1中,第一金属氧化物图案os2a的载子迁移率大于或等于第一金属氧化物层os1a的载子迁移率。

[0101]

在一些实施例中,第一金属氧化物图案os2a的侧壁与第一栅极g1的侧壁之间的水平距离hd1小于300纳米,且第二金属氧化物图案os2b的侧壁与第二栅极g2的一侧壁之间的水平距离hd2小于300纳米。

[0102]

基于上述,通过于第一通道区ch1中设置第一金属氧化物图案os2a,可以降低第一薄膜晶体管tl的等效阻值r

l

,因此,不需要增加第二薄膜晶体管ts的第二通道区ch2的长度就可以减少第一薄膜晶体管tl的等效阻值r

l

与第二薄膜晶体管ts的等效阻值rs的比值(r

l

/rs),使逆变器10c具有面积小的优点。

[0103]

此外,由于第二金属氧化物图案os2b的设置,第二源极区sr2具有较低的电阻率,借此减少第二源极s2与第二源极区sr2之间的阻抗。另外,通过于第二源极区sr2中设置第二金属氧化物图案os2b,第二源极区sr2的厚度大于第二通道区ch2的厚度,可以分散第二通道区ch2与第二源极s2之间的电场,借此降低第二源极s2与第二金属氧化物图案os2b的接触阻抗。此外,通过于第一通道区ch1中设置第一金属氧化物图案os2a,第一通道区ch1的厚度大于第一漏极区dr1的厚度,可以分散第一漏极d1与第一通道区ch1之间的电场,借此减少热载子效应。

[0104]

图6是依照本发明的一实施例的一种逆变器的剖面示意图。在此必须说明的是,图6的实施例沿用图5的实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明。关于省略部分的说明可参考前述实施例,在此不赘述。

[0105]

图6的逆变器10d与图5的半导体装置10c的主要差异在于:逆变器10d的第一金属氧化物层os1a位于第一金属氧化物图案os2a与基板100之间,且第二金属氧化物层os1b位于第二金属氧化物图案os2b与基板100之间。

[0106]

图7a是依照本发明的一实施例的一种逆变器的电路示意图。图7b是图7a的逆变器的输出电压与输入电压的示意图。

[0107]

图7a的逆变器的具体结构可以参考图1的逆变器10a以及图3的逆变器10b,于此不再赘述。

[0108]

第一薄膜晶体管tl2的第一漏极d1电性连接至电压v

dd

。第一薄膜晶体管tl2的第一栅极g1与第一源极s1电性连接至第二薄膜晶体管ts的第二漏极d2,且第一源极s1、第一栅极g1以及第二漏极d2连接至输出电压v

out

。输入电压v

in

通过信号线l连接至第二薄膜晶体管ts的第二栅极g2。第二薄膜晶体管ts的第二源极s2连接至接地电压gnd。

[0109]

在本实施例中,第一薄膜晶体管tl与第二薄膜晶体管ts皆为增强型晶体管。第一薄膜晶体管tl的等效阻值r

l

不同于第二薄膜晶体管ts的等效阻值rs,等效阻值r

l

与等效阻值rs的比值(r

l

/rs)会影响逆变器的特性。当r

l

/rs高时,逆变器适用于处理数字信号(digital signal);当r

l

/rs低时,逆变器适用于处理模拟信号(analog signal)。

[0110]

在本实施例中,通过于第二通道区ch2中设置第二金属氧化物图案os2b(请参考图1与图3),可以降低第二薄膜晶体管ts的等效阻值rs,进而改变r

l

/rs。换句话说,不需要调整第一通道区ch1的长度与宽度或第二通道区ch2的长度与宽度,就可以改变的r

l

/rs,借此调整逆变器的特性。

[0111]

图8a是依照本发明的一实施例的一种逆变器的电路示意图。图8b是图8a的逆变器的输出电压与输入电压的示意图。

[0112]

图8a的逆变器的具体结构可以参考图5的逆变器10c以及图6的逆变器10d,于此不再赘述。

[0113]

第一薄膜晶体管tl2的第一漏极d1电性连接至电压v

dd

。第一薄膜晶体管tl2的第一栅极g1与第一源极s1电性连接至第二薄膜晶体管ts的第二漏极d2,且第一源极s1、第一栅极g1以及第二漏极d2连接至输出电压v

out

。输入电压v

in

通过信号线l连接至第二薄膜晶体管ts的第二栅极g2。第二薄膜晶体管ts的第二源极s2连接至接地电压gnd。

[0114]

在本实施例中,第一薄膜晶体管tl为耗尽型晶体管,而第二薄膜晶体管ts为增强型晶体管。第一薄膜晶体管tl的等效阻值r

l

不同于第二薄膜晶体管ts的等效阻值rs,等效阻值r

l

与等效阻值rs的比值(r

l

/rs)会影响逆变器的特性。当r

l

/rs高时,逆变器适用于处理数字信号,当r

l

/rs低时,逆变器适用于处理模拟信号。

[0115]

在本实施例中,通过于第一通道区ch1中设置第一金属氧化物图案os2a(请参考图5与图6),可以降低第一薄膜晶体管tl的等效阻值r

l

,进而改变r

l

/rs。换句话说,不需要调整第一通道区ch1的长度与宽度或第二通道区ch2的长度与宽度,就可以改变r

l

/rs,借此调整逆变器的特性。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1