半导体器件和制造半导体器件的方法与流程

1.本发明涉及一种半导体器件。本发明还涉及一种制造半导体器件的方法。

背景技术:

2.美国专利us6777800b2中描述了一种已知的无损耗封装(lfpak)半导体器件。半导体管芯安装至具有引线的引线框架。导线将半导体管芯与引线联接。然后,将导线、半导体管芯以及大部分引线框架封装在模制材料中。然后,使模制材料成形。形成的半导体管芯封装包括模制体,该模制体具有从该模制体横向延伸远离的引线。将半导体管芯封装安装至电路板上。

3.随着消费类电子产品(例如,手机、膝上型计算机等)的尺寸持续减小,对更薄的电子设备和更薄的电子部件的需求不断增加。另外,应该使半导体管芯封装的散热特性得到改善。例如,诸如竖直mosfet(金属氧化物场效应晶体管)等功率半导体器件可以产生大量的热量。对于高输出功率应用(例如,大于60瓦),需要特殊封装来移除来自功率晶体管的热量以防止过热。过热还会降低功率晶体管的工作特性。

4.在上述专利中描述的一个实施例中,半导体管芯封装包括:(a)半导体管芯,其包括第一表面、第二表面、以及竖直功率mosfet,所述竖直功率mosfet在第一表面处具有栅极区和源极区并且在第二表面处具有漏极区;(b)漏极夹具,其具有主表面并且与漏极区电联接;(c)栅极引线,其与栅极区电联接;(d)源极引线,其与源极区电联接;以及(e)非导电模制材料,其对半导体管芯进行封装,其中,通过非导电模制材料使漏极夹具的主表面露出。

5.在上述专利的另一实施例中,半导体管芯封装包括:(a)半导体管芯,其包括第一表面、第二表面、以及竖直功率mosfet,所述竖直功率mosfet在第一表面处具有栅极区和源极区并且在第二表面处具有漏极区;(b)漏极夹具,其具有主表面并且与漏极区电联接;(c)漏极引线,其与漏极夹具的一端电联接;(d)栅极引线,其与栅极区电联接;(e)源极引线结构,其包括至少一个源极引线和具有主表面的突出区,以及与源极引线结构的主表面相反的管芯附接表面,该管芯附接表面与源极区电联接;以及(f)非导电模制材料,其对半导体管芯进行封装,其中,通过非导电模制材料使漏极夹具的主表面露出。

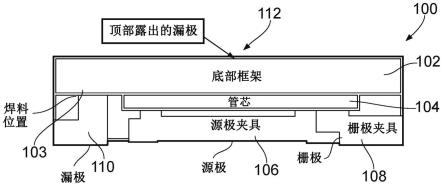

6.图1示出了另一种已知的半导体器件。该器件包括倒置mosfet封装,其中在具有鸥翼引线的器件顶部上具有露出的漏极片。

7.在本领域中还已知将若干半导体部件组合为单个封装的半导体封装,以便通过将相关和从属电路部件保持紧密接近来简化电路设计、降低成本并且提供更高效率和改善性能。与使用分立部件相比,这些一体的多芯片器件封装有利于应用集成以及更好的电气和热性能。此种将电路集成度提高的趋势导致了功率方形扁平无引线(pqfn)封装的开发和使用,该功率方形扁平无引线封装可以包括诸如12mm

×

12mm的更大形状因数的多芯片模块(mcm)。通过在pqfn封装的底面上露出大面积的管芯焊盘,对需要高效散热的高功率密度电路应用的性能进行优化。

8.pqfn封装的一个优点是制造成本低,这是因为pqfn封装的基材是使用简单的低成

本引线框架而非昂贵的多层基板。然而,由于这种单层构造,特别是对于由12mm

×

12mm形状因数支持的更大并且更复杂的多芯片模块而言,电线和布线成为特别的挑战。使用多层基板将诸如功率mosfet和igbt等功率器件进行直接互连的封装设计无法使用简单的单层引线框架。由于大部分顶面电气互连必须通过导线结合,因此必须仔细设计导线布局以防止导线短路。虽然增加封装厚度可以降低导线短路的风险,但是由于可能增加封装破裂的风险,所以为了维持封装可靠性通常不期望增加封装厚度。

技术实现要素:

9.各个示例性实施例针对如上所述的缺点和/或可以从以下公开内容中变得显而易见的其它缺点。

10.根据本发明的实施例,半导体器件包括引线框架、使用第一焊料附接至引线框架的管芯、使用第二焊料附接至管芯的源极夹具和栅极夹具、以及附接至引线框架的漏极夹具。将半导体器件倒置,使得源极夹具和栅极夹具位于半导体器件的底侧,并且其中,引线框架位于半导体器件的顶侧,使得引线框架是顶部露出的漏极夹具(top exposed drain clip)。

11.漏极夹具可以由铜制成。漏极夹具可以是弯曲柱。在本发明的优选实施例中,弯曲柱具有约90度的弯曲角。

12.在本发明的实施例中,弯曲柱布置成防止半导体器件内的任何机械倾斜。

13.在本发明的另一实施例中,弯曲柱布置成将半导体器件的所有部分维持在相同水平。

14.如上述实施例所述的半导体器件可以是pqfn半导体器件、或hemt半导体器件、或mosfet半导体器件。

15.在本发明的一个实施例中,如上述实施例所述的半导体器件还包括两个冷却系统,第一冷却系统位于半导体器件的顶侧,并且第二冷却系统位于半导体器件的底侧。

16.本发明还涉及一种制造半导体器件的方法,其中,该方法包括以下步骤:

[0017]-产生包括多个引线框架的引线框架矩阵,

[0018]-将第一焊料印刷在引线框架矩阵的顶部上,

[0019]-将管芯经由焊料附接至各自的引线框架,

[0020]-产生源极夹具、栅极夹具和漏极夹具,

[0021]

o其中,漏极夹具弯曲并且附接至各自引线框架,并且

[0022]

o其中,源极夹具和漏极夹具附接至各自管芯,

[0023]-回流,

[0024]-清洗,

[0025]-模制阵列封装(mold array packing),

[0026]-研磨或抛光以便露出源极端子、栅极端子和漏极端子,

[0027]-镀锡,

[0028]-切单(singulation),

[0029]-测试,

[0030]-倒置半导体器件,以及

[0031]-安装。

[0032]

如上述实施例所述并且具有弯曲cu柱的半导体器件提供了额外优点,这是因为弯曲cu柱保护了夹具矩阵,该弯曲cu柱用作支脚以避免任何机械倾斜,并且该弯曲cu柱设置为将半导体器件的所有部分维持在相同水平。

[0033]

根据本发明的实施例对半导体器件进行倒置为半导体器件提供了显著优点,这是因为倒置半导体器件将产生源极封装/半导体器件,这显著改善了封装/半导体器件的电阻、电感、电流处理能力和更好的热性能。

[0034]

根据本发明的实施例的半导体器件(该半导体器件具有源极向下冷却封装)具有多个优点。半导体器件更具有成本效益。

附图说明

[0035]

为了能够详细理解本公开的特征,参照实施例进行更具体的描述,其中一些实施例在附图中示出。然而,应当注意的是,附图仅示出了典型实施例,因此不应认为是对实施例范围的限制。附图是为了便于理解本公开,因此不一定按比例绘制。在结合附图阅读本说明书后,所要求保护的主题的优点对于本领域技术人员将变得显而易见,在附图中,相同的附图标记用于表示相同的元件,并且其中:

[0036]

图1示出了已知的半导体器件;

[0037]

图2示出了根据本发明的实施例的半导体器件;

[0038]

图3、图4和图5示出了根据本发明的实施例的半导体器件的制造方法;

[0039]

图6示出了根据本发明的实施例的半导体器件;

[0040]

图7示出了根据本发明的实施例的半导体器件。

具体实施方式

[0041]

图2中示出了本发明的涉及半导体器件100的实施例,该半导体器件100包括底部框架102、通过焊料103与底部框架102连接的管芯104、与管芯104连接的源极夹具106、与管芯104连接的栅极夹具108以及与底部框架102连接的漏极夹具110。如图2所示,将此半导体器件倒置,使得源极夹具106和栅极夹具108位于该半导体器件100的底部,并且其中,底部框架102位于该半导体器件100的顶部,该底部框架102是顶部露出漏极夹具112。

[0042]

本发明还涉及一种制造半导体器件的方法。该方法如图3和图4所示。

[0043]

该方法包括以下步骤:

[0044]-产生包括多个底部框架102的引线框架矩阵(图3中的附图标记200),

[0045]-将焊料103多重印刷在引线框架矩阵的顶部上(图3中的附图标记202),

[0046]-将管芯104经由焊料103附接至各自的底部框架102(图3中的附图标记204),

[0047]-对管芯顶部进行点胶(dispensing),或对管芯顶部进行多重印刷(图3中的附图标记206),

[0048]-产生源极夹具、栅极夹具和漏极夹具,回流,清洗(图3中的附图标记208),

[0049]-模制阵列封装(图3和图4中的附图标记210),

[0050]-研磨或抛光以便露出所有端子,即源极端子、栅极端子和漏极端子(图3和图4中的附图标记212),

[0051]-镀锡(sn)(图3和图4中的附图标记214),

[0052]-切单(图4和图5中的附图标记216),

[0053]-测试(图4中的附图标218),

[0054]-倒置半导体器件并且安装(图4中的附图标记220)。

[0055]

通过该方法产生的半导体器件以附图标记220在图4中示出,并且该半导体器件还在图2中示出。

[0056]

通过这种方式制造的半导体器件对于功率方形扁平无引线(pqfn)器件是特别有利的。

[0057]

下文列出根据前述实施例的半导体器件的新颖特征。

[0058]

该半导体器件包括相对较小的弯曲cu柱,该弯曲cu柱形成漏极端子/夹具。在上述制造方法中,漏极夹具最初连接在源极夹具和/或栅极夹具上,其中,所有三个夹具都在同一平面表面中,并且其中,在后面的方法步骤中,通过切单将漏极夹具与源极夹具和/或栅极夹具分离。该切单可以实施为冲压、锯切、激光切单或类似方法。在优选实施例中,该弯曲cu柱的弯曲角为约90度。

[0059]

在本发明的优选实施例中,漏极夹具的弯曲高度布置成与管芯、焊料和夹具的堆叠高度匹配。

[0060]

此外,这种弯曲cu柱提供了额外优点,这是因为这种弯曲cu柱还保护了夹具矩阵,该弯曲cu柱用作支脚以避免任何机械倾斜,并且该弯曲cu柱设置为将半导体器件的所有部分维持在相同水平(高度)。

[0061]

在本发明的优选实施例中,通过使用诸如焊料或类似物等导电粘合剂的标准已知daca处理将该弯曲漏极夹具/端子的末端附接在矩阵平面引线框架表面上,以使引线框架的露出的背面作为半导体器件的主漏极端子。

[0062]

在同一平面上的所述源极端子、栅极端子和弯曲的小漏极端子被包覆成型(图3和图4中的附图标记210)并且将通过抛光/研磨处理露出(图4中的附图标记212和214),以使在半导体的顶部和底部上具有双重露出漏极端子的封装。

[0063]

倒置半导体器件100(图4中的附图标记220)为半导体器件提供了显著优点,这是因为倒置半导体器件将产生源极封装/半导体器件,这显著改善了封装/半导体器件的电阻、电感、电流处理能力和更好的热性能。

[0064]

因此,根据本发明的前述实施例的半导体器件将具有改善性能,这是因为该半导体器件将具有相对较低的寄生电感、相对较低的封装电阻和相对较高的电流。

[0065]

根据本发明的实施例的半导体器件结合两个有利特征,该两个有利特征为半导体器件具有源极向下封装并且具有顶部冷却的漏极夹具/端子,该顶部冷却的漏极夹具/端子将通过在这种半导体器件的顶部添加散热器或者使用水冷却系统或空气冷却系统来提高这种半导体器件的热性能优势。

[0066]

根据本发明的实施例的半导体器件(该半导体器件具有源极向下冷却封装)具有多个优点。与本领域中已知的陶瓷基板和裸管芯的使用相比,该半导体器件更具有成本效益。

[0067]

在诸如eps等苛刻应用中,根据本发明的实施例的半导体器件允许使用fr4 pcb代替裸管芯模块。

[0068]

这种半导体器件是需要水冷却的brm系统(10至20kw)中的已知裸管芯模块的有利替代方案。

[0069]

根据本发明的实施例的半导体器件还提供了提高的功率密度,尤其在双冗余系统中提供了提高的功率密度。

[0070]

在半导体器件是hemt器件或mosfet器件的情况下,从顶部冷却这种hemt/mosfet器件有助于降低pcb的温度。使pcb具有较低温度允许其它部件可以置于相对更靠近hemt/mosfet器件的位置处。

[0071]

图6示出了本发明的实施例。根据本发明的实施例的半导体器件100,可以从半导体器件100的顶侧250冷却,并且还可以从半导体器件100的底侧252冷却。这种双侧冷却显著改善了半导体器件的整体耗散。半导体器件的性能也被最大化,即,idmax被增大。

[0072]

图7示出了本发明的实施例。半导体器件101包括在夹具侧旁的漏极柱/端子/夹具260、262,而不是如前述实施例中所示的连接在源极和栅极夹具上。图7中还示出了该先前实施例100,以便对本发明的这两个实施例之间的差异进行清楚说明。

[0073]

本发明的实施例可以应用于使用夹具作为互连件的所有半导体封装/器件。

[0074]

根据本发明的实施例的半导体器件对于在汽车市场中使用的pqfn半导体器件是特别有利的。

[0075]

本发明的特定和优选方面在所附独立权利要求中阐述。可以对从属和/或独立权利要求的特征的组合进行适当组合,而不仅仅如权利要求中所阐述的那样。

[0076]

本公开的范围包括其中明确或隐含公开的任何新颖特征或特征组合或其任何概括,而无论该任何新颖特征或特征组合或其任何概括是否涉及所要求保护的发明或减轻本发明解决的任何或所有问题。申请人特此通知,在本技术或从本技术衍生的任何这种进一步申请的审查期间,可以针对这些特征提出新的权利要求。特别地,参照所附权利要求,从属权利要求的特征可以与独立权利要求的特征组合,并且各个独立权利要求的特征可以以任何适当方式组合,而不仅仅是在权利要求中列举的特定组合。

[0077]

在单独实施例的上下文中描述的特征还可以在单个实施例中以组合的方式提供。相反,为了简洁起见,在单个实施例的上下文中描述的各种特征还可以单独提供或以任何合适的子组合提供。

[0078]

术语“包括”不排除其它元件或步骤,术语“一”或“一个”不排除多个。权利要求中的附图标记不应解释为限制权利要求的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1