扇出型系统级封装结构及其制作方法与流程

本发明涉及半导体封装,特别涉及一种扇出型系统级封装结构及其制作方法。

背景技术:

1、伴随着芯片技术的不断提升,单位面积下容纳的信号数量不断增加,芯片的io数量不断上升,从而导致芯片的信号io之间的间距不断减小。而印刷电路板(pcb)行业相对芯片行业发展比较滞后,基于pcb的封装技术受限于pcb的制程能力,线宽和线距无法太小,因此无法满足现在高密度芯片的系统级设计需求。与在pcb上进行系统集成相比,系统级封装(sip)能最大限度地优化系统性能、避免重复封装、缩短开发周期、降低成本、提高集成度,解决芯片的信号io间距和pcb的线宽与线距不能很好匹配的问题。现有的扇出型系统级封装技术,尤其是芯片及电气元件分两层堆叠封装的技术中,芯片及电气元件堆叠并互联大概有3种实现方案。

2、图1为一种扇出型系统级封装结构的示意图。参考图1,第一种方案是在第一层的芯片101贴装时同时贴装导电金属块102,导电金属块102例如为铜片,导电金属块102作为第一层的芯片101和第二层的电气元件103互联的通道。采用第一种方案时,在贴装过程中导电金属块102的大小及贴装间距技术限制比较多,一般不能贴装宽度在0.5mm以下的导电金属块102,且贴装间距一般不能小于0.1mm,但在实际应用中为了将封装尺寸缩小,导电金属块102的宽度需要更小,导电金属块102之间的间距也需要更小;而且,贴装的导电金属块102在后续的塑封等加工过程中容易出现倾斜等问题,良率损失较大。

3、图2为一种扇出型系统级封装结构的示意图。参考图2,第二种方案是在第一层的芯片101贴装时同时贴装印刷电路板104,印刷电路板104作为第一层的芯片101和第二层的电气元件103互联的通道。采用第二种方案时,当第一层的芯片101厚度出现不同时,需要制作不同厚度的印刷电路板104,且针对不同的互联需求,需要制作不同的印刷电路板104来嵌入互联。因此,采用印刷电路板互联使得封装成本很高。

4、图3为一种扇出型系统级封装结构的示意图。参考图3,第三种方案是在第一层的芯片101的正面制作正面再布线层105(rdl)后,在背面开盲孔并制作背面再布线层106以实现互联。若采用第三种方案,当第一层的芯片101厚度较厚时,对应的需要开的互联孔107也较深,通常互联孔107的深度超过150mm,扇出封装加工过程中,对这样的深孔进行电镀的难度较大,导致良率损失较大,且存在可靠性不良的风险。

5、因此,针对扇出型系统级封装结构,如何降低制作难度和成本,提高产品良率急需解决。

技术实现思路

1、本发明提供一种扇出型系统级封装结构及其制作方法,可以降低扇出型系统级封装结构的制作难度和成本,提高产品良率。

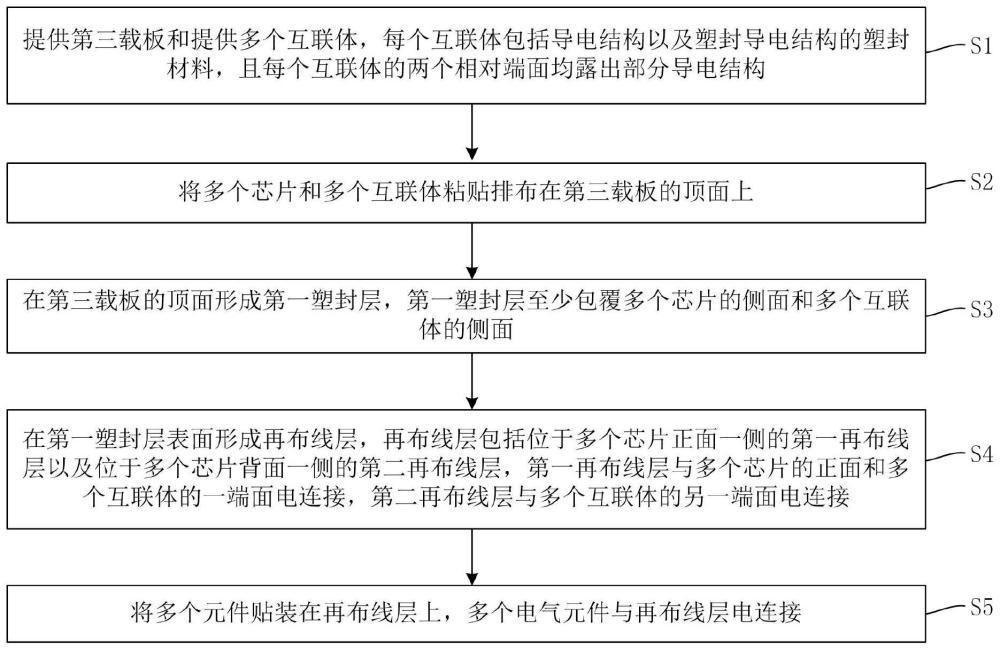

2、为了实现上述目的,本发明提供一种扇出型系统级封装结构的制作方法。所述制作方法包括:

3、提供第三载板和提供多个互联体,每个所述互联体包括导电结构以及塑封所述导电结构的塑封材料,且每个所述互联体的两个相对端面均露出部分所述导电结构;

4、将多个芯片和所述多个互联体粘贴排布在所述第三载板的顶面上;

5、在所述第三载板的顶面形成第一塑封层,所述第一塑封层至少包覆所述多个芯片的侧面和所述多个互联体的侧面;

6、在所述第一塑封层表面形成再布线层,所述再布线层包括位于所述多个芯片正面一侧的第一再布线层以及位于所述多个芯片背面一侧的第二再布线层,所述第一再布线层与所述多个芯片的正面和所述多个互联体的一端面电连接,所述第二再布线层与所述多个互联体的另一端面电连接;以及

7、将多个电气元件贴装在所述再布线层上,所述多个电气元件与所述再布线层电连接。

8、可选的,所述导电结构包括导电柱;所述提供多个互联体,包括:

9、提供第一载板,并在所述第一载板的顶面形成塑封板,所述塑封板具有相对的正面和背面,所述塑封板的正面远离所述第一载板;

10、形成导电层,所述导电层覆盖所述塑封板的正面;

11、在所述导电层远离所述塑封板的一侧设置第二载板,并去除所述第一载板,露出所述塑封板的背面;

12、在所述塑封板中形成多个导通孔,所述多个导通孔贯穿所述塑封板且露出部分所述导电层;

13、以所述导电层作为导电种子层,在所述多个导通孔中电镀形成所述多个导电柱,所述导电柱的端面与所述塑封板的背面齐平;以及

14、去除所述第二载板和所述导电层,切割所述塑封板,形成多个所述互联体。

15、可选的,所述将多个芯片和所述多个互联体粘贴排布在所述第三载板的顶面上,包括:将所述多个芯片正面朝下的粘贴在所述第三载板的顶面上,以及将所述多个互联体的一端面粘贴在所述第三载板的顶面上。

16、可选的,所述在所述第一塑封层表面形成再布线层,包括:去除所述第三载板,露出所述多个芯片正面的微凸点和露出所述互联体的端面;在所述多个芯片的正面一侧形成所述第一再布线层;以及在所述多个芯片的背面一侧形成所述第二再布线层。

17、可选的,所述互联体的原始厚度大于所述芯片的厚度;所述在所述第三载板的顶面形成第一塑封层的步骤中,所述第一塑封层覆盖所述多个芯片的背面和所述多个互联体远离所述第三载板的端面;

18、所述在所述第一塑封层表面形成再布线层,包括:所述在所述多个芯片的正面一侧形成所述第一再布线层之后,去除部分厚度的所述第一塑封层,露出所述多个互联体远离所述第一再布线层的端面;继续去除部分厚度的所述第一塑封层同时去除所述多个互联体的部分厚度;在所述多个芯片的背面一侧形成所述第二再布线层。

19、可选的,所述将多个电气元件贴装在所述再布线层上,包括:在所述第一再布线层和所述第二再布线层中的一个上贴装所述多个电气元件。

20、可选的,所述制作方法包括:所述将多个电气元件贴装在所述再布线层上之后,在所述第一再布线层和所述第二再布线层中的另一个上设置锡球。

21、可选的,所述制作方法包括:所述将多个电气元件贴装在所述再布线层上之后,形成第二塑封层,所述第二塑封层包覆所述多个电气元件的侧面以及所述多个电气元件远离所述第一塑封层的表面。

22、可选的,所述多个电气元件包括两种以上的电气元件。

23、本发明还提供一种扇出型系统级封装结构。所述扇出型系统级封装结构包括:

24、多个芯片和互联体,所述互联体包括导电结构以及塑封所述导电结构的塑封材料,且所述互联体的两个相对端面均露出部分所述导电结构;

25、第一塑封层,至少包覆所述多个芯片的侧面和所述互联体的侧面;所述互联体和所述第一塑封层分别单独形成;

26、形成在所述第一塑封层表面的再布线层,所述再布线层包括位于所述多个芯片正面一侧的第一再布线层以及位于所述多个芯片背面一侧的第二再布线层,所述第一再布线层与所述多个芯片的正面和所述互联体的一端面电连接,所述第二再布线层与所述互联体的另一端面电连接;以及

27、多个电气元件,贴装在所述再布线层上。

28、与现有技术相比,本技术提出的扇出型系统级封装结构及其制作方法具有以下优势:(1)利用互联体作为下层芯片和上层电气元件之间的互联通道,可以提高产品设计灵活性,降低加工作业难度,降低产品成本,且避免了现有技术中导电金属块在塑封过程中容易倾斜的问题以及避免了传统深孔镭射电镀的工艺,有利于提升产品良率及可靠性;(2)包括导电结构以及塑封材料的互联体可以在封装芯片前提前制作,可以提高封装效率;(3)可以根据产品的需求从包括多个导电结构的板上切割出所需尺寸的互联体,且可以在封装过程中去除互联体的部分厚度,从而互联体可以应用到不同的场景中,通用性较高,还可以实现较厚芯片的封装加工,且有利于降低系统集成产品的封装尺寸。

- 还没有人留言评论。精彩留言会获得点赞!