半导体元件的制作方法

半导体元件

1.本技术是中国发明专利申请(申请号:201810436344.5,申请日:2018年05月09日,发明名称:半导体元件)的分案申请。

技术领域

2.本发明涉及一种半导体元件,尤其是涉及一种包含共振腔区域的半导体元件。

背景技术:

3.垂直腔面发射激光器(vertical cavity surface emitting laser,vcsel)可以发出一方向垂直于活性区域的光。vcsel包含一结构,其包含一对反射镜叠层,以及位于一对反射镜叠层之间的一活性区域。一第一电极以及一第二电极分别设置于一对反射镜叠层的上侧和下侧。电流通过第一电极以及第二电极注入活性区域以使活性区域发光,且光是自上述结构发射出。

技术实现要素:

4.本发明内容提供一种半导体元件,其包含︰一半导体叠层,其包含一第一反射结构、一第二反射结构以及一位于第一反射结构以及第二反射结构之间的共振腔区域,其中共振腔区域包含一第一表面、一于第一表面的第二表面以及一位于第一表面以及第二表面的侧壁,相较于第二反射结构,第一表面较接近第一反射结构;一与第一反射结构电连接的第一电极;以及一与第二反射结构电连接的第二电极,其中第二电极包含一电极垫部位以及一自电极垫部位延伸的侧部位;其中第一电极以及第二电极的电极垫部位位于第一表面上,且第二电极的侧部位覆盖共振腔区域的侧壁。

5.本发明内容又提供一种半导体元件,其包含︰一半导体叠层,其包含一第一反射结构、一第二反射结构以及一位于第一反射结构以及第二反射结构之间的共振腔区域,其中共振腔区域包含一第一表面、一于第一表面的第二表面以及一位于第一表面以及第二表面的侧壁,相较于第二反射结构,第一表面较接近第一反射结构;一与第一反射结构电连接的第一电极;一与第二反射结构电连接的第二电极;以及一第一导电层位于共振腔区域的第二表面上,第一电极与第二电极位于第一导电层的同一侧。

附图说明

6.图1为本发明内容的第一实施例的半导体元件的俯视图;

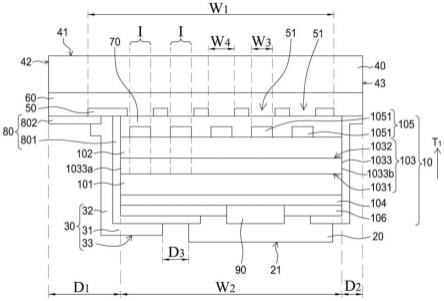

7.图2为本发明内容的第一实施例的半导体元件沿着如图1的a-a’线的剖视图;

8.图3a至图3f为制造如图1以及图2所示的半导体元件的方法的示意图;

9.图4a为本发明内容的第二实施例的半导体元件的剖视图;

10.图4b为本发明内容的制造第二实施例的半导体元件的方法中,形成第一导电层之后的俯视图;

11.图5为本发明内容的第三实施例的半导体元件的剖视图;

12.图6a至图6f为制造如图5所示的半导体元件的方法的示意图;

13.图7为本发明内容的第四实施例的半导体元件的剖视图;

14.图8a至图8i为制造如图7所示的第四实施例的半导体元件的方法的示意图;

15.图9为本发明内容的第五实施例的半导体元件的剖视图;

16.图10为本发明内容的第六实施例的半导体元件的剖视图;

17.图11a为本发明内容的第七实施例的半导体元件的剖视图;

18.图11b为本发明内容的第八实施例的半导体元件的剖视图;

19.图11c为本发明内容的第九实施例的半导体元件的剖视图;

20.图12a为本发明内容的第十实施例的半导体元件的剖视图;

21.图12b为本发明内容的第十一实施例的半导体元件的剖视图;

22.图12c为本发明内容的第十二实施例的半导体元件的剖视图;

23.图13a为本发明内容的第十三实施例的半导体元件的剖视图;

24.图13b为本发明内容的第十四实施例的半导体元件的剖视图;

25.图13c为本发明内容的第十五实施例的半导体元件的剖视图;

26.图14为本发明内容的第十六实施例的半导体元件的剖视图;以及

27.图15为本发明内容的第十七实施例的半导体元件的剖视图。

28.符号说明

29.10:半导体叠层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

101:第一反射结构

30.102:第二反射结构

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

103:共振腔区域

31.104:第一半导体接触层

ꢀꢀꢀꢀꢀꢀ

105:第二半导体接触层

32.106:蚀刻阻挡层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

107:导电区域

33.108:柱状结构

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1031:第一表面

34.1032:第二表面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1033:侧壁

35.20:第一电极

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

21:第一外表面

36.30:第二电极

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

31:电极垫部位

37.32:侧部位

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

33:第二外表面

38.40:基板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

41:顶表面

39.42:第一面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

43:第二面

40.44:第三面

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

45:第四面

41.46:第一侧

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

47:第二侧

42.50:第一导电层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

51:孔洞

43.60:粘结层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

70:第二导电层

44.80:第一绝缘层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

801:第一区域

45.802:第二区域

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

90:金属接触层

46.100:成长基板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

110:绝缘区域

47.120:凹槽

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1201:第三半导体层

48.130:第二绝缘层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1301:第三区域

49.1302:第四区域

50.1303:开孔

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

140:电流限制层

51.1401:导电部位

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1402:绝缘部位

52.150:光学结构

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1501:凸部

53.1502:凹部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

160:光学元件

54.1601:第三侧

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1602:第四侧

55.w1:第一宽度

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

w2:第二宽度

56.w3:第三宽度

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

w4:第四宽度

57.d1:第一距离

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

d2:第二距离

58.d3:第三距离

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1033a:第一部位

59.1033b:第二部位

具体实施方式

60.以下实施例将伴随着附图说明本发明的概念,在附图或说明中,相似或相同的部分是使用相同的标号,并且在附图中,元件的形状或厚度可扩大或缩小。需特别注意的是,图中未绘示或说明书未描述的元件,可以是熟悉此技术的人士所知的形式。

61.在本说明书中,除了特别指出说明,相同的元件符号于不同的附图中,具有与本发明内容任何一处说明的相同或是大致上相同的结构、材料、材料组成和/或制造方法。

62.在本发明内容中,如果没有特别的说明,通式algaas代表al

x1

ga

(1-x1)

as,其中0≤x1≤1;通式alinp代表al

x2

in

(1-x2)

p,其中0≤x2≤1;通式algainp代表(al

y1

ga

(1-y1)

)

1-x3

in

x3

p,其中0≤x3≤1,0≤y1≤1;通式alassb代表alas

(1-x5)

sb

x5

,其中0≤x5≤1;通式ingap代表in

x6

ga

1-x6

p,其中0≤x6≤1;通式ingaasp代表in

x7

ga

1-x7

as

1-y2

p

y2

,其中0≤x7≤1,0≤y2≤1;通式algaasp代表al

x9

ga

1-x9

as

1-y4

p

y4

,其中0≤x9≤1,0≤y4≤1;通式ingaas代表in

x10

ga

1-x10

as,其中0≤x10≤1;。调整元素的含量可以达到不同的目的,例如但不限于,调整能阶,或是当半导体元件为一发光元件时,调整发光元件的主发光波长。

63.图1为本发明内容的第一实施例的半导体元件的俯视图。图2为本发明内容的第一实施例的半导体元件沿着如图1的a-a’线的剖视图。请参阅图1以及图2,半导体元件包含一半导体叠层10、一与半导体叠层10电连接的第一电极20以及一与半导体叠层10电连接的第二电极30。半导体叠层10包含一第一反射结构101、一第二反射结构102以及一位于第一反射结构101以及第二反射结构102之间的共振腔区域103。第一电极20电连接第一反射结构101。第二电极30电连接第二反射结构102。在本实施例中,第一反射结构101包含n型分布式布拉格反射器(distributed bragg reflector,dbr)。第二反射结构102包含p型分布式布拉格反射器(distributed bragg reflector,dbr)。在一实施例中,第一反射结构101包含p型dbr。第二反射结构102包含n型dbr。共振腔区域103可发出辐射。优选的,共振腔区域103可发出同调辐射。优选的,同调辐射具有小于50度的远场角,且又更佳的,小于40度的远场角。共振腔区域103包含活性区域(图未示),活性区域包含多重量子阱(multi-quantum well,mqw)结构。为了明确说明光束发散度,本发明内容的发光元件的辐射的远场角为半波宽的发散角。

64.请参阅图2,共振腔区域103包含第一表面1031、一相对于第一表面1031的第二表面1032以及位于第一表面1031以及第二表面1032之间的侧壁1033。相较于第二反射结构102,第一表面1031较靠近第一反射结构101。侧壁1033具有一第一部位1033a以及一相对于

第一部位1033a的第二部位1033b。相较于第一电极20,侧壁1033的第一部位1033a较接近第二电极30。相较于第二电极30,侧壁1033的第二部位1033b较接近第一电极20。第二电极30包含一电极垫部位31以及一侧部位32,电极垫部位31在共振腔区域103的第一表面1031上,侧部位32自电极垫部位31延伸且覆盖共振腔区域103的侧壁1033。具体地,相较于第一电极20,侧壁1033的第一部位1033a较接近第二电极30的侧部位32。优选的,侧部位32覆盖侧壁1033的第一部位1033a。第一电极20以及第二电极30的电极垫部位31位于共振腔区域103的同一侧。优选的,第一电极20在共振腔区域103的厚度方向t1并未与第二电极30重叠。共振腔区域103的厚度方向t1如图1所示。

65.在本实施例中,第一电极20以及第二电极30的电极垫部位31都位于第一表面1031上。换言之,相较于共振腔区域103的第二表面1032,第一电极20以及第二电极30的电极垫部位31都较接近共振腔区域103的第一表面1031。具体而言,第一电极20包含第一外表面21,第一外表面21实质上与共振腔区域103的第一表面1031平行。第二电极30的电极垫部位31包含一第二外表面33,第二外表面33实质上与共振腔区域103的第一表面1031平行。第一外表面21和第二外表面33都位于共振腔区域103的同一侧。在本实施例中,第一外表面21和第二外表面33都位于第一表面1031上。换言之,相较于共振腔区域103的第二表面1032,第一外表面21和第二外表面33都较接近共振腔区域103的第一表面1031。第一外表面21和第二外表面33之间的高度差不大于5微米(μm),且优选的,不大于3μm。

66.第一反射结构101和第二反射结构102各包含多个交叠的第一半导体层(图未示)以及第二半导体层(图未示)。每一第一半导体层具有一第一折射系数,每一第二半导体层具有一小于每一第一折射系数的第二折射系数。第一半导体层和第二半导体层的材料包含三五族半导体材料。在一实施例中,每一第一半导体层具有一第一铝含量,且每一第二半导体层具有一第二铝含量。每一第二半导体层的第二铝含量不同于每一第一半导体层的第一铝含量,且优选的,大于每一第一半导体层的第一铝含量。在一实施例中,第一反射结构101包含一第一群组(图未标)以及一第二群组(图未标)位于第一群组上。第一群组具有一掺杂物的第一掺杂浓度,且第二群组具有一掺杂物的第二掺杂浓度。优选地,第一掺杂浓度与第二掺杂浓度不同。在一实施例中,第一掺杂浓度高于第二掺杂浓度。优选的,第一掺杂浓度与第二掺杂浓的比值介于1.1至3之间(两者都含),且优选的,介于1.1至1.5之间(两者都含)。在一实施例中,第二掺杂浓度高于第一掺杂浓度。优选的,第二掺杂浓度与第一掺杂浓的比值介于1.1至3之间(两者都含),且优选的,介于1.1至1.5之间(两者都含)。在一实施例中,第一群组具的掺杂物与第二群组的掺杂物相同。在本实施例中,第一半导体层包含alnga

(1-n)

as,第二半导体层包含almga

(1-m)

as,其中n不同于m,且优选的,m大于n。反射预定波段范围可以通过调整第一半导体层与第二半导体层中的铝和镓含量达成。每一第一半导体层具有一实质上等于λ/4n的厚度,每一第二半导体层具有一实质上等于λ/4n的厚度,其中λ为共振腔区域103发出的辐射的峰值波长,n为各层的折射系数。第一反射结构101在峰值波长具有一超过99%的反射率。第二反射结构102在峰值波长具有一超过98%的反射率。优选地,第一反射结构101在峰值波长的反射率大于第二反射结构102在峰值波长的反射率。

67.第一反射结构101中第一半导体层与第二半导体层的对数大于第二反射结构102中第一半导体层与第二半导体层的对数,其中一第一半导体层以及一相邻的第二半导体层视为一对。优选的,第一反射结构101的对数大于15,且更佳地,大于30且小于80。第二反射

结构102的对数大于15,且更佳地,大于20且小于80。

68.请参阅图1以及图2,在本实施例中,半导体元件还包含一位于半导体叠层10上的基板40。共振腔区域103发出的辐射以自共振腔区域103的第一表面1031至第二表面1032的方向逸散至半导体元件之外。基板40包含一顶表面41,具有一第一面积。第一电极20的第一外表面21包含一第二面积,第二面积不小于第一面积的10%,且优选的,不大于第一面积的40%,又更佳的,介于第一面积的13%至30%之间(两者都含)。第二电极30的第二外表面33包含一第三面积,第三面积不小于第一面积的10%,且优选的,不大于第一面积的40%,又更佳的,介于第一面积的13%至30%之间(两者都含)。第一面积、第二面积以及第三面积是自半导体元件的一俯视图观之。

69.请参阅图2,在本实施例中,半导体元件还包含一第一导电层50以及一粘结层60。第一导电层50位于基板40以及半导体叠层10之间,粘结层60覆盖第一导电层且位于基板40以及半导体叠层10之间。在本实施例中,半导体元件包含多个贯穿第一导电层50的孔洞51,多个孔洞51以一维阵列或是二维阵列的方式排列。粘结层60环绕第一导电层50,且部分的粘结层60位于多个孔洞内。粘结层60用于连接基板40和半导体叠层10,且共振腔区域103发出的辐射实质上可穿透粘结层60。在一实施例中,半导体元件包含一贯穿第一导电层50的孔洞。粘结层60环绕第一导电层50,且部分的粘结层60位于孔洞内。

70.在本实施例中,第一导电层50具有一第一宽度w1,共振腔区域103具有一第二宽度w2,第一宽度w1大于第二宽度w2。具体地,一部分的第一导电层并未被共振腔区域103覆盖,因此部分的第一导电层是裸露的。第二电极30与第一导电层50的裸露部分直接接触。具体地,第二电极30的侧部位32与第一导电层50的裸露部分直接接触。第一导电层50具有一不小于500纳米(nm)的厚度,且优选的,不大于3000nm,又更佳的,不大于2000nm。在本实施例中,第一电极20以及第二电极30位于第一导电层50的同一侧。

71.请参阅图1,在本实施例中,基板40包含一第一面42、相对于第一面42的第二面43以及一位于第一面42以及第二面43之间的第三面44以及第四面45。基板40的顶表面41位于第一面42、第二面43、第三面44以及第四面45之间。在本实施例中,第一面42的具有第一边缘(图未标),第二面43具有第二边缘(图未标),第三面44具有第三边缘(图未标),第四面45具有第四边缘(图未标)。在本实施例中,第一边缘的长度小于第三边缘的长度或第四边缘的长度,第二边缘的长度小于第三边缘的长度或第四边缘的长度。在另一实施例中,第一边缘的长度、第二边缘的长度、第三边缘的长度以及第四边缘的长度实质上相同。

72.请参阅图2,在半导体元件的一剖视图中,基板40的第一面42与共振腔区域103的侧壁1033的第一部位1033a之间的第一距离d1不同于基板40的第二面43与共振腔区域103的侧壁1033的第二部位1033b之间的第二距离d2。优选的,第一距离大于第二距离至少15微米(μm),且更佳的,不超过50μm。第一距离d1不小于20μm,且优选的,不大于60μm。第二距离d2不小于5μm,且优选的,不大于40μm。

73.请参阅图2,在本实施例中,半导体元件还包含一第一半导体接触层104以及一第二半导体接触层105,第一半导体接触层104位于第一电极20以及第一反射结构101之间,第二半导体接触层105位于第二反射结构102以及第一导电层50之间。在本实施例中,第二半导体接触层105包含多个分离的接触区域1051,多个接触区域1051以一维阵列或是二维阵列的方式排列。具体地,每一接触区域1051是位于其中一贯穿第一导电层50的孔洞51的正

下方。优选的,接触区域1051与孔洞51是以一对一的方式对应。换言之,第一导电层50在共振腔区域103的厚度方向t1并未和多个接触区域1051重叠。

74.在本实施例中,第二电极30在共振腔区域103的厚度方向t1与一或多个接触区域1051重叠。具体地,第二电极30的电极垫部位31在共振腔区域103的厚度方向t1与一或多个接触区域1051重叠。每一接触区域1051具有一第三宽度w3。每一贯穿第一导电层50的孔洞51具有一第四宽度w4。其中一接触区域1051的第三宽度w3小于其对应孔洞51的第四宽度w4。具体地,其中一接触区域1051的第三宽度w3小于位于其正上方的孔洞51的第四宽度w4。优选的,每一接触区域1051的第三宽度w3小于其对应孔洞51的第四宽度w4。因此,可以避免或是减轻第一导电层50遮住自共振腔区域103发出的光的问题。在本实施例中,每一孔洞51具有一为圆形的形状。每一接触区域1051具有一为圆形的形状。其中一孔洞51的第四宽度w4为圆形的直径。其中一接触区域1051的第三宽度w3为圆形的直径。接触区域1051与孔洞51形状不限于本实施例。孔洞51的形状以及接触区域1051的形状可以为椭圆形、长方形、正方形、菱形或是任何其他合适的形状。第三宽度w3例如为,但不限于,介于15μm至40μm之间(两者都含)。第四宽度w4例如为,但不限于,介于20μm至50μm之间(两者都含)。

75.在一实施例中,半导体元件还包含一贯穿第一导电层50的孔洞,第二半导体接触层105位于孔洞的正下方。换言之,第一导电层50在共振腔区域103的厚度方向t1并未和第二半导体接触层105重叠。第二半导体接触层105具有一第三宽度,且贯穿第一导电层50的孔洞具有一第四宽度。优选的,第三宽度小于第四宽度。

76.请参阅图2,在本实施例中,半导体叠层10还包含一位于第二电极30以及第一半导体接触层104之间的蚀刻阻挡层106。半导体元件还包含一位于第二反射结构102以及第一导电层50之间的第二导电层70。第二导电层70包覆并环绕多个接触区域1051。接触区域1051与第二反射结构102之间的接触电阻较第二导电层70与第二反射结构102之间的接触电阻低。在本实施例中,第一导电层50的材料与第二导电层70的材料不同。

77.请参阅图1以及图2,在本实施例中,半导体元件还包含一位于半导体叠层10以及第二电极30之间的第一绝缘层80。此外,第一绝缘层80位于第一电极20以及半导体叠层10之间。第一绝缘层80在共振腔区域103的厚度方向t1与第一反射结构101以及与第二反射结构102重叠。在本实施例中,第一绝缘层80覆盖蚀刻阻挡层106的一底表面、覆盖蚀刻阻挡层106的侧壁、覆盖第一半导体接触层104的侧壁、覆盖第一反射结构101的侧壁、覆盖共振腔区域103的侧壁1033、覆盖第二反射结构102的侧壁、覆盖第二导电层70的侧壁且与第一导电层50的裸露部分直接接触。第二电极30覆盖部分的第一绝缘层80,因此,第一绝缘层80位于共振腔区域103的第一表面1031以及第二电极30的电极垫部位31之间且位于共振腔区域103的侧壁1033以及第二电极30的侧部位32之间。第一电极20覆盖第一绝缘层80的另一部分,因此第一绝缘层80亦位于共振腔区域103的第一表面1031以及第一电极20之间。

78.请参阅图2,在本实施例中,在半导体元件的一剖视图中,第一绝缘层80包含一第一区域801以及一第二区域802。第二电极30位于第一区域801以及一第二区域802之间。具体地,第二电极30的侧部位32分隔第二区域802以及第一区域801。第一区域801位于半导体叠层10以及第二电极30的侧部位32之间。第二区域802与粘结层60直接接触。在本实施例中,第二区域802同时与粘结层60以及第一导电层50直接接触。第一绝缘层80具有一小于500nm的厚度,且优选的,不大于3μm。

79.请参阅图1以及图2,在本实施例中,第一电极20与第二电极30分离,且位于第一电极20以及半导体叠层10之间的第一绝缘层80是裸露的。第一电极20与第二电极30之间的一第三距离d3不小于50μm,且优选的,不大于300μm,且更佳的,介于90μm至200μm之间(两者都含)。换言之,第一电极20与第二电极30的电极垫部位31之间的一第三距离d3不小于50μm,且优选的,不大于300μm,且更佳的,介于90μm至200μm之间(两者都含)。

80.请参阅图2,半导体元件还包含一位于第一电极20以及第一反射结构101之间的金属接触层90。金属接触层90贯穿蚀刻阻挡层106因而和第一半导体接触层104直接接触。换言之,蚀刻阻挡层106环绕金属接触层90。在本实施例中,金属接触层90在共振腔区域103的厚度方向t1并未和第二电极30重叠。具体地,金属接触层90在共振腔区域103的厚度方向t1并未和第二电极30的电极垫部位31重叠。优选的,金属接触层90具有一最大宽度,其小于第一电极20的最大宽度。金属接触层90的最大宽度以及第一电极20的最大宽度的衡量方向实质上垂直于共振腔区域103的厚度方向t1。

81.当电流自第一电极20以及第二电极30流入共振腔区域103,因为在第二半导体接触层105和第二导电层70之间的接触电阻相对地比第二导电层70和第二反射结构10之间的接触电阻低,大部分的电流自第二导电层70流向第二半导体接触层105的接触区域1051,接着主要经由接触区域1051流入共振腔区域103。也就是说,位于接触区域1051正下方的第二反射结构102的部位的电流密度高于第二反射结构102的未被接触区域1051覆盖的部位的电流密度。在本实施例中,位于接触区域1051的正下方的共振腔区域103作为主要辐射发射区i,且主要辐射发射区i发射出的辐射经由形成于第一导电层50的孔洞51自基板40逸散至半导体元件之外。

82.在本实施例中,半导体元件具有一正向电压vf、一激光阈值电流i

th

以及一饱和电流i

sat

。半导体元件于正向电压vf开始传导显着的正向电流,激光阈值电流i

th

是半导体元件的辐射发射区发射的辐射中受激辐射(stimulated emission)超过自发辐射(spontaneous emission)时的最小电流,因此于激光阈值电流i

th

下辐射为同调性。饱和电流i

sat

是辐射输出不再随正向电流增加而增加的电流。半导体元件在大于半导体元件的正向电压vf的操作电压v

op

以及在正向电流小于激光阈值电流i

th

之下运作时,本发明内容的半导体元件的辐射发射区i发射的辐射是非同调光。当半导体元件在正向电流大于激光阈值电流i

th

以及小于饱和电流i

sat

之下运作时,半导体元件的辐射发射区i发出的辐射为同调光。

83.图3a至图3f为制造如图1以及图2所示的半导体元件的方法。图3a为形成接触区域1051之后的俯视图。图3b为沿着如图3a的a-a’线的剖视图。请参阅图3a以及图3b,制造如图1以及图2所示的半导体元件的方法包含提供一成长基板100;以外延成长的方式在成长基板100上形成一半导体叠层10,其中半导体叠层10依序包含蚀刻阻挡层106、第一半导体接触层104、第一反射结构101、共振腔区域103、第二反射结构102以及一半导体层(图未示);以及图案化半导体层以形成包含多个接触区域1051的第二半导体接触层105。

84.图3c为形成接触区域1051后的俯视图。图3d为沿着如图3c的a-a’线的剖视图。请参阅图3c以及图3d,制造半导体元件的方法还包含于半导体叠层10上形成一第二导电层70,且第二导电层70包覆多个接触区域1051;在第二导电层70上形成一电流传导层(图未示);以及通过光刻光掩模图案化电流传导层以形成第一导电层50。图案化电流传导层后,半导体元件包含多个贯穿第一导电层50的孔洞51,孔洞51的位置对应接触区域1051的位

置。换言之,第一导电层500在共振腔区域103的厚度方向t1并未与接触区域1051重叠,且多个孔洞51裸露位于其下的第二导电层70。

85.图3e为连接基板40后的剖视图。请参阅图3e,制造半导体元件的方法还包含提供一基板40;通过一粘结层60连接基板40以及图3d所示的结构;以及用任何适合的方法移除成长基板100。一部分的粘结层60位于形成于第一导电层50的孔洞51内。

86.图3f为形成第一绝缘层80后的剖视图。请参阅图3f,制造半导体元件的方法还包含以任何适合的方法,例如以感应耦合等离子体(inductively coupled plasma,icp)或湿蚀刻移除半导体叠层10的周围部分以及移除第二导电层70的周围部分以裸露一部分的第一导电层50以及一部分的粘结层60;移除一部分的蚀刻阻挡层106以裸露部分的第一半导体接触层104;形成一与第一半导体接触层104的裸露部分直接接触的金属接触层90,在本实施例中,金属接触层90包含合金,例如为锗金镍;形成一第一绝缘层80,第一绝缘层80在蚀刻阻挡层106相对于基板40的表面上、覆盖半导体叠层10的侧壁、覆盖第二导电层70的侧壁以及与第一导电层50的裸露部分直接接触。

87.制造半导体元件的方法还包含移除部分位于第一导电层50上的第一绝缘层80以及形成一第一电极20以及一第二电极30,以完成如图2所示的半导体元件。

88.请参阅图2,部分位于第一导电层50上的第一绝缘层80被移除以形成一裸露部分的第一导电层50的沟槽(图未标),以及移除部分位于第一半导体接触层104上的第一绝缘层80,用于同时裸露蚀刻阻挡层106以及金属接触层90。在另一实施例中,移除第一绝缘层80后可以不裸露蚀刻阻挡层106,只裸露金属接触层90。在未完成的半导体元件的剖视图中,沟槽将第一绝缘层80分隔成一第一区域801以及一第二区域802。第一区域801覆盖半导体叠层10的侧壁。

89.第一电极20与金属接触层90的裸露部分直接接触,且优选的,第一电极20同时与金属接触层90的裸露部分、蚀刻阻挡层106的裸露部分以及部分的第一绝缘层80直接接触。第二电极30与第一电极20分离且位于第一绝缘层80上。具体地,第二电极30覆盖第一区域801。部分的侧部位32位于沟槽内以直接接触第一导电层50的裸露部分。

90.图4a为本发明内容的第二实施例的半导体元件的剖视图。图4b为本发明内容的制造第二实施例的半导体元件的方法中,形成第一导电层50之后的俯视图。本发明内容的第二实施例的半导体元件包含与第一实施例大致上相同的结构,且制造第二实施例的半导体元件的方法包含与制造第一实施例的半导体元件大致上相同的步骤,第二实施例的半导体元件与第一实施例的半导体元件不同的地方在于,第二半导体接触层105在共振腔区域103的厚度方向t1并未与第二电极30重叠。换言之,第二半导体接触层105在共振腔区域103的厚度方向t1并未与第二电极30的电极垫部位31重叠。具体地,贯穿第一导电层50的孔洞51在共振腔区域103的厚度方向t1并未与第二电极30的电极垫部位31重叠。

91.图5为本发明内容的第三实施例的半导体元件的剖视图。本发明内容的第三实施例的半导体元件包含与第一实施例大致上相同的结构,不同的地方如下所述。在本实施例中,第二半导体接触层105未包含如第一实施例的多个分离的接触区域1051。第一导电层50直接位于第二半导体接触层105之上。本实施例的半导体元件并未包含如第一实施例中位于第二反射结构102以及粘结层60之间的第二导电层70。半导体元件还包含一形成于半导体叠层10内的绝缘区域110,用于在半导体叠层10内定义一或多个导电区域107。绝缘区域

110包含离子,例如氩(ar)离子,氦(he)离子或氢(h)离子,用于降低半导体叠层10的导电率。如图6a所示,绝缘区域110围绕多个导电区域107。

92.在本实施例中,绝缘区域110位于第一半导体接触层104上。优选的,绝缘区域110位于共振腔区域103上。导电区域107包含第二半导体接触层105的未含有降低导电率的离子的部分以及第二反射结构102的未含有降低导电率的离子的部分。每一导电区域107直接位于其中一孔洞51之下。在本实施例中,绝缘区域110位于第二半导体接触层105内以及位于第二反射结构102内。在另一实施例中,绝缘区域110只位于第二反射结构102内。具体地,绝缘区域110并未直接位于贯穿第一导电层50的多个孔洞51之下。换言之,绝缘区域110在共振腔区域103的厚度方向t1与第一导电层50重叠。然而,绝缘区域110在共振腔区域103的厚度方向t1并未与贯穿第一导电层50的多个孔洞51重叠。

93.在本实施例中,绝缘区域110的图案实质上与第一导电层50的图案相等。换言之,被绝缘区域110围绕且彼此分离的导电区域107是以一维阵列或是二维阵列的方式排列。优选的,导电区域107的排列方式与贯穿第一导电层50的孔洞51的排列方式大致上相同。此外,每一导电区域107是分别直接位于其中一孔洞51之下。在本实施例中,在导电区域107的俯视图中观之,导电区域107的形状可为椭圆形、长方形、正方形、菱形或是任何其他合适的形状。每一导电区域107具有一导电率,其高于绝缘区域110的导电率。优选的,导电区域107的导电率高于绝缘区域110的导电率至少3个数量级,且更佳地,至少5个数量级。

94.贯穿第一导电层50的多个孔洞51裸露部分位于其下的第二半导体接触层105。在本实施例中,当电流自第一电极20以及第二电极30流入共振腔区域103,因为在孔洞51正下方的导电区域107的导电率高于绝缘区域110的导电率,大部分的电流自在孔洞51正下方的导电区域107流入共振腔区域103。在本实施例中,位于孔洞51正下方的共振腔区域103的部位作为主要辐射发射区i,且主要辐射发射区i发射出的辐射经由贯穿第一导电层50的孔洞51自基板40逸散至半导体元件之外。在本实施例中,在半导体元件的一剖视图中,其中一导电区域107的宽度大于对应的孔洞51的第四宽度w4。优选的,每一导电区域107的宽度大于其对应的孔洞51的第四宽度w4。换言之,第一导电层50在共振腔区域103的厚度方向t1同时与导电区域107以及绝缘区域110重叠。

95.图6a至图6f为制造如图5所示的半导体元件的方法。图6a为形成绝缘区域110之后的俯视图。图6b为沿着如图6a的a-a’线的剖视图。请参阅图6a以及图6b,制造如图5所示的半导体元件的方法包含提供一成长基板100;以外延成长的方式在成长基板100上形成一半导体叠层10;以及在部分的半导体叠层10内注入离子以降低导电率以形成绝缘区域110。注入离子的同时,实质上并未影响另一部分的半导体叠层10的导电率,离子可例如为氩(ar)离子,氦(he)离子或氢(h)离子。在本实施例中,离子是注入部分的第二半导体接触层105内以及部分的第二反射结构102内以形成绝缘区域110以及定义被绝缘区域110环绕的导电区域107。优选的,离子并未注入共振腔区域103内。在另一实施例中,离子只注入部分的第二反射结构102内。第二半导体接触层105的未含有降低导电率的离子的部分以及第二反射结构102的未含有降低导电率的离子的部分为导电区域107。在本实施例中,导电区域107以一维阵列或二维阵列的方式排列。

96.图6c为形成第一导电层50后的俯视图。图6d为沿着图6c的a-a’线的剖视图。请参阅图6c以及图6d,制造如图5所示的半导体元件的方法还包含在半导体叠层10上形成一电

流传导层(图未示);以及通过光刻光掩模图案化电流传导层以形成第一导电层50。图案化电流传导层后,半导体元件包含多个贯穿第一导电层50的孔洞51,用于裸露部分位于其下且未包含注入离子的第二半导体接触层105。换言之,贯穿第一导电层50的孔洞51裸露其下的导电区域107。在本实施例中,在半导体叠层10的一剖视图中,每一导电区域107的宽度大于对应的孔洞51的第四宽度w4。换言之,第一导电层50在共振腔区域103的厚度方向t1同时与导电区域107以及绝缘区域110重叠。

97.图6e为连接基板40后的剖视图。请参阅图6e,制造如图5所示的半导体元件的方法还包含提供一基板40;通过一粘结层60连接基板40以及图6d所示的结构;以及用任何适合的方法移除成长基板100。一部分的粘结层60位于贯穿第一导电层50的多个孔洞51内。

98.图6f为形成第一绝缘层80后的剖视图。请参阅图6f,制造如图5所示的半导体元件的方法还包含以任何适合的方法,例如以感应耦合等离子体(inductively coupled plasma,icp)或湿蚀刻移除半导体叠层10的周围部分以裸露一部分的第一导电层50以及一部分的粘结层60;移除一部分的蚀刻阻挡层106以裸露部分的第一半导体接触层104;形成一与第一半导体接触层104的裸露部分直接接触的金属接触层90,金属接触层90包含合金,例如为锗金镍;形成一第一绝缘层80,第一绝缘层80在蚀刻阻挡层106相对于基板40的表面上、覆盖蚀刻阻挡层106的侧壁、覆盖第一反射结构101的侧壁、覆盖共振腔区域103的侧壁1033、覆盖绝缘区域110的侧壁且与第一导电层50的裸露部分直接接触。在本实施例中,第一绝缘层80也与粘结层60直接接触。

99.制造半导体元件的方法还包含移除部分位于第一导电层50上的第一绝缘层80以及形成一第一电极20以及一第二电极30以完成如图5所示的半导体元件。请参阅图5,部分位于第一导电层50上的第一绝缘层80被移除以形成一裸露部分第一导电层50的沟槽(图未标),以及移除部分位于第一半导体接触层104上的第一绝缘层80,用于同时裸露蚀刻阻挡层106以及金属接触层90。在另一实施例中,移除第一绝缘层80后可以不裸露蚀刻阻挡层106,只裸露金属接触层90。在未完成的半导体元件的剖视图中,沟槽将第一绝缘层80分隔成一第一区域801以及一第二区域802。第一区域801覆盖半导体叠层10的侧壁。

100.第一电极20与金属接触层90的裸露部分直接接触,且优选的,第一电极20同时与金属接触层90的裸露部分、蚀刻阻挡层106的裸露部分以及部分的第一绝缘层80直接接触。第二电极30与第一电极20分离且位于第一绝缘层80上。具体地,第二电极30覆盖第一区域801。部分的侧部位32位于沟槽内以直接接触第一导电层50的裸露部分。

101.图7为本发明内容的第四实施例的半导体元件的剖视图。本发明内容的第四实施例的半导体元件包含与第一实施例大致上相同的结构,不同的地方如下所述。请参阅图7,半导体叠层10包含多个通过一凹槽120彼此分离的柱状结构108。每一柱状结构108包含相同结构,亦即,在本实施例中,每一柱状结构108依序包含如第一实施例提及的第一反射结构101、共振腔区域103、第二反射结构102以及第二半导体接触层105。

102.每一柱状结构108包含一外壁1081,其中凹槽120裸露外壁1081。具体而言,凹槽120贯穿第二半导体接触层105,优选的,凹槽120还贯穿第二反射结构102以及贯穿共振腔区域103以裸露第一反射结构101。因此,柱状结构108的外壁1081为裸露的。相较于共振腔区域103的侧壁1033,外壁1081较远离基板40的第一面42、第二面43、第三面44以及第四面45。在柱状结构108的俯视图中,柱状结构108的形状可以为,但不限于,圆形、长方形、正方

形、菱形或是任何其他合适的形状。

103.半导体元件还包含一第二绝缘层130沿着柱状结构108的轮廓覆盖柱状结构108。具体地,第二绝缘层130覆盖第二半导体接触层105的一面对基板40的顶表面、覆盖柱状结构108的外壁1081以及覆盖第一反射结构101被凹槽120裸露的一上表面。具体地,第二绝缘层130位于第一导电层5以及第一电极20之间。第二绝缘层130在共振腔区域103的厚度方向t1与第一绝缘层80重叠。换言之,第二绝缘层130在共振腔区域103的厚度方向t1同时与第二电极30以及第一绝缘层80重叠。具体地,第二绝缘层130在共振腔区域103的厚度方向t1同时与第二电极30的电极垫部位31以及第一绝缘层80重叠。

104.在本实施例中,第二绝缘层130位于第一绝缘层80的第二区域802以及粘结层60之间。第二绝缘层130同时与第一导电层50以及粘结层60直接接触。具体地,第二绝缘层130包含一第三区域1301以及一第四区域1302。第二电极30的侧部位32分隔第三区域1301以及第四区域1302。第二绝缘层130的第三区域1301在共振腔区域103的厚度方向t1同时与半导体叠层10以及第一导电层50重叠。第二绝缘层130的第四区域1302在共振腔区域103的厚度方向t1同时与第一绝缘层80的第二区域802以及第一绝缘层80重叠。

105.请参阅图7,在本实施例中,第二绝缘层130具有一实质上等于nλ/4的光学厚度,其中λ为共振腔区域103发出的辐射的峰值波长,且n为奇数的正整数。在本实施例中,λ为940

±

10nm。在另一实施例中,λ为905

±

10nm。在另一实施例中,λ为850

±

10nm。在另一实施例中,第二绝缘层130的厚度介于300nm至400nm之间(两者都含)。半导体元件包含多个贯穿第二绝缘层130的开孔1303。每一开孔1303直接位于其中一柱状结构108之上。每一开孔1303裸露部分位于其下的对应的柱状结构108的第二半导体接触层105。具体地,在第二绝缘层130的俯视图中,其中一或是每一开孔1303的形状为,但不限于,环形。

106.请参阅图7,第一导电层50沿着第二绝缘层130的轮廓覆盖在第二绝缘层130之上。具体地,一部分的第一导电层50位于贯穿第二绝缘层130的开孔1303内以与一或多个柱状结构108的第二半导体接触层105直接接触。本实施例的半导体元件并未包含如第一实施例中位于第二反射结构102以及粘结层60之间的第二导电层70。

107.请参阅图7,在本实施例中,半导体元件包含一电流限制层140位于每一柱状结构108中。优选的,电流限制层140位于第二反射结构102内。电流限制层140包含一导电部位1401以及一绝缘部位1402,绝缘部位1402环绕导电部位1401。位于导电部位1401正下方的共振腔区域103的部位作为主要辐射发射区i,且主要辐射发射区i发射出的辐射经由贯穿第一导电层50的孔洞51自基板40逸散至半导体元件之外。

108.导电部位1401包含三五族半导体材料,三五族半导体材料包含铝,例如alaga

(1-a)

as,其中0.9≤a≤1.0。导电部位1401中的铝含量高于第一反射结构101以及第二反射结构102中第一半导体层的铝含量n以及第二半导体层的铝含量m。例如,导电部位1401包含alaga

1-a

as,其中0.9≤a≤0.99。绝缘部位1402包含氧化物。优选的,绝缘部位1402包含氧化铝,氧化铝具有为alaob的实验式,其中a和b为不含0的自然数。在本实施例中,电流限制层140插入第二反射结构102中以位于其中一第一半导体层以及相邻的第二半导体层之间。在另一实施例中,每一柱状结构108中,第二反射结构102中的其中一第一半导体层或其中一第二半导体层被取代为电流限制层140。贯穿第一导电层50的多个孔洞51位于对应的电流限制层140的导电部位1401的正上方。优选的,第二电极30的电极垫部位31在共振腔区域

103的厚度方向t1并未与柱状结构108的导电部位1401重叠。在一实施例中,第二电极30的电极垫部位31在共振腔区域103的厚度方向t1并未与贯穿第一导电层50的多个孔洞51重叠。每一导电部位1401具有一宽度。优选的,其中一导电部位1401的宽度小于对应孔洞51的第四宽度w4。优选的,其中一导电部位1401的宽度不小于3μm,且优选的,不大于20μm。

109.图8a至图8i为制造如图7所示的第四实施例的半导体元件的方法。图8a为形成第二半导体接触层105之后的俯视图。请参阅图8a,制造如图7所示的半导体元件的方法包含提供一成长基板100;以外延成长的方式在成长基板100上形成一如第一实施例中提及的半导体叠层10,半导体叠层10包含第二反射结构102,第二反射结构102包含如第一实施例提及的多个交叠的第一半导体层以及第二半导体层。本实施例与第一实施例不同的地方在于,在本实施例中,第二反射结构102包含一第三半导体层1201位于其中一第一半导体层与相邻的第二半导体层之间。第三半导体层1201具有一第三折射系数,其小于每一第二半导体层的第二折射系数。在一实施例中,第三半导体层1201具有一第三铝含量,其高于每一第二半导体层的第二铝含量。在本实施例中,多个第一半导体层包含alnga

(1-n)

as,多个第二半导体层包含almga

(1-m)

as,,第三半导体层1201包含alfga

(1-f)

as,且f》m》n。

110.图8b为形成多个柱状结构108之后的俯视图。图8c为沿着图8b的a-a’线的剖视图。请参阅图8b以及图8c,制造如图7所示的半导体元件的方法还包含用任何适合的方法移除部分的半导体叠层10以形成一凹槽120以及多个柱状结构108。多个柱状结构108通过凹槽120彼此分离,每一柱状结构108包含一外壁1081,且优选的,凹槽120裸露第一反射结构101的一上表面。

111.图8d为形成第二绝缘层130之后的俯视图。图8e为沿着图8d的a-a’线的剖视图。请参阅图8d以及图8e,制造如图7所示的半导体元件的方法还包含氧化第三半导体层1201以形成一电流限制层140,电流限制层140包含一导电部位1401以及一环绕导电部位1401的绝缘部位1402,具有第三铝含量的第三半导体层1201是自被凹槽120裸露的外壁1081开始氧化以形成绝缘部位1402;形成一第二绝缘层130,第二绝缘层130覆盖第二半导体接触层105的一面对基板40的顶表面、覆盖柱状结构108的外壁1081以及覆盖第一反射结构101被凹槽120裸露的一上表面;以及移除部分位于柱状结构108上的第二绝缘层130以形成多个开孔1303,其中多个开孔1303裸露部分位于其下的第二半导体接触层105。

112.图8f为形成第一导电层50后的俯视图。图8g为沿着图8f的a-a’线的剖视图。请参阅图8f以及图8g,制造如图7所示的半导体元件的方法还包含在第二绝缘层130上以及开孔1303内形成一电流传导层(图未示),电流传导层直接接触第二半导体接触层105;以及通过光刻光掩模图案化电流传导层以形成第一导电层50。图案化电流传导层后,半导体元件包含多个贯穿第一导电层50的孔洞51。每一孔洞51位于其中一柱状结构108的电流限制层140的导电部位1401的正上方,且孔洞51裸露部分位于其下的第二半导体接触层105。

113.图8h为连接基板40后的剖视图。请参阅图8h,制造如图7所示的半导体元件的方法还包含提供一基板40;通过一粘结层60连接基板40以及图8g所示的结构。一部分的粘结层60位于贯穿第一导电层50的多个孔洞51内。

114.图8i为形成第一绝缘层80后的剖视图。请参阅图8i,制造如图7所示的半导体元件的方法还包含用任何适合的方法移除成长基板100;以任何适合的方法,例如以感应耦合等离子体(inductively coupled plasma,icp)或湿蚀刻移除半导体叠层10的周围部分以裸

露一部分的第二绝缘层130;移除一部分的蚀刻阻挡层106以裸露部分的第一半导体接触层104;形成一与第一半导体接触层104的裸露部分直接接触的金属接触层90,金属接触层90包含合金,例如为锗金镍;以及形成一第一绝缘层80,第一绝缘层80位于蚀刻阻挡层106的一相对于基板40的顶表面上、覆盖半导体叠层10的侧壁以及覆盖第二绝缘层130。

115.制造如图7所示的半导体元件的方法还包含同时移除部分的第一绝缘层80以及部分的第二绝缘层130以及形成一第一电极20以及形成一第二电极30,用于完成如图7所示的半导体元件。请参阅图7,部分的第一绝缘层80以及部分的第二绝缘层130同时被移除以形成一裸露部分第一导电层50的沟槽(图未标),以及部分位于第一半导体接触层104上的第一绝缘层80被移除,用于同时裸露蚀刻阻挡层106以及金属接触层90。在另一实施例中,移除第一绝缘层80后可以不裸露蚀刻阻挡层106,只裸露金属接触层90。在未完成的半导体元件的剖视图中,沟槽将第一绝缘层80分隔成一第一区域801以及一第二区域802以及将第二绝缘层130分隔成一第三区域1301以及一第四区域1302。

116.第一电极20与金属接触层90的裸露部分直接接触,且优选的,第一电极20同时与金属接触层90的裸露部分、蚀刻阻挡层106的裸露部分以及部分的第一绝缘层80直接接触。第二电极30与第一电极20分离且位于第一绝缘层80上。具体地,第二电极30覆盖第一绝缘层80的第一区域801,且部分的侧部位32位于沟槽内以直接接触第一导电层50的裸露部分。换言之,在半导体元件的一剖视图中,第二电极30的侧部位32位于第一绝缘层80的第一区域801以及第一绝缘层80的第二区域802之间且位于第二绝缘层130的第三区域1301以及一第四区域1302之间以直接接触第一导电层50的裸露部分。

117.图9为本发明内容的第五实施例的半导体元件的剖视图。本发明内容的第五实施例的半导体元件包含与第一实施例大致上相同的结构,不同的地方在于,金属接触层90位于第一绝缘层80以及半导体叠层10之间。具体地,在一半导体元件的剖视图中,金属接触层90在共振腔区域103的厚度方向t1与所有的接触区域1051以及孔洞51重叠。

118.图10为本发明内容的第六实施例的半导体元件的剖视图。本发明内容的第六实施例的半导体元件包含与第一实施例大致上相同的结构,不同的地方在于第二反射结构102包含一平台结构1021。具体地,第二反射结构102包含两个不同的宽度,其中一宽度大致上等于共振腔区域103的第二宽度w2,另一宽度大于共振腔区域103的第二宽度w2。

119.制造如图10所示的第六实施例的半导体元件的方法包含与制造如图1以及图2所示的半导体元件的方法大致上相同的步骤。不同之处如下所述。在形成如图3e所示的结构之后,制造如图10所示的第六实施例的半导体元件的方法还包含移除蚀刻阻挡层106的周围部分、移除第一半导体接触层104的周围部分、移除第一反射结构10的周围部分、移除共振腔区域103的周围部分以及移除第二反射结构102的底部周围部分以形成平台结构1021;通过一保护层保护共振腔区域103的侧壁10331;进一步移除第二反射结构102的顶部周围部分以及第二导电层70的周围部分以裸露第一导电层50。于移除第二导电层70的周围部分的步骤中,一部分裸露的第一导电层50可能被移除导致第一导电层50的导电材料溅洒,进而导致漏电流的问题。通过保护共振腔区域103的侧壁10331,可以减轻或避免因移除部分裸露的第一导电层50而造成第一导电层50的导电材料溅洒至共振腔区域103的侧壁1033,并进一步减轻或避免半导体元件漏电流的问题。

120.接着,部分的蚀刻阻挡层106被移除,形成第一绝缘层80、第一电极20以及第二电

极30。相关的叙述可参考前面的段落。

121.图11a为本发明内容的第七实施例的半导体元件的剖视图。本发明内容的第七实施例的半导体元件包含与第一实施例大致上相同的结构,不同的地方在于本实施例的半导体元件包含一光学结构150。共振腔区域103发出的辐射具有一辐射图案。光学结构150可以改变辐射图案。在一实施例中,光学结构150可以放大或是缩小辐射图案的尺寸。在一实施例中,光学结构150可以改变辐射图案的方向或是形状。例如,辐射图案的形状可以通过光学结构150从圆形改变为线形。在半导体元件的一剖视图中,光学结构150包含交替设置的多个凸部1501以及多个凹部1502。在半导体元件的一剖视图中,其中一凸部1501的形状包含矩形、三角形、或半圆形。多个凸部1501的形状可以相同或是不同。在一实施例中,光学结构150包含菲涅耳透镜(fresnel lens)。

122.在一实施例中,自光学结构150的一俯视图中,多个凸部1501以及多个凹部1502可被设置为具有重复单元的规则图案。在另一实施例中,自光学结构150的一俯视图中,多个凸部1501以及多个凹部1502可被设置为不规则的图案。在本实施例中,在半导体元件的一剖视图中,光学结构150的每一凸部1501的形状包含矩形。在一实施例中,光学结构150的其中一凸部1501的高度介于0.3μm至5μm之间。在本实施例中,光学结构150的其中一凸部1501的高度介于0.5μm至1.5μm之间。多个凸部1501的高度可以相同或是不同。在本实施例中,多个凸部1501的高度大致上相同。

123.请参阅图11a,具体地,基板40包含一第一侧46以及一相对于第一侧46的第二侧47。相较于第二侧47,第一侧46较接近半导体叠层10。第一侧46以及第二侧47接近第一面42、第二面43、第三面(图未示)以及第四面(图未示)之间。第二侧47包含顶表面41。在本实施例中,光学结构150位于第二侧47。具体地,基板40的一部分被移除以形成光学结构150。光学结构在共振腔区域103的厚度方向t1与一或多个主要辐射发射区i重叠。在本实施例中,光学结构150在共振腔区域103的厚度方向t1与所有的主要辐射发射区i重叠。在本实施例中,辐射通过光学结构150自基板40逸散至半导体元件之外。

124.图11b为本发明内容的第八实施例的半导体元件的剖视图。本发明内容的第八实施例的半导体元件包含与第七实施例大致上相同的结构,不同的地方在于光学结构150位于第一侧46。在本实施例中,光学结构150与粘结层60直接接触。具体地,光学结构150的多个凸部1501与粘结层60直接接触。在一实施例中,多个凹部1502可以填入空气或是其他不同于基板40材料的材料。优选的,共振腔区域103发出的辐射可穿透填入多个凹部1502的材料。在一实施例中,填入多个凹部1502的材料与粘结层60的材料相同。若填入多个凹部1502的材料与粘结层60的材料相同,多个凹部1502与粘结层60之间不会有界线。

125.图11c为本发明内容的第九实施例的半导体元件的剖视图。本发明内容的第九实施例的半导体元件包含与第七实施例大致上相同的结构,不同的地方在于本实施例中半导体元件包含两个光学结构150。其中一光学结构150位于第一侧46,且另一光学结构150位于第二侧47。在半导体元件的一剖视图中,两个光学结构150的形状可以相同或是不同。具体地,在半导体元件的一剖视图中,其中一光学结构150的任一凸部1501的形状与另一光学结构150的任一凸部1501的形状可以相同或是不同。在本实施例中,在半导体元件的一剖视图中,位于第一侧46的光学结构150的任一凸部1501的形状为矩形。在半导体元件的一剖视图中,位于第二侧47的光学结构150的每一凸部1501的形状为矩形。共振腔区域103发出的辐

射具有一辐射图案。辐射自基板40逸散至半导体元件之外,且辐射的辐射图案可以被位于第一侧46的光学结构150的改变,且再被位于第二侧47的光学结构150改变。

126.图12a为本发明内容的第十实施例的半导体元件的剖视图。本发明内容的第十实施例的半导体元件包含与第七实施例大致上相同的结构,不同的地方在于,在半导体元件的一剖视图中,多个凸部1501的形状不同于图11a中所示的形状。在本实施例中,在半导体元件的一剖视图中,每一凸部1501的形状为三角形。

127.图12b为本发明内容的第十一实施例的半导体元件的剖视图。本发明内容的第十一实施例的半导体元件包含与第八实施例大致上相同的结构,不同的地方在于,在半导体元件的一剖视图中,多个凸部1501的形状不同于图11b中所示的形状。在本实施例中,在半导体元件的一剖视图中,每一凸部1501的形状为三角形。

128.图12c为本发明内容的第十二实施例的半导体元件的剖视图。本发明内容的第十二实施例的半导体元件包含与第九实施例大致上相同的结构,不同的地方在于,在半导体元件的一剖视图中,多个凸部1501的形状不同于图11c中所示的形状。在本实施例中,在半导体元件的一剖视图中,位于第二侧47的光学结构150的每一凸部1501的形状为三角形。在半导体元件的一剖视图中,位于第一侧46的光学结构150的每一凸部1501的形状为三角形。

129.图13a为本发明内容的第十三实施例的半导体元件的剖视图。本发明内容的第十三实施例的半导体元件包含与第七实施例大致上相同的结构,不同的地方如下所述。基板40的第二侧47包含顶表面41。光学结构150形成于顶表面41之上。在本实施例中,于半导体元件的一剖视图中,光学结构150包含多个凸部1501凸出于顶表面41。在半导体元件的一剖视图中,多个凸部1501的形状不同于图11a中所示的形状。在本实施例中,每一凸部1501的形状为半圆形。在一实施例中,光学结构150的材料不同于基板40的材料。光学结构150的材料包含硅、石英、二氧化硅或氟化钙(caf2)。

130.图13b为本发明内容的第十四实施例的半导体元件的剖视图。本发明内容的第十四实施例的半导体元件包含与第八实施例大致上相同的结构,不同的地方在于,在半导体元件的一剖视图中,多个凹部1502的形状不同于图11b中所示的形状。在本实施例中,在半导体元件的一剖视图中,每一凹部1502的形状为半圆形。

131.图13c为本发明内容的第十五实施例的半导体元件的剖视图。本发明内容的第十五实施例的半导体元件包含与第十三实施例大致上相同的结构,不同的地方在于,本实施例的半导体元件包含两个光学结构150。其中一半导体元件150位于第一侧46,且另一光学结构150位于第二侧47的顶表面41上。在本实施例中,在半导体元件的一剖视图中,位于第一侧46上的光学结构150的每一凸部1501的形状为半圆形。在半导体元件的一剖视图中,位于第二侧47的顶表面41上的光学结构150的每一凹部1502的形状为半圆形。

132.图14为本发明内容的第十六实施例的半导体元件的剖视图。本发明内容的第十六实施例的半导体元件包含与第十四实施例大致上相同的结构,不同的地方如下所述。半导体元件还包含一光学元件160与基板40的第二侧47连接。在本实施例中,基板40的第二侧47包含相对于半导体叠层10的顶表面41。光学元件160位于基板40的第二侧47的顶表面41上。光学元件160包含一第三侧1601、一第四侧1602以及一如前所揭示的光学结构150。相较于第四侧1602,第三侧1601较接近基板40。光学结构150位于第四侧1602。在本实施例中,光学元件160包含的材料与基板40的材料不同。优选的,共振腔区域103发出的辐射大致上可穿

透光学元件160的材料。在一实施例中,光学元件160的材料包含硅、石英、二氧化硅或氟化钙(caf2)。辐射通过光学元件160自基板40逸散至半导体元件之外,且辐射的辐射图案可以被光学元件160以及基板40的光学结构150改变。在另一实施例中,光学元件160位于基板40以及半导体叠层10之间。

133.图15为本发明内容的第十七实施例的半导体元件的剖视图。本发明内容的第十七实施例的半导体元件包含与第一实施例大致上相同的结构,不同的地方在于第二电极30并未含有如第一实施例中所揭示的电极垫部位31。在本实施例中,第一电极20以及第二电极30位于第一导电层50的同一侧。

134.本发明内容还提供一半导体封装(图未示)。半导体封装包含如前所揭示的第一实施例至第六实施例中的其中一半导体元件。半导体封装还包含一如第十六实施例中所揭示的光学元件160。光学元件160与半导体元件分离,且两者之间的距离不小于200μm。在一实施例中,半导体封装还包含一第一透镜(图未示),第一透镜位于光学元件160以及半导体装之间。在另一实施例中,光学元件160位于第一透镜以及半导体装之间。在一实施例中,半导体封装还包含一第二透镜(图未示)。第一透镜以及第二透镜位于光学元件160的两侧,且第一透镜或第二透镜位于光学元件160以及半导体元件之间。

135.本发明内容的又一实施例是依据前述实施例中的结构的结合或是改变。例如,在一实施例中,,图7所示的半导体元件可包含如图10所示的平台结构1021。

136.根据本发明内容的又一实施例,粘结层60包含透明导电氧化物、金属、绝缘氧化物或高分子。透明导电氧化物包含氧化铟锡(ito)、氧化铟(ino)、氧化锡(sno)、氧化镉锡(cto)、氧化锑锡(ato)、氧化铝锌(azo)、氧化锌锡(zto)、氧化镓锌(gzo)、氧化铟钨(iwo)、氧化锌(zno)或氧化铟锌(izo)。金属包含铟、锡、金、铂、钨、钛、铝、镍或其等的合金。绝缘氧化物包含氧化铝(alo

x

)、氧化硅(sio

x

)或氮氧化硅(sio

x

ny)。高分子材料包含环氧树脂(epoxy)、聚酰亚胺(polyimide)、八氟环丁烷(perfluorocyclobutane)、苯并环丁烯(benzocyclobutene,bcb)或硅氧树脂(silicone)。在一实施例中,如果粘结层60的材料包含金属,其厚度可以薄到让共振腔区域103发出的辐射穿透。在一实施例中,若粘结层60的材料包含透明导电氧化物,粘结层60具有一介于400纳米至5000纳米之间的厚度。

137.根据本发明内容的又一实施例,第二导电层70具有一实质上等于nλ/4的光学厚度,其中λ为共振腔区域103发出的辐射的峰值波长,且n为奇数的正整数。在一实施例中,第二导电层70包含透明导电氧化物,透明导电氧化物包含氧化铟锡(ito)、氧化铟(ino)、氧化锡(sno)、氧化镉锡(cto)、氧化锑锡(ato)、氧化铝锌(azo)、氧化锌锡(zto)、氧化镓锌(gzo)、氧化铟钨(iwo)、氧化锌(zno)或氧化铟锌(izo)。在一实施例中,第二导电层70包含石墨烯。共振腔区域103发出的辐射可穿透第二导电层70。

138.根据本发明内容的又一实施例,基板40具有一足够的厚度以支撑在基板40上的层或是结构。基板40的厚度例如为不小于50μm,且优选的,不超过250μm,又更佳的,不超过200μm。于本实施例中,基板40的厚度介于80μm至120μm之间。在一实施例中,基板40包含导电材料,例如硅。在另一实施例中,共振腔区域103发出的辐射可穿透基板40。在一实施例中,基板40包含氧化铝或是氮化铝。

139.根据本发明内容的又一实施例,成长基板100提供一上表面,其用于外延成长半导体叠层10。成长基板100具有一足够的厚度以支撑之后成长在成长基板100上的层或是结

构。优选地,成长基板100的厚度不小于100微米,且优选地,不超过250微米。成长基板100是单晶且包含半导体材料,例如,包含一个三五族半导体材料或是四族半导体材料。在一实施例中,成长基板100包含一具有一n型或p型的三五族半导体材料。在本实施例中,三五族半导体材料包含n型的砷化镓(gaas),n型掺杂物为硅(si)。

140.根据本发明内容的又一实施例,多重量子阱结构包含交叠的阱层以及阻障层。每一阻障层的能阶大于其中一阱层的能阶。共振腔区域103发出的辐射的峰值波长可以通过改变阱层的厚度或是材料而改变。优选地,阱层的材料包含三五族半导体材料,例如铝砷化镓(algaas)。阻障层的材料包含三五族半导体材料,例如铝砷化镓(algaas)。共振腔区域103可还包含一间隔层位于多重量子阱结构和第一反射结构101之间和/或位于多重量子阱结构和第二反射结构102之间,用于调整共振腔区域103的厚度以大致上接近或等于为n’λ/2的厚度,其中λ为共振腔区域103发射的辐射的峰值波长,并且n’为正整数。间隔层材料包含三五族半导体材料,例如铝砷化镓(algaas)。

141.根据本发明内容的又一实施例,第二半导体接触层105为p型。第二半导体接触层105具有一掺杂物,其掺杂浓度不小于10

18

/cm3,且优选地,不小于于10

19

/cm3,且更佳地,介于1

×

10

19

/cm3以及5

×

10

22

/cm3之间(两者都含)。第二半导体接触层105的材料包含三五族半导体材料,例如砷化镓(gaas)或铝砷化镓(algaas)。p型掺杂物为镁(mg)、碳(c)或锌(zn)。

142.根据本发明内容的又一实施例,第一半导体接触层104为n型。第一半导体接触层104具有掺杂物,其掺杂浓度不小于10

18

/cm3,且优选地,不小于10

19

/cm3,且更佳地,介于1

×

10

19

/cm3以及5

×

10

22

/cm3之间(两者都含)。第一半导体接触层104的材料包含三五族半导体材料,例如砷化镓(gaas)或铝砷化镓(algaas)。n型掺杂物为硅(si)或锑(te)。

143.根据本发明内容的又一实施例,第一绝缘层80以及第二绝缘层130包含绝缘材料,绝缘材料包含氧化铝(alo

x

)、氧化硅(sio

x

)氮化硅(si

x

ny)、氮氧化硅(sio

x

ny)环氧树脂(epoxy)、聚酰亚胺(polyimide)、八氟环丁烷(perfluorocyclobutane)、苯并环丁烯(benzocyclobutene,bcb)或硅氧树脂(silicone)。在一实施例中,第一绝缘层80的材料可以和第二绝缘层130的材料相同。在一实施例中,第一绝缘层80的材料与第二绝缘层130的材料不同。

144.根据本发明内容的又一实施例,蚀刻阻挡层106包含三五族半导体材料。蚀刻阻挡层106可以通过一蚀刻剂移除。蚀刻剂对于蚀刻阻挡层106的材料具有一第一蚀刻率,蚀刻剂对于第一半导体接触层104的材料具有一第二蚀刻率。第一蚀刻率不同于第二蚀刻率。优选的,第二蚀刻率大于第一蚀刻率。例如,第一半导体接触层104包含gaas,蚀刻阻挡层106包含ingap。蚀刻阻挡层106具有一掺杂物,其具有一掺杂浓度,蚀刻阻挡层106的掺杂物的掺杂浓度小于第一半导体接触层104的掺杂物的掺杂浓度。具体地,第一半导体接触层104的掺杂物的掺杂浓度至少为蚀刻阻挡层106的掺杂物的掺杂浓度的两倍。

145.根据本发明内容的又一实施例,第一电极20以及第二电极30用于与一外接电源连接且传导在两者之间的电流。第一电极20、第一导电层50以及第二电极30的材料包含透明导电氧化物或是金属。透明导电氧化物包含氧化铟锡(ito)、氧化铟(ino)、氧化锡(sno)、氧化镉锡(cto)、氧化锑锡(ato)、氧化铝锌(azo)、氧化锌锡(zto)、氧化镓锌(gzo)、氧化铟钨(iwo)、氧化锌(zno)或氧化铟锌(izo)。金属包含铟、锡、金、铂、钨、钛、铝、镍或其等的合金。

优选的,第一导电层50包含金属。

146.根据本发明内容的又一实施例,第一宽度w1、第二宽度w2、第三宽度w3、第四宽度w4、第一距离d1、第二距离d2、第三距离d3、金属接触层的最大宽度、第一电极20的最大宽度以及各导电区域107的宽度的量测方向大致上垂直于共振腔区域103的厚度方向t1。光学结构150的多个凸部1501的高度的量测方向大致上平行于共振腔区域103的厚度方向t1。

147.根据本发明内容的又一实施例,辐射包含光。在一实施例中,光可以为可见光。优选的,光具有一介于580nm至730nm之间的峰值波长。在另一实施例中,光可以为不可见光。优选的,光具有一介于730nm至1600nm之间的峰值波长,且更佳的,介于800nm至1000nm之间的峰值波长。

148.在一实施例中,电流限制层140通过一对的第一半导体层与相邻的第二半导体层与共振腔区域103分离。在另一实施例中,电流限制层140通过两对的第一半导体层与相邻的第二半导体层与共振腔区域103分离。在另一实施例中,电流限制层140直接与共振腔区域103接触。

149.在一实施例中,共振腔区域103还包含一第一导电型层以及一第二导电型层。第一导电型层以及一第二导电型层位于活性区域的两侧。第一导电型层以及一第二导电型层各具有一能阶,其大于其中一阻障层的能阶。具体地,第一导电型层以及一第二导电型层的能阶小于电流限制层140的导电部位1401的能阶。

150.在本实施例中,半导体元件可以通过倒装的方式与一包含电路的支撑载板结合,且大部分的光会通过基板40逸散至半导体元件外。

151.半导体元件可应用于例如为接近感测器、夜视系统、血氧侦测器等、或数据传输。

152.外延的方法包含,但不限于,金属有机化学气相沉积(metal-organic chemical vapor deposition,mocvd)、氢化物气相外延法(hydride vapor phase epitaxy,hvpe)、分子束外延(molecular beam epitaxy,mbe)或液相外延法(liquid-phase epitaxy,lpe)。

153.需注意的是,本发明所列举的各实施例仅用以说明本发明,并非用以限制本发明的范围。任何人对本发明所作显而易见的修饰或变更都不脱离本发明的精神与范围。不同实施例中相同或相似的构件,或者不同实施例中具相同标号的构件都具有相同的物理或化学特性。此外,本发明中上述的实施例在适当的情况下,是可互相组合或替换,而非仅限于所描述的特定实施例。在一实施例中详细描述的特定构件与其他构件的连接关系也可以应用于其他实施例中,且均落于附上的本发明的权利要求保护范围的范畴中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1