半导体结构及其制备方法与流程

本公开涉及半导体集成电路制造,特别是涉及一种半导体结构及其制备方法。

背景技术:

1、动态随机存储器(dynamic random access memory,简称dram)是一种高速地、随机地写入和读取数据的半导体存储器,被广泛地应用到数据存储设备或装置中。dram由多个重复的存储单元组成。每个存储单元通常包括电容结构和晶体管,晶体管的栅极与字线相连、漏极与位线相连、源极与电容结构相连。

2、目前,随着半导体技术的发展,尤其是在半导体工艺进入深亚微米及纳米阶段后,dram中各组成元件的尺寸及相邻元件之间的间距也越来越小,并广泛应用了高深宽比离子刻蚀技术进行部分元件的制备。例如,在制备焊盘层时,需要先形成焊盘材料层,然后再利用高深宽比离子刻蚀技术图形化焊盘材料层以形成焊盘。然而,随着dram中各组成元件的尺寸及相邻元件之间的间距越来越小,采用前述方法制备的焊盘容易发生倒塌,导致影响dram的生产良率。

3、由上,如何有效避免采用高深宽比离子刻蚀技术制备的焊盘发生倒塌,也成为了相关技术中一个亟待解决的难题。

技术实现思路

1、基于此,本公开实施例提供了一种半导体结构及其制备方法,可以提高焊盘的制备稳定性,以降低焊盘倒塌的风险,从而有效提升半导体结构的生产良率。

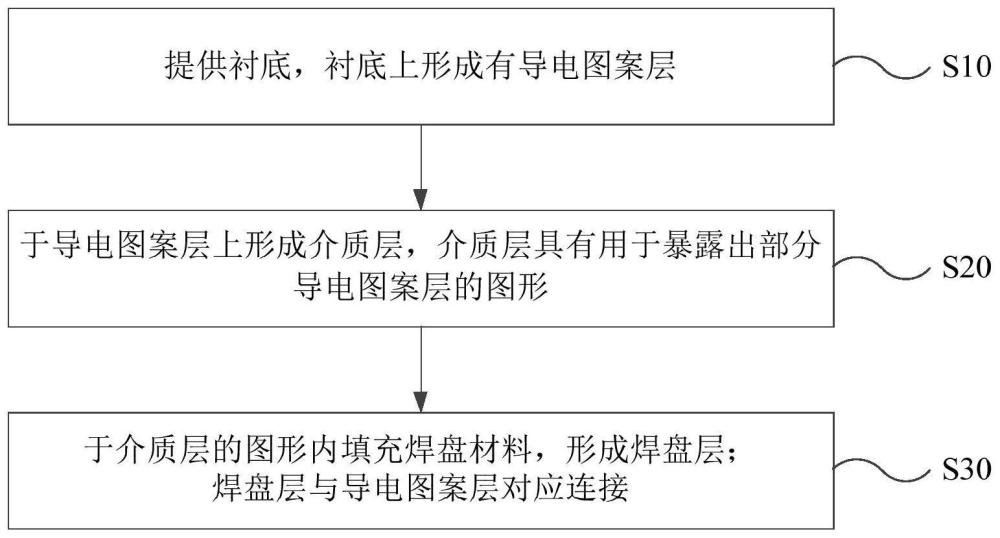

2、一方面,本公开一些实施例提供了一种半导体结构的制备方法,包括:提供衬底,所述衬底上形成有导电图案层;于所述导电图案层上形成介质层,所述介质层具有用于暴露出部分所述导电图案层的图形;于所述介质层的所述图形内填充焊盘材料,形成焊盘层;所述焊盘层与所述导电图案层对应连接。

3、在本公开一些实施例中,所述形成焊盘层之前,所述制备方法还包括:研磨填充所述焊盘材料后的所得结构。

4、在本公开一些实施例中,所述形成焊盘层之前,所述制备方法还包括:对研磨后的所得结构进行清洗。

5、在本公开一些实施例中,所述形成焊盘层之后,所述制备方法还包括:对形成所述焊盘层后的所得结构执行切筋成型工艺,形成多个焊盘;其中,所述导电图案层包括多个导电部;所述焊盘与所述导电部对应连接。

6、在本公开一些实施例中,所述衬底包括单元阵列区以及位于所述单元阵列区旁侧的核心电路区;其中,位于所述单元阵列区内的所述焊盘为接触衬垫,位于所述单元阵列区内的所述导电部为导电接触结构;所述接触衬垫与所述导电接触结构对应连接,且所述接触衬垫在所述衬底上的正投影位于所述导电接触结构在所述衬底上的正投影一侧,并与所述导电接触结构在所述衬底上的正投影部分重叠。

7、在本公开一些实施例中,所述于所述导电图案层上形成介质层,包括:于所述导电图案层上依次层叠第一介质材料层和第二介质材料层,并对所述第一介质材料层和所述第二介质材料层执行第一次构图工艺,形成第一初始介质层和第二初始介质层。

8、在本公开一些实施例中,所述第一次构图工艺包括自对准双重成像工艺或自对准四重成像工艺。

9、在本公开一些实施例中,所述第一介质材料层的形成厚度大于所述第二介质材料层的形成厚度。

10、在本公开一些实施例中,所述衬底包括单元阵列区以及位于所述单元阵列区旁侧的核心电路区;所述对所述第一介质材料层和所述第二介质材料层执行第一次构图工艺,包括:在所述第一介质材料层和所述第二介质材料层位于所述单元阵列区内的部分中形成网格图形,在所述第一介质材料层和所述第二介质材料层位于所述核心电路区内的部分中形成线性图形。

11、在本公开一些实施例中,所述对形成所述焊盘层后的所得结构执行切筋成型工艺,包括:

12、于所述第二初始介质层及所述焊盘层上形成掩模;所述掩模具有切筋图案;基于所述切筋图案,对所述第一初始介质层和所述第二初始介质层执行第二次构图工艺,形成第一介质层和第二介质层;去除所述掩模及所述第二介质层,形成多个所述焊盘。

13、在本公开一些实施例中,所述于所述第二初始介质层及所述焊盘层上形成掩模,包括:于所述第二初始介质层及所述焊盘层上形成阻挡材料层,于所述阻挡材料层上形成所述掩模;所述制备方法还包括:基于所述切筋图案,对所述阻挡材料层、所述第一初始介质层和所述第二初始介质层同步执行所述第二次构图工艺,形成阻挡层、所述第一介质层和所述第二介质层;以及,去除所述阻挡层。

14、在本公开一些实施例中,所述阻挡层与所述第二介质层均为氧化物层;所述阻挡层和所述第二介质层同步去除。

15、另一方面,本公开一些实施例提供了一种半导体结构,所述半导体结构包括:衬底;导电图案层,设置于所述衬底上;所述导电图案层包括多个导电部;第一介质层,设置于所述导电图案层上;所述第一介质层具有图形,所述图形暴露出部分所述导电图案层;多个焊盘,填充于所述第一介质层的所述图形内;所述焊盘与所述导电部对应连接。

16、在本公开一些实施例中,以所述衬底为基准,所述焊盘背离所述衬底的表面高于所述第一介质层背离所述衬底的表面。

17、在本公开一些实施例中,所述衬底包括单元阵列区以及位于所述单元阵列区旁侧的核心电路区;其中,位于所述单元阵列区内的所述焊盘为接触衬垫,位于所述单元阵列区内的所述导电部为导电接触结构;所述接触衬垫与所述导电接触结构对应连接,且所述接触衬垫在所述衬底上的正投影位于所述导电接触结构在所述衬底上的正投影一侧,并与所述导电接触结构在所述衬底上的正投影部分重叠。

18、本公开实施例提供的半导体结构及其制备方法如上所述。在本公开实施例中,优化了焊盘的制备流程。在制备焊盘层之前,先于导电图案层上形成介质层,该介质层具有用于暴露出部分导电图案层的图形,可以用来定义焊盘层的图形。基于此,在介质层的图形内填充焊盘材料,即可形成焊盘层。如此,本公开实施例通过先定义焊盘层图形再填充焊盘材料来形成焊盘层的方法,可以提高焊盘层中各焊盘的制备稳定性,尤其是针对具有较高深宽比的焊盘,从而有效降低焊盘层中焊盘倒塌的风险,进而有效提升半导体结构的生产良率。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述形成焊盘层之前,所述制备方法还包括:

3.根据权利要求2所述的半导体结构的制备方法,其特征在于,所述形成焊盘层之前,所述制备方法还包括:对研磨后的所得结构进行清洗。

4.根据权利要求1所述的半导体结构的制备方法,其特征在于,所述形成焊盘层之后,所述制备方法还包括:

5.根据权利要求4所述的半导体结构的制备方法,其特征在于,所述衬底包括单元阵列区以及位于所述单元阵列区旁侧的核心电路区;其中,

6.根据权利要求4所述的半导体结构的制备方法,其特征在于,

7.根据权利要求6所述的半导体结构的制备方法,其特征在于,所述第一次构图工艺包括自对准双重成像工艺或自对准四重成像工艺。

8.根据权利要求6所述的半导体结构的制备方法,其特征在于,所述第一介质材料层的形成厚度大于所述第二介质材料层的形成厚度。

9.根据权利要求6所述的半导体结构的制备方法,其特征在于,所述衬底包括单元阵列区以及位于所述单元阵列区旁侧的核心电路区;

10.根据权利要求6所述的半导体结构的制备方法,其特征在于,所述对形成所述焊盘层后的所得结构执行切筋成型工艺,包括:

11.根据权利要求10所述的半导体结构的制备方法,其特征在于,所述于所述第二初始介质层及所述焊盘层上形成掩模,包括:于所述第二初始介质层及所述焊盘层上形成阻挡材料层,于所述阻挡材料层上形成所述掩模;

12.根据权利要求11所述的半导体结构的制备方法,其特征在于,所述阻挡层与所述第二介质层均为氧化物层;所述阻挡层和所述第二介质层同步去除。

13.一种半导体结构,其特征在于,所述半导体结构包括:

14.根据权利要求13所述的半导体结构,其特征在于,以所述衬底为基准,所述焊盘背离所述衬底的表面高于所述第一介质层背离所述衬底的表面。

15.根据权利要求13所述的半导体结构,其特征在于,所述衬底包括单元阵列区以及位于所述单元阵列区旁侧的核心电路区;其中,

技术总结

本公开涉及一种半导体结构及其制备方法。所述半导体结构的制备方法,包括:提供衬底,衬底上形成有导电图案层;于导电图案层上形成介质层,介质层具有用于暴露出部分导电图案层的图形;于介质层的图形内填充焊盘材料,形成焊盘层;焊盘层与导电图案层对应连接。本公开实施例可以提高焊盘的制备稳定性,以降低焊盘倒塌的风险,从而有效提升半导体结构的生产良率。

技术研发人员:曹新满

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!