半导体封装载板结构及其制法的制作方法

本发明有关一种半导体封装制程,尤指一种可提高可靠度的半导体封装 载板结构及其制法。

背景技术:

1、随着产业应用的发展,近年来应用于网通服务器、高速运算、人工智能 (ai)等半导体芯片需要的功能愈来愈多元化,且性能愈来愈高,因而可靠性 要求也随之提高。

2、目前高可靠度要求用电子封装件1(如图1a所示,例如为车用电子封装 件)于封装时,为了确保焊锡状态是否良好,可借由外观检测其四周接脚是 否均有爬锡至侧壁的铜垫上(如图1b所示的焊垫111与焊锡材料18)。例 如,于承载半导体芯片用的载板11的接脚处可形成一半凹槽结构13,其中, 该载板11可为如图1c所示的封装线路载板(可于焊垫111上先镀上全铜, 再蚀刻该焊垫111的侧壁形成该半凹槽结构13)。

3、图1d为现有电子封装件1于切单制程前的剖面示意图。如图1d所示, 该电子封装件1提供一条状基材10,其包含多个相连的载板11,再于该条状 基材10的切割路径s上形成凹槽12,以将该条状基材10以其凹槽12的侧 结合至一封装模封用的承载件8上,其中,该条状基材10的凹槽12的底部 具有绝缘块体14,其齐平于该凹槽12的底部,且该绝缘块体14的材质与该 载板11的介电层110的材质相同。之后,于该载板11的置晶侧上进行封装 制程,以将半导体元件16设于该载板11上,再以模封层17包覆该半导体元 件16。最后,沿该切割路径s进行切单制程,以获取该电子封装件1,且该 载板11于其焊垫侧上的焊垫111形成一半凹槽结构13。

4、于后续组装作业中,将该电子封装件1以其焊垫111(表面可形成表面 处理层,例如镍金层)借由焊锡材料18接置于一电路板1b(如图1b所示) 上。

5、现有电子封装件1的制法中,该条状基材10极薄,且该条状基材10的 凹槽12的空间过大,故于形成该模封层17时,该条状基材10容易因模具内 的注胶压力,且该载板11与封装模封用的承载件8之间的中空处需抽取为真 空状态而令该条状基材10承受强大压力等因素,致使该条状基材10会沿该 凹槽12处塌陷变形甚至容易因而产生微裂缝,导致该模封层17的胶材会由 该载板11的置晶侧渗流至该载板11的凹槽12内而污染焊垫111。

6、再者,由于自该模封层17渗入的胶材会溢流至该载板11的半凹槽结构 13上,因而阻挡了该焊锡材料18的爬锡路径与功能,且该渗入的胶材更会 遮挡该半凹槽结构13,使该半凹槽结构13失去观测焊锡爬锡状态的主要功 能。

7、因此,如何克服上述现有技术的种种问题,实已成为目前业界亟待克服 的难题。

技术实现思路

1、鉴于上述现有技术的种种缺失,本发明提供一种半导体封装载板结构及 其制法,可至少部分地解决现有技术中的问题。

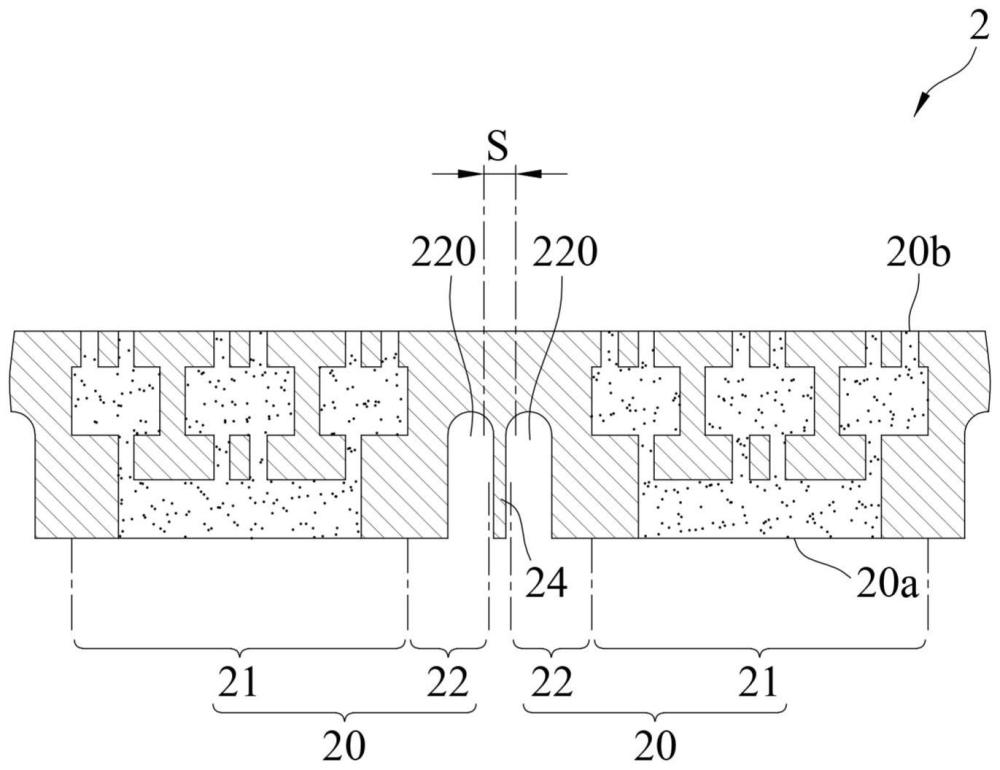

2、本发明的半导体封装载板结构,包括:多个载板本体,其包含增层线路 结构及多个导电块,且该多个载板本体定义有相对的第一表面与第二表面, 而该多个导电块设于该增层线路结构的至少相对二侧的周面上并与该增层线 路结构电性连接,其中,该第一表面及/或该第二表面具有多个的电性连接垫 以结合外部元件,且该多个导电块所形成的区域定义有切割路径,并使该多 个载板本体于对应该多个导电块上的该第一表面上分别设有一开口;以及多 个支撑凸块,其竖立于相邻的二该开口之间,并与该切割路径相叠合,且该支撑凸块的其中一端与该开口的底部相结合并凸出该开口的底部,而另一端 的表面凹入或齐平于该载板本体的第一表面。

3、前述的半导体封装载板结构中,相邻的二该载板本体之间以该导电块相 接以形成一体式结构,且该支撑凸块为金属凸块。

4、前述的半导体封装载板结构中,相邻的二该载板本体之间以该多个导电 块借由该支撑凸块相连接,且该支撑凸块为绝缘块体。例如,该支撑凸块的 周身轮廓呈凹凸状。进一步,该支撑凸块具有一横向部而呈十字状,且该横 向部的其中一部分嵌入于该导电块内。或者,该支撑凸块具有至少二个横向 部,且其中一该横向部的部分或全部嵌入于该导电块内,而另一该横向部作 为该支撑凸块的一端部。甚至于,该开口的底部的最底面低于作为该支撑凸 块一端部的该横向部。

5、前述的半导体封装载板结构中,该支撑凸块的宽度不大于该切割路径的 宽度。

6、前述的半导体封装载板结构中,该开口的底部与侧壁的相接处呈凹弧面。

7、本发明亦提供一种半导体封装载板结构的制法,包括:提供一具有金属 表面的承载板;以线路增层制程形成包含增层线路结构及多个导电块的多个 载板本体于该承载板上,其中,该多个载板本体定义有相对的第一表面与第 二表面,且该多个载板本体以该第二表面结合至该承载板的金属表面,又于 该增层线路结构的至少相对二侧的周面上分别形成该多个导电块,并使该多 个导电块与该增层线路结构电性连接,而相邻的该载板本体以各自相对应的 该导电块相接而呈一体式,且该多个导电块相邻接的区域定义有切割路径; 以图案化制程于该多个载板本体的第一表面上形成防蚀刻阻障层,且露出该 多个导电块的部分表面,其中,覆盖于该切割路径处的该防蚀刻阻障层的宽 度不大于该切割路径的宽度;以蚀刻制程移除该多个导电块露出处的部分材 料,以于该多个导电块上各形成一呈盲孔状的开口,且该多个导电块对应于 该切割路径处未被蚀刻而保留的部分作为支撑凸块;移除该防蚀刻阻障层, 以令该载板本体的第一表面及该开口露出;以及移除该承载板,以露出该载 板本体的第二表面。

8、前述的制法中,还包括于移除该承载板之前,于该开口的表面及该支撑 凸块所露出的表面上形成一表面处理层。

9、本发明另提供一种半导体封装载板结构的制法,包括:提供一具有金属 表面的承载板;以线路增层制程形成包含增层线路结构及多个导电块的多个 载板本体于该承载板上,其中,该多个载板本体定义有相对的第一表面与第 二表面,且该多个载板本体以该第二表面结合至该承载板的金属表面,又于 该增层线路结构的至少相对二侧的周面上分别形成该多个导电块,并使该多 个导电块与该增层线路结构电性连接,而相邻的该多个载板本体的各自相对 应的该多个导电块之间具有间隙而呈分离状,并且以绝缘材填满该间隙,且 相邻的该多个载板本体之间由该多个导电块与该绝缘材所形成的区域定义有 切割路径,其中,该切割路径处的该绝缘材的宽度不大于该切割路径的宽度; 以图案化制程于该多个载板本体的该第一表面上形成防蚀刻阻障层,且该防 蚀刻阻障层露出该切割路径处;以蚀刻制程移除该多个导电块露出处的部分 材料,以各自形成一呈盲孔状的开口,而该切割路径处未被蚀刻而保留的该 绝缘材作为支撑凸块;移除该防蚀刻阻障层,以露出该多个载板本体的该第 一表面及这些开口;以及移除该承载板,以露出该多个载板本体的该第二表 面。

10、前述的制法中,还包括于移除该承载板之前,于该开口的表面上形成一 表面处理层。

11、前述的制法中,该支撑凸块的周身轮廓形成为凹凸状。例如,该支撑凸 块形成有一横向部,以令该支撑凸块的轮廓呈十字状,且该横向部的部分嵌 入于该导电块内。进一步,该支撑凸块形成有至少二个相互间隔排列的横向 部,且其中一该横向部的部分或全部嵌入于该导电块内,而另一该横向部形 成为该支撑凸块的一端部。

12、前述的制法中,该相邻多个载板本体间于该第一表面侧各自相对应的该 多个导电块连接结合为一体;其中,该防蚀刻阻障层露出该多个导电块的部 分表面,且露出部分的宽度大于该切割路径的宽度;其中,以蚀刻制程移除 该多个导电块露出处的部分材料,以于该多个导电块上各自形成一呈盲孔状 的开口,且相邻接的该开口相连通以露出该绝缘材作为支撑凸块。例如,该 支撑凸块的周身轮廓形成为呈凹凸状。进一步,该支撑凸块形成有至少二个 相互间隔排列的横向部,且其中一该横向部的全部嵌入于该导电块内,而另一该横向部形成为该支撑凸块的一端部。或者,该开口的底部的最底面低于 作为该支撑凸块一端部的该横向部。

13、前述的各制法中,还包括于移除该承载板之后,将多个半导体元件设于 该多个载板本体的第二表面上并电性连接该增层线路结构,且形成一模封层 于该多个载板本体的第二表面上以覆盖该多个半导体元件。又可包括于形成 该模封层后,沿该切割路径执行切割制程,以移除该支撑凸块,以获取多个 单体状的半导体封装件。

14、由上可知,本发明的半导体封装载板结构及其制法中,主要借由该支撑 凸块的设计,以将现有凹槽处隔成两开口,不仅缩小现有凹槽的空间,且提 供该载板本体用于封装模封承载件上的支撑功能,故相较于现有技术,当形 成该模封层时,该载板本体能承受灌胶的高压,且不会因高压变形而破裂, 可有效避免该模封层的胶材会溢流至该载板本体的第一表面而衍生污染焊垫 的问题。

15、再者,由于该模封层的胶材不会溢流至该载板本体的第一表面,因而该 模封层的胶材不会遮挡该开口,故该半导体封装载板结构的开口于后续所形 成的半开口结构不会失去观测焊锡爬锡状态的主要功能。

- 还没有人留言评论。精彩留言会获得点赞!