半导体结构及其形成方法与流程

本发明涉及半导体制造,尤其涉及一种半导体结构及其形成方法。

背景技术:

1、金属-氧化物-半导体场效应晶体管(mosfet)是现代集成电路中最重要的元件之一,mosfet的基本结构包括:半导体衬底;位于半导体衬底表面的栅极结构,所述栅极结构包括:位于半导体衬底表面的栅介质层以及位于栅介质层表面的栅电极层;位于栅极结构两侧半导体衬底中的源漏掺杂区。

2、随着半导体技术的发展,传统的平面式的mosfet对沟道电流的控制能力变弱,造成严重的漏电流。鳍式场效应晶体管(fin fet)是一种新兴的多栅器件,它一般包括凸出于半导体衬底表面的鳍部,覆盖部分所述鳍部的顶部表面和侧壁的栅极结构,位于栅极结构两侧的鳍部中的源漏掺杂区。与平面式的mosfet相比,鳍式场效应晶体管具有更强的短沟道抑制能力,具有更强的工作电流。

3、随着半导体技术的进一步发展,传统的鳍式场效应晶体管在进一步增大工作电流方面存在限制。具体的,由于鳍部中只有靠近顶部表面和侧壁的区域用来作为沟道区,使得鳍部中用于作为沟道区的体积较小,这对增大鳍式场效应晶体管的工作电流造成限制。因此,提出了一种(gate all around,gaa)结构的mosfet,使得用于作为沟道区的体积增加,进一步的增大了gaa结构mosfet的工作电流。

4、然而,现有技术中gaa的器件结构中仍存在诸多问题。

技术实现思路

1、本发明解决的技术问题是提供一种半导体结构及其形成方法,以提升最终形成的半导体结构的性能。

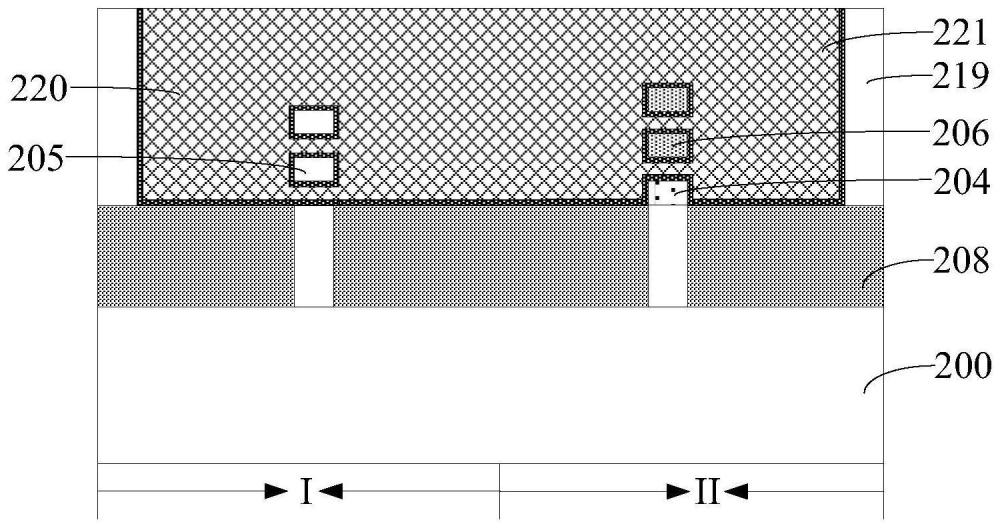

2、为解决上述问题,本发明技术方案中提供一种半导体结构,包括:衬底,所述衬底包括第一区和第二区;位于所述第一区上的第一鳍部结构,所述第一鳍部结构包括若干层沿所述衬底表面法线方向重叠排布的第一沟道层,所述第一沟道层的材料采用掺杂有第一掺杂离子的硅或采用非掺杂的硅;位于所述第二区上的第二鳍部结构,所述第二鳍部结构包括隔断沟道层、以及位于是隔断沟道层上的若干第二沟道层,所述隔断沟道层和若干所述第二沟道层沿所述衬底表面法线方向重叠排布,所述第二沟道层内的材料采用掺杂有第二掺杂离子的硅锗,所述隔断沟道层的材料采用掺杂有第三掺杂离子的硅,所述第二掺杂离子分别与所述第三掺杂离子和所述第一掺杂离子的电学类型不同,所述第三掺杂离子与所述第一掺杂离子的电学类型相同,且所述第一掺杂离子和所述第三掺杂离子为电学相同类型中的不同离子,所述隔断沟道层内所述第三掺杂离子的掺杂浓度使得晶体管工作时所述隔断沟道层不能被导通。

3、可选的,所述第一掺杂离子为n型离子;所述第二掺杂离子为p型离子;所述第三掺杂离子为n型离子。

4、可选的,还包括:位于所述衬底上的横跨所述第一鳍部结构的第一栅极结构,所述第一栅极结构包围所述第一沟道层;位于所述衬底上的横跨所述第二鳍部结构的第二栅极结构,所述第二栅极结构包围所述隔断沟道层和所述第二沟道层。

5、可选的,还包括:位于所述衬底内的隔离沟槽;位于所述隔离沟槽的隔离层,所述隔离层的顶部表面齐平于所述隔断沟道层的底部表面。

6、可选的,还包括:位于所述第一鳍部结构内的第一源漏掺杂层,所述第一源漏掺杂层内具有第一源漏离子;位于所述第二鳍部结构内的第二源漏掺杂层,所述第二源漏掺杂层内具有第二源漏离子,所述第一源漏离子和所述第二源漏离子的电学类型不同。

7、可选的,所述第一源漏离子为n型离子;所述第二源漏离子为p型离子。

8、可选的,还包括:位于所述第一栅极结构和所述第二栅极结构侧壁的侧墙;位于所述第一沟道层和所述衬底之间、以及相邻的所述第一沟道层之间的第一阻挡层;位于相邻的所述隔断沟道层和所述第二沟道层、以及相邻所述第二沟道层之间的第二阻挡层。

9、可选的,还包括:位于所述衬底上的介质层,所述介质层覆盖所述第一栅极结构、第二栅极结构以及侧墙,且所述介质层暴露出所述第一栅极结构、第二栅极结构以及侧墙的顶部表面。

10、相应的,本发明技术方案中还提供一种半导体结构的形成方法,包括:提供衬底,所述衬底包括第一区和第二区;在所述第一区上形成第一鳍部结构,所述第一鳍部结构包括若干层沿所述衬底表面法线方向重叠排布的第一沟道层,所述第一沟道层的材料采用掺杂有第一掺杂离子的硅或采用非掺杂的硅;在所述第二区上形成第二鳍部结构,所述第二鳍部结构包括隔断沟道层、以及位于是隔断沟道层上的若干第二沟道层,所述隔断沟道层和若干所述第二沟道层沿所述衬底表面法线方向重叠排布,所述第二沟道层的材料采用掺杂有第二掺杂离子的硅锗,所述隔断沟道层的材料采用掺杂有第三掺杂离子的硅,所述第二掺杂离子分别与所述第三掺杂离子和所述第一掺杂离子的电学类型不同,所述第三掺杂离子与所述第一掺杂离子的电学类型相同,且所述第一掺杂离子和所述第三掺杂离子为电学相同类型中的不同离子,所述隔断沟道层内所述第三掺杂离子的掺杂浓度使得晶体管工作时所述隔断沟道层不能被导通。

11、可选的,所述第一掺杂离子为n型离子;所述第二掺杂离子为p型离子;所述第三掺杂离子为n型离子。

12、可选的,在形成所述第一鳍部结构和所述第二鳍部结构之后,还包括:在所述衬底上形成横跨所述第一鳍部结构的第一栅极结构,所述第一栅极结构包围所述第一沟道层;在所述衬底上形成横跨所述第二鳍部结构的第二栅极结构,所述第二栅极结构包围所述隔断沟道层和所述第二沟道层。

13、可选的,在形成所述第一鳍部结构和所述第二鳍部结构之前,还包括:在所述衬底上形成隔断沟道材料层、若干第一沟道材料层以及若干第二沟道材料层,所述第一沟道材料层位于相邻的所述隔断沟道材料层和所述第二沟道材料层之间、或相邻的所述第二沟道材料层之间。

14、可选的,在形成所述隔断沟道材料层、第一沟道材料层以及第二沟道材料层之后,还包括:对所述隔断沟道材料层、若干所述第一沟道材料层以及若干所述第二沟道材料层进行图形化处理,形成第一初始鳍部结构和第二初始鳍部结构,所述第一初始鳍部结构包括所述隔断沟道层、若干所述第一沟道层以及若干所述第二沟道层,所述第一沟道层位于相邻的所述隔断沟道层和所述第二沟道层之间、或相邻的所述第二沟道层之间,所述第二初始鳍部结构包括所述隔断沟道层、若干所述第一沟道层以及若干所述第二沟道层,所述第一沟道层位于相邻的所述隔断沟道层和所述第二沟道层之间、或相邻的所述第二沟道层之间。

15、可选的,在所述图形化处理的过程中,还包括:刻蚀所述衬底,在所述衬底内形成隔离沟槽;在所述图形化处理之后,还包括:在所述隔离沟槽内形成隔离层,所述隔离层的顶部表面齐平于所述隔断沟道层的底部表面。

16、可选的,在形成所述第一初始鳍部结构和所述第二初始鳍部结构之后,还包括:在所述衬底上形成横跨相邻所述第一初始鳍部结构和所述第二初始鳍部结构的伪栅结构;在所述伪栅结构的侧壁和顶部表面形成侧墙材料层;在所述衬底上形成第一图形化层,所述第一图形化层暴露出所述第二区上的所述侧墙材料层;以所述第一图形化层为掩膜刻蚀所述侧墙材料层,直至暴露出所述伪栅结构的顶部表面为止,在所述第二区的所述伪栅结构侧壁形成侧墙;以所述第一图形化层、以及位于所述第二区上的所述伪栅结构和所述侧墙为掩膜,刻蚀所述第二初始鳍部结构,在所述第二初始鳍部结构内形成第二源漏开口;刻蚀所述第二源漏开口暴露出的部分所述第一沟道层,形成第二凹槽;去除所述第一图形化层;在去除所述第一图形化层之后,在所述第一区和所述第二区上沉积第二阻挡层薄膜;在所述衬底上形成第二图形化层,所述第二图形化层暴露出所述第二区上的所述第二阻挡层薄膜;以所述第二图形化层为掩膜刻蚀所述第二阻挡层薄膜,在所述第二凹槽内形成第二阻挡层;在形成所述第二阻挡层之后,去除所述第二图形化层;在去除所述第二图形化层之后,在所述第二源漏开口内形成第二源漏掺杂层,所述第二源漏掺杂层内具有第二源漏离子;在形成所述第二源漏掺杂层之后,在所述衬底上形成第三图形化层,所述第三图形化层暴露出所述第一区上的所述侧墙材料层和所述第二阻挡层薄膜;以所述第三图形化层为掩膜刻蚀所述侧墙材料层和所述第二阻挡层薄膜,直至暴露出所述伪栅结构的顶部表面为止,在所述第一区的所述伪栅结构侧壁形成侧墙;以所述第三图形化层、以及位于所述第一区上的所述伪栅结构和所述侧墙为掩膜,刻蚀所述第一初始鳍部结构,在所述第一初始鳍部结构内形成第一源漏开口;刻蚀所述第一源漏开口暴露出的部分所述隔断沟道层和部分所述第二沟道层,形成第一凹槽;去除所述第三图形化层;在去除所述第三图形化层之后,在所述第一区和所述第二区上沉积第一阻挡层薄膜;在所述衬底上形成第四图形化层,所述第四图形化层暴露出所述第一区上的所述第一阻挡层薄膜;以所述第四图形化层为掩膜刻蚀所述第一阻挡层薄膜,在所述第一凹槽内形成第一阻挡层;在形成所述第一阻挡层之后,去除所述第四图形化层;在去除所述第四图形化层之后,在所述第一源漏开口内形成第一源漏掺杂层,所述第一源漏掺杂层内具有第一源漏离子,所述第一源漏离子和所述第二源漏离子的电学类型不同;清洗去除在所述第二源漏掺杂层上的所述第一阻挡层薄膜;在所述衬底上形成介质层,所述介质层覆盖所述伪栅结构、侧墙、第一源漏掺杂层和第二源漏掺杂层,且所述介质层暴露出所述伪栅结构和所述侧墙的顶部表面。

17、可选的,所述第一源漏离子为n型离子;所述第二源漏离子为p型离子。

18、可选的,所述第一鳍部结构和所述第二鳍部结构的形成方法包括:在所述介质层上形成第五图形化层,所述第五图形化层暴露出位于所述第二区上的所述伪栅结构顶部表面;以所述第五图形化层为掩膜去除位于所述第二区上的所述伪栅结构,形成第二栅极开口;在形成所述第二栅极开口之后,去除所述第二栅极开口暴露出的所述第一沟道层,形成第二栅极凹槽以及所述第二鳍部结构;在形成所述第二鳍部结构之后,去除所述第五图形化层且在所述介质层上形成第六图形化层,所述第六图形化层暴露出位于所述第一区上的所述伪栅结构顶部表面;以所述第六图形化层为掩膜去除位于所述第一区上的所述伪栅结构,形成第一栅极开口;在形成所述第一栅极开口之后,去除所述第一栅极开口暴露出的所述隔断沟道层和所述第二沟道层,形成第一栅极凹槽以及所述第一鳍部结构;在形成所述第二鳍部结构之后,去除所述第六图形化层。

19、可选的,所述第一栅极结构和所述第二栅极结构的形成方法包括:在所述第一栅极开口、第一栅极凹槽、第二栅极开口以及第二栅极凹槽内形成栅氧化层,所述栅氧化层包围所述第一沟道层、隔断沟道层和第二沟道层;在所述栅氧化层表面形成第二栅极功函数层;在所述衬底上形成第七图形化层,所述第七图形化层暴露出位于所述第一区上的所述第二栅极功函数层;以所述第七图形化层为掩膜,去除位于所述第一区上的所述第二栅极功函数层;去除所述第七图形化层;在所述第一区的所述栅氧化层表面、以及所述第二区的所述第二栅极功函数层的表面形成第一栅极功函数层;在所述第一栅极功函数层上、以及所述介质层上形成栅极材料层;对所述栅极材料层进行平坦化处理,直至暴露出所述介质层的表面为止,形成栅极层,由位于所述第一区的所述栅氧化层、第一栅极功函数层、以及栅极层形成所述第一栅极结构,由所述第二区的所述栅氧化层、第一栅极功函数层、第二栅极功函数层以及栅极层形成所述第二栅极结构。

20、与现有技术相比,本发明的技术方案具有以下优点:

21、本发明的技术方案的半导体结构中,通过采用具有第二掺杂离子的硅锗材料的所述第二沟道层作为pmos晶体管的沟道区,能够满足所述pmos晶体管对空穴迁移率的需求,进而有效提升最终形成的半导体结构的性能。通过增设所述隔断沟道层,所述隔断沟道层的材料采用掺杂有第三掺杂离子的硅,且所述第三掺杂离子与所述第二沟道层内的所述第二掺杂离子的电学类型相反,使得在所述pmos晶体管底部形成的寄生晶体管与所述pmos晶体管类型相反,进而有效减少所述pmos晶体管底部漏电的问题。

22、本发明的技术方案的半导体结构的形成方法中,通过采用具有第二掺杂离子的硅锗材料的所述第二沟道层作为pmos晶体管的沟道区,能够满足所述pmos晶体管对空穴迁移率的需求,进而有效提升最终形成的半导体结构的性能。通过增设所述隔断沟道层,所述隔断沟道层的材料采用掺杂有第三掺杂离子的硅,且所述第三掺杂离子与所述第二沟道层内的所述第二掺杂离子的电学类型相反,使得在所述pmos晶体管底部形成的寄生晶体管与所述pmos晶体管类型相反,进而有效减少所述pmos晶体管底部漏电的问题。而且所述隔断沟道层位于所述第二沟道层的下方,使得在后续形成第一栅极结构时,仅对位于包覆于所述隔断沟道层上的第二栅极结构造成损伤,不会对包覆于所述第二沟道层上的第二栅极结构造成损伤,以此降低对所述pmos晶体管阈值电压的影响,提升最终形成的半导体结构的性能。

23、进一步,所述第一栅极结构和所述第二栅极结构的形成方法包括:在所述第一栅极开口、第一栅极凹槽、第二栅极开口以及第二栅极凹槽内形成栅氧化层,所述栅氧化层包围所述第一沟道层、隔断沟道层和第二沟道层;在所述栅氧化层表面形成第二栅极功函数层;在所述衬底上形成第七图形化层,所述第七图形化层暴露出位于所述第一区上的所述第二栅极功函数层;以所述第七图形化层为掩膜,去除位于所述第一区上的所述第二栅极功函数层;去除所述第七图形化层;在所述第一区的所述栅氧化层表面、以及所述第二区的所述第二栅极功函数层的表面形成第一栅极功函数层;在所述第一栅极功函数层上、以及所述介质层上形成栅极材料层;对所述栅极材料层进行平坦化处理,直至暴露出所述介质层的表面为止,形成栅极层,由位于所述第一区的所述栅氧化层、第一栅极功函数层、以及栅极层形成所述第一栅极结构,由所述第二区的所述栅氧化层、第一栅极功函数层、第二栅极功函数层以及栅极层形成所述第二栅极结构。由于所述隔断沟道层位于所述第二沟道层的下方,在刻蚀位于所述第一区上的所述第二栅极功函数层时,仅仅损伤包覆所述隔断沟道层的所述第二栅极功函数层,不会损伤包覆所述第二沟道层的所述第二栅极功函数层,以此降低对所述pmos晶体管阈值电压的影响,提升最终形成的半导体结构的性能。

- 还没有人留言评论。精彩留言会获得点赞!