一种具有半超结结构的快恢复二极管

本发明涉及功率半导体,尤其涉及一种具有半超结结构的快恢复二极管。

背景技术:

1、在功率半导体器件的研究中,高反向击穿电压和低正向电阻是主要的研究方向,但这两者的性能指标是相互制约,高击穿电压需要减少漂移区掺杂,但这样会使正向导通电阻增加。超结结构的提出,打破了传统硅在击穿电压和导通电阻之间的极限。在超结结构中,通过在n型外延层中加入p型掺杂,使得超结器件加反向电压时,可以在水平方向上产生电场,当n型外延层和p型区达到电荷平衡时,漂移区电荷耗尽,使得电场在漂移区内均匀分布,由此可以大幅提高击穿电压。同时,可以通过提高n型外延层和p型区的掺杂来降低器件的导通电阻。然而,在半超结快恢复二极管中,击穿电压对于p型注入区的浓度较为敏感,只有在较窄的p型注入区的浓度范围内才能实现较好的电荷平衡,较低的工艺容差增加了器件制造的工艺难度。因此,现有技术存在不足,需要改进。

技术实现思路

1、本发明主要针对半超结结构快恢复二极管中,反向击穿电压对p型注入区的浓度比较敏感的问题进行改进,提供了一种具有半超结结构的快恢复二极管。

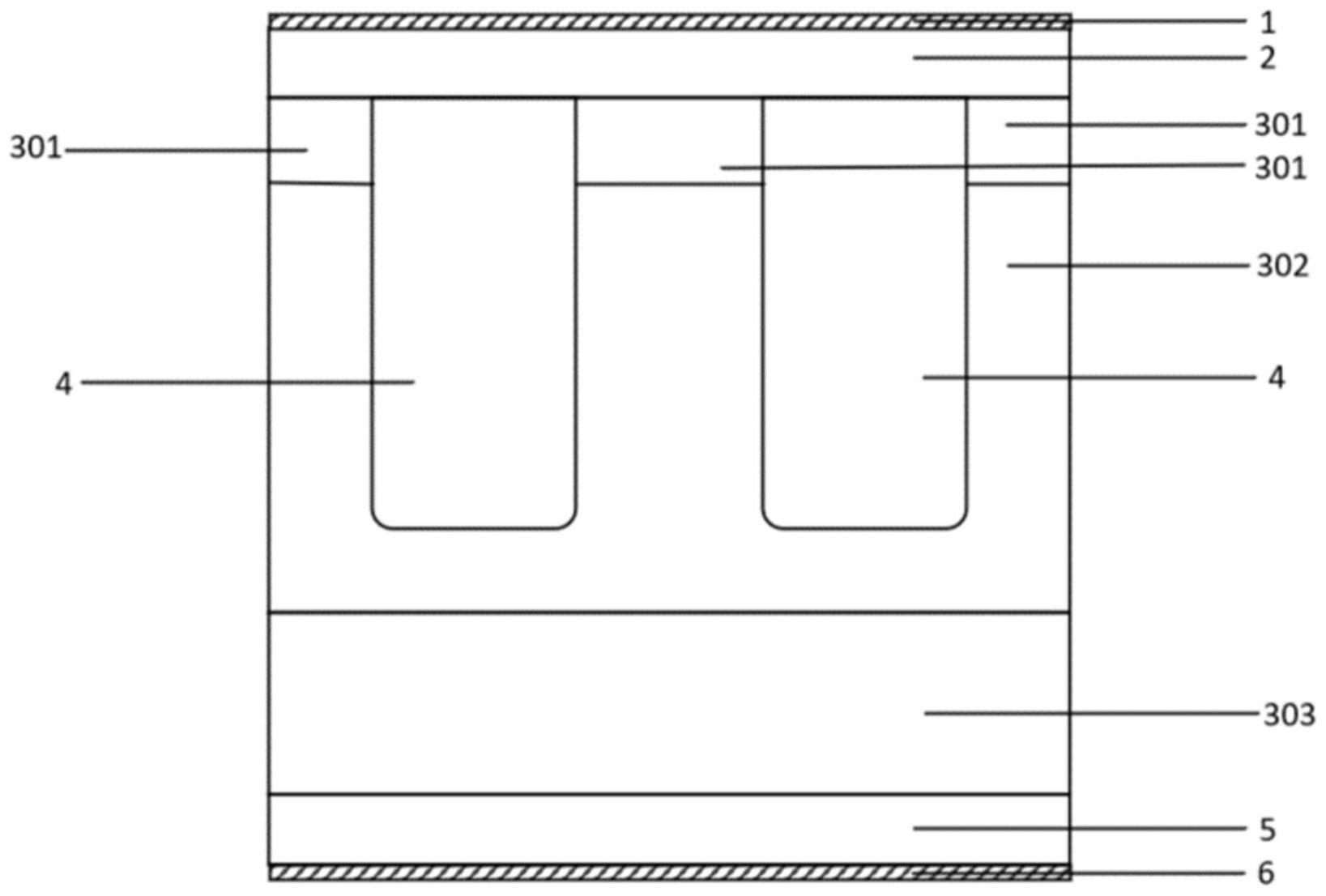

2、本发明解决技术问题的方案提供一种具有半超结结构的快恢复二极管,见附图2,该结构包括衬底层5,外延层3,p型注入区4,p型区域2,金属电极层1和6,金属电极层包括阳极金属层1与阴极金属层6,所述衬底层设置于阴极金属层6之上,所述外延层303下端与衬底层5接触,上端外延层301与p型区域2接触,所述外延层3上设置p型注入区4,p型注入区4侧面及底部与外延层302接触,顶部与p型区域2接触。所述衬底层5为n型掺杂,厚度为100~300μm,掺杂浓度为1×1018~1×1020cm-3。所述p型区域2为p型掺杂,厚度为2~10μm,掺杂浓度为1×1018~1×1020cm-3。所述p型注入区4的深度为30~60μm,宽度为5~10μm。两个相邻p型注入区4的间距为1~20μm。

3、优选地,所述外延层3分为第一外延层301,第二外延层302与第三外延层303,所述第一外延层301上端与p型区域2接触,所述第三外延层303下端与衬底层5接触,所述第二外延层302位于第一外延层301及第三外延层303之间。所述外延层3为n型掺杂,厚度为10~110μm,掺杂浓度为1×1013~5×1014cm-3,且所述第二外延层302掺杂浓度大于第一外延层301与第三外延层303的掺杂浓度。所述第一外延层301厚度为2~20μm,掺杂浓度为1×1013~5×1013cm-3,所述第二外延层302厚度为3~30μm,掺杂浓度为1×1014~5×1014cm-3,所述第三外延层303厚度为5~50μm,掺杂浓度为1×1013~5×1013cm-3。

4、相对于现有技术,本发明中具有半超结结构的快恢复二极管具有如下优点:

5、本发明为一种具有半超结结构的快恢复二极管,通过在n型外延层中加入p型注入区,当器件在加反向电压时,可以在水平方向上产生电场,当n型外延层和p型注入区达到电荷平衡时,漂移区电荷耗尽,使得电场在漂移区内均匀分布,由此可以大幅提高器件的击穿电压。同时,可以通过提高n型外延层和p型区的掺杂来降低器件的导通电阻。此外,本发明提出的结构采用三层不同掺杂浓度的外延层,可以有效提高器件在p型注入区低掺杂浓度范围和高掺杂浓度范围的击穿电压,降低了器件反向击穿电压对p型注入区掺杂浓度的敏感性,从而扩大了p型注入区的离子注入的工艺窗口,增加了工艺容差,同时增大了器件的反向击穿电压。

技术特征:

1.一种具有半超结结构的快恢复二极管,包括衬底层,外延层和属电极层;金属电极层包括阳极金属层与阴极金属层,其特征在于:还包括两个p型注入区,p型区域,所述衬底层设置于阴极金属层之上,

技术总结

一种具有半超结结构的快恢复二极管涉及功率半导体技术领域。本发明采用掺杂不同的三层外延层,从上至下分为第一外延层,第二外延层和第三外延层,所述第一外延层采用低掺杂,位于P型区域之下,所述第二外延层采用高掺杂,位于第一外延层及第三外延层之间,所述第三外延层采用低掺杂,位于衬底层之上。本发明所述的结构可以有效降低反向击穿电压对对P型注入区掺杂浓度的敏感性,从而扩大了P型注入区的工艺窗口,同时增大了器件的反向击穿电压。

技术研发人员:周新田,吴岳峰,张蕾,贾云鹏,吴郁,胡冬青,刘峰,刘洋

受保护的技术使用者:北京工业大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!