半导体装置以及功率放大器模块的制作方法

半导体装置以及功率放大器模块

1.本技术是申请日为2018年03月27日、申请号为201810261605.4、发明名称为“半导体装置以及功率放大器模块”的发明专利申请的分案申请。

技术领域

2.本发明涉及半导体装置以及功率放大器模块。

背景技术:

3.在下述的专利文献1以及专利文献2中,公开了使用异质结双极晶体管(hbt)的高频放大模块用的半导体装置。在该半导体装置设置有hbt 保护用的保护电路。保护电路在静电等的过电压被施加于hbt的情况下,防止hbt的破坏。保护电路具有将多个二极管串联连接的电路结构,被连接于hbt的集电极与发射极之间。

4.在下述的专利文献3中,公开了在布线或者有源元件上形成有电极焊盘的半导体装置。用于在接合时保护布线或者有源元件的突起电极形成于电极焊盘(接合焊盘)的表面上。突起电极在将电极焊盘的表面上的al 置换为可与ni产生置换反应的zn之后,通过在电极焊盘的表面对nip进行非电解镀而形成。记载了除了nip,也可以使用能进行非电解镀的cu 系金属。

5.在先技术文献

6.专利文献

7.专利文献1:jp特开2005-236259号公报

8.专利文献2:国际公开第2001/018865号

9.专利文献3:特开2000-164623号公报

10.在专利文献1以及专利文献2中公开的半导体装置中,必须将用于配置构成保护电路的多个二极管的区域确保在半导体基板上。因此,芯片面积变大。芯片面积的增大使得化合物半导体装置的低成本化的实现变得困难。

11.如专利文献3中公开的半导体装置那样,通过在布线或者有源元件上配置接合焊盘(bonding pad),能够抑制芯片面积的增大。在硅系半导体工艺中,对布线、接合焊盘使用了al,但在化合物半导体工艺中,通常对布线、接合焊盘不使用a1。因此,难以将专利文献3中公开的技术直接应用于化合物半导体工艺。

技术实现要素:

12.本发明的目的在于,提供一种在使用了包含化合物半导体的基板的半导体装置中,能够抑制芯片面积的增大的半导体装置。本发明的另一目的在于,提供一种使用了该半导体装置的功率放大器模块。

13.基于本发明的第1观点的半导体装置具有:

14.电路元件,形成在包含化合物半导体的基板上;和

15.接合焊盘,在所述电路元件上,被配置为与所述电路元件至少局部重叠,

16.所述接合焊盘包含第1金属膜以及形成于所述第1金属膜上的第2金属膜,所述第2金属膜的金属材料的杨氏模量比所述第1金属膜的金属材料的杨氏模量大。

17.由于电路元件与接合焊盘被配置为局部重叠,因此不需要确保用于配置接合焊盘的专用区域。由此,能够抑制芯片面积的增大。通过第2金属膜作为应力分散板而发挥作用,能够使接合时在电路元件产生的应力分散,抑制电路元件的破损。

18.基于本发明的第2观点的半导体装置除了基于第1观点的半导体装置的结构,还具有以下特征:所述接合焊盘进一步包含形成于所述第2金属膜上的第3金属膜,所述第3金属膜由与所述第1金属膜相同的金属材料形成。

19.作为第3金属膜,能够使用与接合线的接触电阻低的金属材料。与接合线直接接合于第2金属膜的情况相比,能够降低接合焊盘与接合线的接触电阻。

20.基于本发明的第3观点的半导体装置除了基于第2观点的半导体装置的结构,还具有以下特征:所述第1金属膜以及所述第3金属膜由au形成,所述第2金属膜具有包含至少1种金属材料的层,所述至少1种金属材料是从包含cu、ni以及mo的群选出的。

21.作为形成于化合物半导体基板上的多个电路元件的连接用的布线,能够使用一般被利用的au。由于cu、ni以及mo比au硬,因此第2金属膜作为应力分散板而发挥作用。

22.基于本发明的第4观点的半导体装置除了基于第3观点的半导体装置的结构,还具有以下特征:所述第2金属膜具有包含至少2种金属材料的 2层,所述至少2种金属材料是从包含cu、ni以及mo的群选出的。

23.通过将多个金属材料组合,作为第2金属膜的整体,也能够提高硬度、电阻率等选择的自由度。

24.基于本发明的第5至第7观点的半导体装置除了基于第2至第4观点的半导体装置的结构,还具有以下特征:

25.在所述第1金属膜上进一步具有保护膜,

26.所述保护膜具有在俯视情况下被配置于所述第1金属膜的内侧的开口,

27.所述第2金属膜以及所述第3金属膜在俯视情况下被配置于所述开口的内侧。

28.接合时施加于第2金属膜以及第3金属膜的载荷不被传递到保护膜。因此,接合时保护膜难以损伤。

29.基于本发明的第8至第10观点的半导体装置除了基于第5至第7观点的半导体装置的结构,进一步具有第4金属膜,所述第4金属膜覆盖所述开口的内侧的所述第1金属膜的上表面之中未被所述第2金属膜覆盖的区域、所述第2金属膜的侧面以及所述第3金属膜的侧面和上表面,并且由与所述第1金属膜相同的金属材料形成。

30.由于包含不同种类金属的第2金属膜与第3金属膜的接合界面被第4 金属膜覆盖,因此能够抑制不同种类金属接触腐蚀的产生。

31.基于本发明的第11至第13观点的半导体装置除了基于第1至第3观点的半导体装置的结构,还具有以下特征:

32.所述基板的化合物半导体具有闪锌矿型结晶构造,所述基板的上表面是从(100)面起的偏离角为4

°

以下的面,

33.所述电路元件是从包含异质结双极晶体管、场效应晶体管、二极管、电容器以及电阻元件的群选出的1个元件。

34.在将形成于具有闪锌矿型结晶构造的化合物半导体基板上的异质结双极晶体管、场效应晶体管、二极管、电容器以及电阻元件等的电路元件与接合焊盘重叠配置的结构中,能够抑制这些电路元件的损伤。

35.基于本发明的第14以及第15观点的半导体装置除了基于第11以及第12观点的半导体装置的结构,还具有以下特征:

36.所述电路元件具有包含从所述基板外延生长的半导体层的台面构造,所述台面构造的上表面的平面形状是包含与[01-1]方向平行的边和与 [011]方向平行的边的长方形或者正方形,与[011]方向平行的边比与 [01-1]方向平行的边短。

[0037]

若使用包含与[01-1]方向平行的边和与[011]方向平行的边的长方形或者正方形的蚀刻掩模,通过湿式蚀刻来对半导体层进行各向异性蚀刻,则从与[011]方向平行的边起进行侧面蚀刻,形成檐状的部分。这里,所谓“各向异性蚀刻”,是指利用了基于结晶面的蚀刻速度的不同的蚀刻。该檐状的部分通过接合时产生的应力而容易破损。由于与[011] 方向平行的边比与[01-1]方向平行的边短,因此形成檐状的部分的区域变窄。因此,能够抑制接合时的破损。

[0038]

基于本发明的第16以及第17观点的半导体装置除了基于第11以及第12观点的半导体装置的结构,还具有以下特征:所述电路元件具有包含从所述基板外延生长的半导体层的台面构造,所述台面构造的上表面的平面形状是包含与[001]方向平行的边以及与[010]方向平行的边的多边形。

[0039]

若使用包含与[001]方向平行的边和与[010]方向平行的边的多边形的蚀刻掩模,通过湿式蚀刻来对半导体层进行各向异性蚀刻,则与这些边对应地形成几乎垂直竖立的侧面。由于未形成檐状的部分,因此能够抑制接合时的破损。

[0040]

基于本发明的第18以及第19观点的半导体装置除了基于第16以及第17观点的半导体装置的结构,还具有以下特征:所述台面构造的上表面的平面形状是还包含与[01-1]方向平行的边的平行六边形。

[0041]

与平行于[01-1]方向的边对应的侧面缓慢倾斜。由于未形成檐状的部分,因此能够抑制接合时的破损。

[0042]

基于本发明的第20观点的功率放大器模块具有:

[0043]

半导体装置,所述半导体装置包含:具有形成于包含化合物半导体的基板上的异质结双极晶体管的功率放大电路、与所述异质结双极晶体管的发射极-集电极间连接的保护电路、以及作为所述功率放大电路的输出端子的接合焊盘,构成所述功率放大电路以及所述保护电路的至少1个电路元件与所述接合焊盘被配置为局部重叠,所述接合焊盘包含第1金属膜和第 2金属膜的至少2层,所述第2金属膜的金属材料的杨氏模量比所述第1 金属膜的金属材料的杨氏模量大;

[0044]

印刷布线基板,安装所述半导体装置;和

[0045]

接合线,与所述接合焊盘接合,将所述接合焊盘与所述印刷布线基板的布线连接。

[0046]

由于至少一个电路元件与接合焊盘被局部重叠地配置,因此不需要确保用于配置接合焊盘的专用区域。由此,能够抑制半导体装置的芯片面积的增大。通过第2金属膜作为应力分散板而发挥作用,能够使接合时在电路元件产生的应力分散,抑制电路元件的破损。

[0047]

由于电路元件与接合焊盘被局部重叠地配置,因此不需要确保用于配置接合焊盘

的专用区域。由此,能够抑制芯片面积的增大。通过第2金属膜作为应力分散板而发挥作用,能够使接合时在电路元件产生的应力分散,抑制电路元件的破损。

附图说明

[0048]

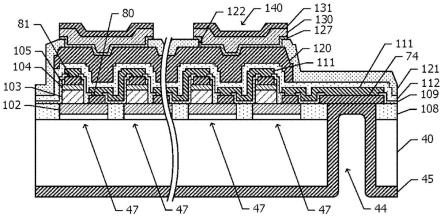

图1a是基于第1实施例的半导体装置的一部分的俯视图,图1b以及图1c分别是图1a的单点划线1b-1b以及单点划线1c-1c处的剖视图。

[0049]

图2是包含基于第1实施例的半导体装置的功率放大器模块的等效电路图。

[0050]

图3a以及图3b是基于第1实施例的半导体装置的接合焊盘的引线接合前以及引线接合中的示意性的剖视图,图3c以及图3d是基于比较例的半导体装置的接合焊盘的引线接合前以及引线接合中的示意性的剖视图。

[0051]

图4是表示各种金属的维氏硬度、杨氏模量以及电阻率的图表。

[0052]

图5是基于第2实施例的半导体装置的剖视图。

[0053]

图6是基于第3实施例的半导体装置的剖视图。

[0054]

图7a以及图7b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0055]

图8a以及图8b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0056]

图9a以及图9b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0057]

图10a以及图10b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0058]

图11a以及图11b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0059]

图12a以及图12b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0060]

图13a以及图13b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0061]

图14a以及图14b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0062]

图15a以及图15b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0063]

图16a以及图16b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0064]

图17a以及图17b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0065]

图18a以及图18b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0066]

图19a以及图19b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0067]

图20a以及图20b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0068]

图21a以及图21b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0069]

图22a以及图22b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0070]

图23a以及图23b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0071]

图24a以及图24b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0072]

图25a以及图25b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0073]

图26a以及图26b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0074]

图27a以及图27b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0075]

图28a以及图28b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0076]

图29a以及图29b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0077]

图30a以及图30b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0078]

图31a以及图31b是基于第3实施例的半导体装置的制造中途阶段的剖视图。

[0079]

图32a是基于第4实施例的半导体装置的剖视图,图32b以及图32c 分别是基于第4

实施例的变形例的半导体装置的剖视图。

[0080]

图33a是在上表面为(100)面的gaas基板通过各向异性蚀刻而形成的正八边形的台面的俯视图,图33b、图33c、图33d以及图33e分别是图33a的单点划线33b-33b、33c-33c、33d-33d以及33e-33e处的剖视图。

[0081]

图34a是基于第5实施例的半导体装置的1个二极管的俯视图,图 34b以及图34c分别是图34a的单点划线34b-34b以及单点划线34c-34c 处的剖视图。

[0082]

图35a是基于第6实施例的半导体装置的1个二极管的俯视图,图 35b以及图35c分别是图35a的单点划线35b-35b以及单点划线35c-35c 处的剖视图。

[0083]

图36a是基于第7实施例的半导体装置的1个二极管的俯视图,图 36b是图36a的单点划线36b-36b处的剖视图。

[0084]

图37是基于第8实施例的功率放大器模块的剖视图。

[0085]-符号说明-[0086]

40 基板

[0087]

41 异质结双极晶体管(hbt)

[0088]

42 保护电路

[0089]

43、44 通孔

[0090]

45 背面电极

[0091]

47 二极管

[0092]

70 集电极电极

[0093]

71 基极电极

[0094]

72 发射极电极

[0095]

73、74 通孔用连接焊盘

[0096]

80 阴极电极

[0097]

81 阳极电极

[0098]

83 檐状的部分

[0099]

101 缓冲层

[0100]

102 子集电极层

[0101]

103 集电极层

[0102]

104 基极层

[0103]

105 发射极层

[0104]

106、107 接触层

[0105]

108 元件分离区域

[0106]

109 层间绝缘膜

[0107]

110 开口

[0108]

111 布线

[0109]

112、113 层间绝缘膜

[0110]

120 接合焊盘用的第1金属膜

[0111]

121 保护膜

[0112]

122 接合焊盘用的开口

[0113]

127 镀覆用的种子电极层

[0114]

130 接合焊盘用的第2金属膜

[0115]

130a 下侧金属膜

[0116]

130b 上侧金属膜

[0117]

131 接合焊盘用的第3金属膜

[0118]

132 接合焊盘用的第4金属膜

[0119]

140 接合焊盘

[0120]

143 基于比较例的半导体装置的接合焊盘

[0121]

150 发射极区域

[0122]

160 抗蚀剂膜

[0123]

161 开口

[0124]

163 抗蚀剂膜

[0125]

164 开口

[0126]

166 蜡

[0127]

167 蓝宝石基板

[0128]

170 抗蚀剂膜

[0129]

171、172 开口

[0130]

200 印刷布线基板

[0131]

201、202 下垫板

[0132]

203、204 接合焊盘

[0133]

221 导电性粘接剂

[0134]

225 接合线

[0135]

230 硅半导体芯片

[0136]

231 导电性粘接剂

[0137]

232 接合焊盘

[0138]

235 接合线

[0139]

240 密封用固化树脂

[0140]

500 半导体装置

[0141]

501 信号输入用的接合焊盘

[0142]

502 初级的hbt

[0143]

503、504 偏置电路

[0144]

505 接合线

[0145]

506 金属球

[0146]

510 毛细管

[0147]

511 表示向第3金属膜施加的应力的分布的曲线

[0148]

512 表示向保护电路施加的应力的分布的曲线

[0149]

520 输入匹配电路

[0150]

521 输入端子

[0151]

522 信号输出用的接合焊盘

[0152]

523 接合线

[0153]

540 输出匹配电路

[0154]

541 信号输入用的接合焊盘

[0155]

542 输出端子。

具体实施方式

[0156]

[第1实施例]

[0157]

参照图1a至图4的附图,对基于第1实施例的半导体装置进行说明。图1a是基于第1实施例的半导体装置的一部分的俯视图。在包含半绝缘性的gaas的基板40上,形成异质结双极晶体管(hbt)41、保护电路 42等的电路元件。多个接合焊盘140被配置为与构成保护电路42的电路元件局部重叠。

[0158]

图1b是图1a的单点划线1b-1b处的剖视图。在基板40上依次层叠缓冲层101、子集电极层102、集电极层103、基极层104、发射极层105、接触层106、107。缓冲层101由非掺杂的gaas形成,子集电极层102以及集电极层103由n型的gaas形成。基极层104由p型的gaas形成。发射极层105由n型的ingap形成。接触层106、107分别由n型的gaas 以及n型的ingaas形成。

[0159]

通过向缓冲层101以及子集电极层102的一部分的区域注入硼(b),来形成元件分离区域108。包含子集电极层102、集电极层103、基极层 104以及发射极层105的hbt41形成在基板40上。在子集电极层102上形成集电极电极70,集电极电极70与子集电极层102欧姆连接。形成在发射极层105上的基极电极71贯通发射极层105并与基极层104欧姆连接。形成在接触层107上的发射极电极72与接触层107欧姆连接。

[0160]

在hbt41的侧向的元件分离区域108上,形成通孔用连接焊盘73。在基板40的整个区域形成层间绝缘膜109,以使得覆盖hbt41、通孔用连接焊盘73。对层间绝缘膜109例如使用氮化硅(sin)。在层间绝缘膜 109的规定的位置、例如配置有集电极电极70、基极电极71、发射极电极 72、通孔用连接焊盘73的位置形成多个接触孔。

[0161]

形成在层间绝缘膜109上的布线111将发射极电极72和通孔用连接焊盘73连接。进一步地,其他多个布线111连接于集电极电极70、基极电极71。

[0162]

在基板40的整个区域形成层间绝缘膜112以使得覆盖布线111,在其上方进一步形成上侧的层间绝缘膜113。对层间绝缘膜112例如使用sin,对上侧的层间绝缘膜113使用聚酰亚胺。在层间绝缘膜113上形成保护膜 121。对保护膜121例如使用sin。

[0163]

从基板40的背面向通孔用连接焊盘73形成通孔43。形成于基板40 的背面的背面电极45通过通孔43内而与通孔用连接焊盘73连接。

[0164]

图1c是图1a的单点划线1c-1c处的剖视图。在基板40上,形成利用了集电极层103与基极层104的pn结的多个二极管47。通过将多个二极管47串联连接来构成保护电路42(图1a)。

[0165]

形成于二极管47的各自的子集电极层102上的阴极电极80与子集电极层102欧姆连接。形成于二极管47的各自的发射极层105上的阳极电极81贯通发射极层105而与基极层104欧姆连接。在1个二极管47的侧向的元件分离区域108上形成通孔用连接焊盘74。

[0166]

在基板40的整个区域形成层间绝缘膜109,以使得覆盖二极管47以及通孔用连接

焊盘74。在层间绝缘膜109的规定的位置、例如配置有阴极电极80、阳极电极81、通孔用连接焊盘74的位置,形成接触孔。通过形成于层间绝缘膜109上的多个布线111将多个二极管47的阴极电极80和阳极电极81连接,从而将多个二极管47串联连接。其他布线111将包含多个二极管47的串联电路的端部的阴极电极80和通孔用连接焊盘74连接。包含多个二极管47的串联电路的端部的阳极电极81通过其他布线111 而与hbt41(图1b)的集电极电极70连接。

[0167]

在基板40的整个区域形成层间绝缘膜112以使得覆盖布线111。在层间绝缘膜112上形成接合焊盘用的第1金属膜120。第1金属膜120被配置于与多个二极管47部分重叠的位置。

[0168]

在第1金属膜120以及层间绝缘膜112上形成保护膜121。在保护膜 121形成接合用的多个开口122。该多个开口122被配置于俯视情况下第1 金属膜120的内侧、并且与多个二极管47部分重叠的位置。

[0169]

形成镀覆用的种子电极层127以使得覆盖开口122的底面以及侧面。种子电极层127扩展到保护膜121的上表面的包围开口122的边框状的区域。在种子电极层127上依次层叠接合焊盘用的第2金属膜130以及第3 金属膜131。由第1金属膜120、第2金属膜130以及第3金属膜131构成接合焊盘140。

[0170]

第2金属膜130的金属材料比第1金属膜120的金属材料硬。金属材料的硬度例如能够由维氏硬度、杨氏模量等定义。第3金属膜131由与第 1金属膜120相同的金属材料形成。例如,第1金属膜120以及第3金属膜131由金(au)形成,第2金属膜130由铜(cu)形成。

[0171]

形成从基板40的背面达到至通孔用连接焊盘74的通孔44。形成于基板40的背面的背面电极45通过通孔44内而与通孔用连接焊盘74连接。

[0172]

图2是包含基于第1实施例的半导体装置的功率放大器模块的等效电路图。该功率放大器模块包含:输入匹配电路520、半导体装置500以及输出匹配电路540。

[0173]

半导体装置500包含构成功率放大电路的初级的hbt502以及输出级的hbt41。输入信号被输入到信号输入用的接合焊盘501。输入信号被输入到初级的hbt502的基极电极。初级的hbt502的输出被输入到输出级的hbt41的基极电极71(图1b)。

[0174]

偏置电路503、504分别向初级的hbt502以及输出级的hbt41提供偏置电流。在输出级的hbt41的集电极-发射极之间连接保护电路42。保护电路42包含串联连接的多个、例如10个二极管47。输出级的hbt41 的集电极与作为输出端子的多个接合焊盘140连接。

[0175]

向输入匹配电路520的输入端子521输入高频信号。输入匹配电路520 的信号输出用的接合焊盘522通过接合线523而与半导体装置500的信号输入用的接合焊盘501连接。

[0176]

半导体装置500的信号输出用的多个接合焊盘140分别通过多个接合线505而与输出匹配电路540的信号输入用的多个接合焊盘541连接。被输入到输入匹配电路520的输入端子521的高频信号经由输入匹配电路 520,被半导体装置500放大,经由输出匹配电路540而被输出到输出端子542。

[0177]

[第1实施例的效果]

[0178]

接下来,对第1实施例的优良效果进行说明。

[0179]

在第1实施例中,保护电路42(图1a)具有保护hbt41(图1b) 使其免于静电破坏、过电压破坏、负载变动破坏的功能。此外,在第1实施例中,由于该保护电路42(图1a)与接合焊盘140被部分重叠地配置,因此不需要确保用于配置接合焊盘140的专用的区域。由此,能够

抑制芯片面积的增大。

[0180]

接下来,参照从图3a至图3d的附图,对第1实施例的其他效果进行说明。图3a以及图3b是基于第1实施例的半导体装置的接合焊盘140 的引线接合前以及引线接合中的示意性的剖视图。

[0181]

在毛细管510支承接合线505。作为接合线505,例如使用金(au) 线。在接合线505的前端形成金属球506。若将毛细管510向接合焊盘140 按压并施加热量或者超声波,则接合焊盘140的第3金属膜131以及金属球506变形并且两者接合。在第3金属膜131,沿着金属球506的外周产生相对较大的应力。通过曲线511来表示向第3金属膜131施加的应力的分布。

[0182]

在第3金属膜131产生的应力经由相对较硬的第2金属膜130而被传递到保护电路42。通过第2金属膜130作为应力分散板而发挥作用,从而在比第2金属膜130更靠下方的保护电路42产生的应力的分布变得比在第3金属膜131产生的应力的分布平缓。通过曲线512来表示在保护电路 42产生的应力的分布。

[0183]

图3c以及图3d是基于比较例的半导体装置的接合焊盘143的引线接合前以及引线接合中的示意性的剖视图。在比较例中,接合焊盘143由包含与第1金属膜120以及第3金属膜131(图3a、图3b)相同的金属材料的单一的金属膜形成。由于接合焊盘143比第2金属膜130(图3a、图3b)柔软,因此使应力分散的功能较弱。因此,如曲线512所示,沿着金属球506的外周,在保护电路42产生较大的应力。在产生较大的应力的位置,在构成保护电路42的电路元件容易产生损伤。

[0184]

在第1实施例中,由于接合焊盘140的第2金属膜130作为应力分散板而发挥作用,因此在接合时,在保护电路42难以产生损伤。进一步地,由于作为第3金属膜131,使用比第2金属膜130柔软的金属材料,因此能够确保接合线505与接合焊盘140的良好的电连接。

[0185]

从得到稳定的接触界面的观点出发,优选对第1金属膜120使用与其方的布线111(图1b、图1c)相同的金属材料。在由化合物半导体形成电路元件的情况下,一般对布线111使用au。因此,优选对第1金属膜 120使用au。

[0186]

接下来,参照图4,说明对于接合焊盘140的第2金属膜130优选的金属材料。第2金属膜130为了提高作为应力分散板的效果,优选使用比第1金属膜120硬的金属材料。这里,所谓“硬”,是指维氏硬度高、或者杨氏模量大。进一步地,从第2金属膜130构成接合焊盘140的一部分的观点出发,优选使用电阻率较低的金属材料。

[0187]

图4是表示各种金属的维氏硬度、杨氏模量以及电阻率的图表。图4 所示出的维氏硬度是在全部金属中以相同的试验力测定得出的值。

[0188]

在对第1金属膜120使用au的情况下,优选对第2金属膜130使用维氏硬度或者杨氏模量比金(au)高的金属材料。作为一个例子,优选对第2金属膜130使用具有比30hv高的维氏硬度的金属材料或者具有比 90gpa大的杨氏模量的金属材料。作为维氏硬度或者杨氏模量比au高并且电阻率并不明显高的金属材料,举例:铜(cu)、镍(ni)、钼(mo)。优选对第2金属膜130使用cu、ni或者mo。

[0189]

在接合焊盘140对于使应力分散而足够厚的情况下,插入较硬的第2 金属膜130(图1c)的效果较低。在接合焊盘140的厚度为10μm以下的情况下,可得到插入第2金属膜130的显著的效果。

[0190]

[第1实施例的变形例]

[0191]

在第1实施例中,接合焊盘140(图1a)与构成保护电路42的二极管47(图1c)局部重叠。此外,也可以设为接合焊盘140与hbt41(图 1a、图lb)重叠的构成。在基板40(图1b、图1c)上,如图2所示那样形成电容器、电阻元件等的电路元件。也可以设为将接合焊盘140与这些电路元件局部重叠的构成。也可能在包含化合物半导体的基板40上,形成hbt以外的有源元件、例如高电子迁移率晶体管(hemt)、mes 型场效应晶体管(mesfet)等的场效应晶体管。也可以设为将接合焊盘 140与使用了化合物半导体的这些有源元件局部重叠的构成。

[0192]

在图1a中,表示了接合焊盘140的个数是3个的例子,但接合焊盘 140的个数并不局限于3个。配置1个以上的接合焊盘140即可。在图2 中,表示了输出级的hbt41是1个的例子,但一般由并联连接的多个hbt 构成输出级。

[0193]

也可以在包含cu的第2金属膜130(图1c)与包含au的第3金属膜131(图1c)的界面,配置扩散防止膜。作为扩散防止膜,能够使用 tiw、ni等。

[0194]

在第1实施例中,作为基板40,使用了gaas基板,但也可以使用其他的化合物半导体基板。例如,也可以作为基板40,使用inp基板。

[0195]

在第1实施例中,作为一个例子,将第1金属膜120与第2金属膜130 设为相同的厚度,但优选使第2金属膜130的厚度为第1金属膜120的厚度以上。通过使第2金属膜130较厚,能够提高第2金属膜130的作为应力分散板的功能。

[0196]

[第2实施例]

[0197]

接下来,参照图5,对基于第2实施例的半导体装置进行说明。以下,针对与基于第1实施例的半导体装置的构成共通的构成,省略说明。

[0198]

图5是基于第2实施例的半导体装置的剖视图。在第1实施例中,如图1c所示,接合焊盘140的第2金属膜130以及第3金属膜131扩展到开口122的边缘的外侧,其外周部分与保护膜121重叠。与此相对地,在第2实施例中,第2金属膜130以及第3金属膜131在俯视情况下被配置于开口122的内侧。即,第2金属膜130以及第3金属膜131与保护膜121 不重叠。另外,种子电极层127也在俯视情况下被配置于开口122的内侧。

[0199]

在第2实施例中,即使在接合时向接合焊盘140的第2金属膜130以及第3金属膜131施加载荷,也不向保护膜121施加载荷。因此,能够减少接合时向保护膜121施加的机械应力。其结果,能够抑制向保护膜121 的裂缝的产生。

[0200]

[第3实施例]

[0201]

接下来,参照图6,对基于第3实施例的半导体装置进行说明。以下,针对与基于第2实施例的半导体装置的构成共通的构成,省略说明。

[0202]

图6是基于第3实施例的半导体装置的剖视图。在第2实施例中,是包含接合焊盘140的种子电极层127、第2金属膜130以及第3金属膜131 (图5)的多层构造的侧面以及上表面露出的状态。在第3实施例中,包含种子电极层127、第2金属膜130以及第3金属膜131的多层构造的侧面以及上表面被第4金属膜132覆盖。第4金属膜132进一步覆盖开口122 内的第1金属膜120的上表面之中未形成种子电极层127的区域。对第4 金属膜132例如使用与第3金属膜131相同的金属材料。

[0203]

在第3实施例中,第2金属膜130与第3金属膜131的不同种类金属的接触面不露出。因此,特别是能够抑制高湿度环境下的不同种类金属接触腐蚀。

[0204]

接下来,参照图7a、图7b至图30a、图30b的附图,对基于第3 实施例的半导体装置的制造方法进行说明。基于第3实施例的半导体装置的制造方法也能够应用于基于第1实施例以及第2实施例的半导体装置的制造。

[0205]

图7a、图7b至图30a、图30b的附图是基于第3实施例的半导体装置的制造中途阶段的剖视图。图7a、图7b至图30a、图30b的附图之中,在末尾附上a的附图对应于图1a的单点划线1b-1b处的剖视图,在末尾附上b的附图对应于图1a的单点划线1c-1c处的剖视图。

[0206]

如图7a以及图7b所示,在包含半绝缘性的gaas的基板40上,使缓冲层101、子集电极层102、集电极层103、基极层104、发射极层105、接触层106、107依次外延生长。对这些半导体层的形成,例如能够使用有机金属气相外延(movpe)法。基板40的上表面是从(100)面起的偏离角为4

°

以下的面。

[0207]

接下来,对从缓冲层101到接触层107的各半导体层的材料、掺杂浓度以及膜厚的一个例子进行说明。缓冲层101由非掺杂的gaas形成,其膜厚为0.1μm。子集电极层102由n型gaas形成,作为n型掺杂剂的si 的掺杂浓度为5

×

10

18

cm-3

,膜厚为0.6μm。集电极层103由n型gaas形成, si的掺杂浓度为1

×

10

16

cm-3

,膜厚为1.0μm。基极层104由p型gaas形成,作为p型掺杂剂的c的掺杂浓度为5

×

10

19

cm-3

,膜厚为96nm。发射极层105由n型ingap形成,inp的摩尔比为0.48,si的掺杂浓度为 4

×

10

17

cm-3

,膜厚为35nm。接触层106由n型gaas形成,si的掺杂浓度为5

×

10

18

cm-3

,膜厚为50nm。上侧的接触层107由n型ingaas形成,inas 的摩尔比为0.5,si的掺杂浓度为1

×

10

19

cm-3

,膜厚为50nm。

[0208]

如图8a所示,在接触层107的规定的区域上形成发射极电极72。在图8b所示的剖面,未配置发射极电极72。发射极电极72具有从基板40 侧起依次层叠厚度10nm的mo膜、厚度5nm的ti膜、厚度30nm的pt 膜以及厚度200nm的au膜的4层构造。发射极电极72能够通过蒸镀以及剥离法来形成。

[0209]

如图9a所示,通过将接触层107、106加工为规定的形状,形成发射极区域150。在发射极区域150上配置发射极电极72。在图9b所示的剖面,接触层107、106被除去,发射极层105露出。接触层107、106的加工中,能够应用光刻以及湿式蚀刻。对该湿式蚀刻,例如能够使用将磷酸、双氧水以及水混合而成的蚀刻液。作为一个例子,能够使用将浓度85重量%的磷酸、浓度35重量%的双氧水和水以体积比1:2:40的比例进行混合而成的蚀刻液。该蚀刻液具有不实质地蚀刻包含ingap的发射极层 105而选择性地蚀刻包含gaas的接触层107、106的选择性。

[0210]

如图10a所示,在发射极区域150的两侧形成基极电极71。基极电极71在应用光刻、蒸镀以及剥离法在发射极层105上形成金属膜之后,通过进行烧结,贯通发射极层105并与基极层104欧姆连接。用于形成基极电极71的金属膜包含从基板40侧起依次被层叠的厚度30nm的pt膜、厚度50nm的ti膜、厚度50nm的pt膜以及厚度200nm的au膜。

[0211]

如图10b所示,与基极电极71(图10a)的形成同时地,形成多个阳极电极81。阳极电极81也贯通发射极层105并与基极层104欧姆连接。

[0212]

如图11a以及图11b所示,通过光刻以及湿式蚀刻来除去发射极层 105的不必要的部分。由此,基极层104露出。作为蚀刻液,例如能够使用盐酸。盐酸具有不实质地蚀刻包含gaas的基极层104而选择性地蚀刻包含ingap的发射极层105的选择性。

[0213]

如图12a以及图12b所示,使用对发射极层105进行蚀刻时的蚀刻掩模,除去基极层

104以及集电极层103的不必要的部分。由此,子集电极层102露出。对基极层104以及集电极层103的蚀刻,能够使用与对接触层107、106(图9a、图9b)的蚀刻使用的蚀刻液相同的蚀刻液。蚀刻的停止通过进行时间控制来进行。

[0214]

如图13a以及图13b所示,形成用于确保元件间的电绝缘的元件分离区域108。元件分离区域108例如能够通过向子集电极层102以及缓冲层101离子注入硼而形成。

[0215]

如图14a以及图14b所示,与在hbt41(图1b)的子集电极层102 上形成集电极电极70同时地,在二极管47(图1b)的子集电极层102上形成阴极电极80。进一步地,在元件分离区域108上形成通孔用连接焊盘 73、74。对集电极电极70、阴极电极80以及通孔用连接焊盘73、74的形成能够应用光刻、蒸镀以及剥离法。集电极电极70、阴极电极80以及通孔用连接焊盘73、74包含从基板40侧起依次被层叠的厚度60nm的auge 膜、厚度10nm的ni膜以及厚度200nm的au膜。

[0216]

如图15a以及图15b所示,使层间绝缘膜109堆积于基板40的整个区域,以使得覆盖hbt41、二极管47、通孔用连接焊盘73、74。层间绝缘膜109例如由sin形成,厚度为100nm。对于层间绝缘膜109的堆积,例如能够应用化学气相生长(cvd)法。

[0217]

如图16a以及图16b所示,在层间绝缘膜109的规定的位置形成多个开口110。多个开口110分别在俯视情况下被配置于集电极电极70、基极电极71、发射极电极72、阴极电极80、阳极电极81以及通孔用连接焊盘73、74的内侧,使这些部分的上表面的一部分的区域露出。对于开口 110的形成,能够应用光刻以及干式蚀刻。

[0218]

如图17a以及图17b所示,在层间绝缘膜109上形成多个布线111。布线111例如由au形成,其厚度为1μm。对于布线111的形成,能够应用光刻、蒸镀以及剥离法。一个布线111将发射极电极72与通孔用连接焊盘73连接。另一个布线将1个二极管47的阴极电极80与通孔用连接焊盘74连接。另一个布线111将二极管47的阳极电极81与和其相邻的二极管47的阴极电极80连接。进一步地,在基极电极71以及集电极电极70也分别连接布线111。

[0219]

如图18a所示,在基板40的整个区域形成层间绝缘膜112,以使得覆盖布线111。层间绝缘膜112例如由sin形成。进一步地,在层间绝缘膜112上形成层间绝缘膜113。层间绝缘膜113例如通过涂敷聚酰亚胺并形成厚度1.8μm的聚酰亚胺膜后,进行表面的平坦化而形成。然后,除去配置接合焊盘140(图1a、图6)的区域的层间绝缘膜113。在图18b所示的剖面,层间绝缘膜113被除去,包含sin的层间绝缘膜112露出。

[0220]

如图19b所示,在层间绝缘膜112上形成第1金属膜120。第1金属膜120配置为与多个二极管47局部重叠。在图19a所示的剖面内,不形成第1金属膜120。第1金属膜120例如由au形成,其厚度为2μm。对于第1金属膜120的形成,例如能够应用光刻、蒸镀以及剥离法。与第1 金属膜120的形成同时地,在基板40的其他区域形成第2层的布线。

[0221]

在基板40的整个区域形成包含sin的保护膜121,以使得覆盖图19b 所示的第1金属膜120。在图19a所示的剖面,在层间绝缘膜113上形成保护膜121。保护膜121的厚度例如为500nm。对于保护膜121的形成,例如能够应用cvd法。

[0222]

在保护膜121上形成抗蚀剂膜160,在应形成接合焊盘140(图1a、图6)的区域形成开口161。

[0223]

如图20a以及图20b所示,通过将抗蚀剂膜160作为蚀刻掩模来对保护膜121进行蚀刻,从而在保护膜121形成开口122。第1金属膜120 在开口122的内侧露出。对于保护膜121

的蚀刻,例如能够应用干式蚀刻。在保护膜121形成开口122后,除去抗蚀剂膜160。

[0224]

如图21a以及图21b所示,在基板40的整个区域形成镀覆用的种子电极层127,以使得覆盖保护膜121的上表面、开口122的侧面以及底面。种子电极层127例如包含厚度0.1μm的tiw膜和厚度0.1μm的cu膜的2 层。对于种子电极层127的形成,例如能够应用溅射法。

[0225]

如图22a以及图22b所示,在种子电极层127上形成抗蚀剂膜163。通过光刻,在应形成第2金属膜130以及第3金属膜131(图6)的区域形成开口164。在开口164内,种子电极层127露出。

[0226]

如图23a以及图23b所示,在开口164内的种子电极层127上,通过电解镀来使第2金属膜130以及第3金属膜131依次堆积。第2金属膜 130例如由cu形成,其厚度为2μm。第3金属膜131例如由au形成,其厚度为1μm。第3金属膜131的上表面比抗蚀剂膜163的上表面低。在形成第2金属膜130以及第3金属膜131之后,除去抗蚀剂膜163。

[0227]

如图24a以及图24b所示,对未形成第2金属膜130的区域的露出的种子电极层127进行蚀刻除去。保护膜121在图24a的剖面露出,在图 24b的剖面,第1金属膜120在保护膜121以及形成于保护膜121的开口 122内露出。

[0228]

如图25b所示,在包含种子电极层127、第2金属膜130以及第3金属膜131的层叠构造的侧面和上表面、以及在开口122内露出的第1金属膜120的上表面,形成第4金属膜132。对于第4金属膜132的形成,例如能够应用非电解镀。第4金属膜132例如由au形成,其厚度为0.1μm。在图25a以及图25b所示的保护膜121的上表面不堆积au。

[0229]

如图26a以及图26b所示,使基板40的表侧的面(形成有保护膜121 的面)与蓝宝石基板167对置,隔着蜡166而将基板40与蓝宝石基板167 粘贴。

[0230]

如图27a以及图27b所示,通过从背侧对基板40进行研削,使其薄层化到厚度75μm。

[0231]

如图28a以及图28b所示,在被薄层化的基板40的背侧的表面形成抗蚀剂膜170。通过光刻,在抗蚀剂膜170形成开口171、172。开口171、 172分别形成于与通孔用连接焊盘73、74对应的位置。

[0232]

如图29a以及图29b所示,将抗蚀剂膜170作为蚀刻掩模,对基板 40以及元件分离区域108进行蚀刻。由此,形成贯通基板40以及元件分离区域108的通孔43、44,在其底面,分别露出通孔用连接焊盘73、74。对于基板40以及元件分离区域108的蚀刻,能够应用各向异性干式蚀刻。在通孔用连接焊盘73、74露出后,除去抗蚀剂膜170。

[0233]

如图30a以及图30b所示,在基板40的被侧的表面以及通孔43、44 的侧面以及底面形成背面电极45。背面电极45能够通过利用非电解镀来使钯堆积之后,利用电解镀来使au堆积而形成。背面电极45的厚度为 4μm。在形成背面电极45之后,从基板40取下蜡166以及蓝宝石基板167。

[0234]

如图31a以及图31b所示,接合焊盘140的表层的第4金属膜132 以及保护膜121露出。然后,通过进行切割等来按照每个芯片进行分离,从而半导体装置完成。

[0235]

[第4实施例]

[0236]

接下来,参照图32a,对基于第4实施例的半导体装置进行说明。以下,针对与参照图1a至图4的附图而说明的第1实施例共通的构成,省略说明。

[0237]

图32a是基于第4实施例的半导体装置的剖视图。在第1实施例中,构成接合焊盘140的第2金属膜130(图1c)由包含比第1金属膜120硬的金属材料的单层构成。在第4实施例

中,第2金属膜130具有包含不同的金属材料的下侧金属膜130a以及上侧金属膜130b的2层构造。下侧金属膜130a以及上侧金属膜130b均由比第1金属膜120硬的金属材料形成。

[0238]

例如,作为下侧金属膜130a以及上侧金属膜130b,优选使用从cu、 ni、mo这3种金属选出的2种金属。

[0239]

接下来,参照图32b以及图32c,对基于第4实施例的变形例的半导体装置进行说明。

[0240]

图32b以及图32c分别是基于第4实施例的变形例的半导体装置的剖视图。在图32b所示的变形例中,与基于第2实施例的半导体装置的接合焊盘140(图5)同样地,第2金属膜130以及第3金属膜131被配置于在保护膜121设置的开口122的内侧。在图32c所示的变形例中,与基于第3实施例的半导体装置的接合焊盘140(图6)同样地,包含第2金属膜130以及第3金属膜131的层叠构造、以及该层叠构造的周围的第1金属膜120的上表面被第4金属膜132覆盖。在图32b以及图32c所示的变形例中,第2金属膜130也包含下侧金属膜130a和上侧金属膜130b这2 层。

[0241]

在第4实施例以及第4实施例的变形例中,能够将第2金属膜130作为整体来设为所希望的硬度,并且将多个材料组合以使得抑制电阻率的增加。其结果,可提供一种可靠性更高的半导体装置。

[0242]

[第5实施例]

[0243]

接下来,参照图33a至图34c的附图,对基于第5实施例的半导体装置进行说明。以下,针对与第1实施例至第4实施例的各实施例共通的构成,省略说明。在第1实施例至第4实施例的各实施例中,未限定基板 40(图1b、图1c等)的上表面的面指数、二极管47(图1c等)的各半导体层的图案的平面形状以及取向。在第5实施例中,基板40的上表面的面指数被确定,半导体层的图案的平面形状以及优选的取向被限定。

[0244]

首先,参照图33a至图33e的附图,对基于湿式蚀刻的各向异性蚀刻特性进行说明。

[0245]

图33a是在上表面为(100)面的gaas基板通过各向异性蚀刻而形成的正八边形的台面的俯视图。正八边形的1个边与[011]方向平行。图33b、图33c、图33d以及图33e分别是图33a的单点划线33b-33b、单点划线33c-33c、单点划线33d-33d以及单点划线33e-33e处的剖视图。作为进行各向异性蚀刻的蚀刻液,能够使用弱酸性或者弱碱性的蚀刻液。

[0246]

在图33b所示的剖面,在朝向[01-1]方向的侧面以及朝向其相反方向的侧面容易形成出现了(111)a面的反台面状的部分。例如,台面构造的上层部分为反台面状,下层部分为正台面状。在反台面状的部分,形成在横向突出的檐状的部分。这里,对米勒指数的各要素付与的负号表示对该要素付与了上横线。在图33c所示的剖面,在朝向[0-1-1]方向的侧面以及朝向其相反方向的侧面容易出现(111)b面,侧面为平缓的斜面。在图33d以及图33e所示的剖面,朝向[00-1]方向的侧面以及朝向其相反方向的侧面、朝向[0-10]方向的侧面以及朝向其相反方向的侧面为几乎垂直竖立的形状。

[0247]

图33b至图33e的各图中所示的各向异性蚀刻特性与对在上表面为 (100)面的gaas基板上外延生长的化合物半导体进行各向异性蚀刻时的特性相同。此外,除了gaas基板,对在具有闪锌矿型结晶构造的化合物半导体基板以及其上外延生长的化合物半导体层进行各向异性蚀刻的情况下,也可得到相同的特性。

[0248]

图34a是基于第5实施例的半导体装置的1个二极管47的俯视图。图34b以及图34c

分别是图34a的单点划线34b-34b以及单点划线 34c-34c处的剖视图。基板40的上表面的面指数为(100)。另外,也可以使用上表面是从(100)面起的偏离角为4

°

以下的结晶面的基板。

[0249]

在由元件分离区域108包围的子集电极层102上,层叠集电极层103、基极层104以及发射极层105。俯视情况下,发射极层105被配置于集电极层103的内侧。形成于子集电极层102上的阴极电极80将集电极层103 从[011]方向、[0-11]方向以及[0-1-1]方向这三个方向包围。形成于发射极层105上的阳极电极81贯通发射极层105并与基极层104欧姆连接。

[0250]

多个二极管47(图1c)与[01-1]方向平行地排列。该排列方向相当于包含gaas的基板40的容易裂开方向。换言之,多个二极管47在与容易裂开方向平行的方向上排列。

[0251]

发射极层105、基极层104以及集电极层103通过使用相同的蚀刻掩模来进行各向异性蚀刻而被图案化(参照图11b以及图12b)。该蚀刻掩模的平面形状是长方形,长边与[01-1]方向平行,短边与[011]方向平行。

[0252]

如图34b所示,在相对于[0-1-1]方向垂直的剖面,包含集电极层 103、基极层104以及发射极层105的台面的上层部分为反台面状,形成檐状的部分83。图34a所示的发射极层105相当于上表面的外周线。

[0253]

如图34c所示,在相对于[0-11]方向垂直的剖面,包含集电极层103、基极层104以及发射极层105的台面为正台面状,形成平缓的斜面。图34a 所示的集电极层103表示底面的外周线。

[0254]

接下来,对第5实施例的优良效果进行说明。若在接合时对二极管47 施加载荷,则在檐状的部分83容易产生破损。在第5实施例中,发射极层105的外周线(图34a)之中,与形成檐状的部分83的[011]方向平行的边比与形成平缓的斜面的[01-1]方向平行的边短。这样,形成檐状的部分83的区域被限定于较窄的范围。因此,难以产生基于接合时的载荷的破损。

[0255]

在图34a至图34c的附图中,表示了阳极电极81贯通发射极层105 并与基极层104欧姆连接的例子,但也可以除去发射极层105而将阳极电极81直接形成于基极层104上。在该情况下,由基极层104和集电极层 103的上层部分形成檐状的部分83。

[0256]

为了提高抑制檐状的部分83的破损的效果,优选使配置有阳极电极 81的台面状部分的上表面的短边的长度为长边的长度的1/2以下。

[0257]

[第6实施例]

[0258]

接下来,参照图35a至图35c的附图,对基于第6实施例的半导体装置进行说明。以下,针对与基于第5实施例的半导体装置共通的构成,省略说明。

[0259]

图35a是基于第6实施例的半导体装置的1个二极管47的俯视图。图35b以及图35c分别是图35a的单点划线35b-35b以及单点划线 35c-35c处的剖视图。在第5实施例中,发射极层105以及集电极层103 (图34a)的平面形状为长方形。在第6实施例中,发射极层105以及集电极层103的平面形状为包含与[01-1]方向平行的边、与[001]方向平行的边以及与[010]方向平行的边的多边形,例如平行六边形。

[0260]

如图35b所示,在相对于与[01-1]方向平行的边垂直交叉的剖面,包含集电极层103、基极层104以及发射极层105的台面的形状与图34c 所示的第5实施例的剖面同样地,为正台面状。如图35a所示,集电极层 103的底面比发射极层105的底面更向[011]方向以及[0-1-1]方向扩展。

[0261]

如图35c所示,在与平行于[010]方向的边交叉的剖面,包含集电极层103、基极层104以及发射极层105的台面的侧面为垂直竖立的形状。在与平行于[001]方向的边交叉的剖面也相同。

[0262]

在第6实施例中,在包含二极管47的集电极层103、基极层104以及发射极层105的台面不形成檐状的部分。因此,可得到难以产生基于接合时的载荷的破损的效果。

[0263]

[第7实施例]

[0264]

接下来,参照图36a以及图36b,对基于第7实施例的半导体装置进行说明。以下,针对与基于第6实施例的半导体装置共通的构成,省略说明。

[0265]

图36a是基于第7实施例的半导体装置的1个二极管47的俯视图。在第6实施例中,发射极层105的平面形状为平行六边形(图35a),但在第7实施例中,是具有与[010]方向平行的边以及与[001]方向平行的边的正方形。

[0266]

图36b是图36a的单点划线36b-36b中的剖视图。在与平行于[010] 方向的边交叉的剖面,包含集电极层103、基极层104以及发射极层105 的台面的侧面为垂直竖直的形状。在与平行于[001]方向的边交叉的剖面也相同。

[0267]

如上述那样,在第7实施例中,包含集电极层103、基极层104以及发射极层105的台面的全部侧面为垂直竖直的形状,不形成檐状的部分。由此,可得到难以产生基于接合时的载荷的破损的效果。

[0268]

[第8实施例]

[0269]

接下来,参照图37来对基于第8实施例的功率放大器模块进行说明。该功率放大器模块搭载了基于从上述的第1实施例至第7实施例的任意一个实施例的半导体装置。

[0270]

图37是基于第8实施例的功率放大器模块的剖视图。在印刷布线基板200安装有半导体装置500、硅半导体芯片230以及其他多个表面安装型元件。对于半导体装置500,使用基于第1实施例至第7实施例的任意一个实施例的半导体装置。在硅半导体芯片230例如形成cmos电路。

[0271]

半导体装置500的背面电极45经由导电性粘接剂221而被固定于印刷布线基板200的下垫板201并且被电连接。硅半导体芯片230经由导电性粘接剂231而被固定于印刷布线基板200的下垫板202。在下垫板201、 202的最表面形成au膜。作为导电性粘接剂221、231,例如能够使用以使银(ag)微粒子分散的环氧树脂为主成分的粘接剂。另外,除了环氧树脂,也可以使用丙烯酸树脂、双马来酰亚胺树脂、丁二烯树脂、硅酮树脂或者将这些树脂而成的混合树脂。

[0272]

半导体装置500的多个接合焊盘140与印刷布线基板200的接合焊盘 203通过多个接合线225而被连接。作为接合线225,例如能够使用直径 20μm的au线。接合线225使用引线接合器来与接合焊盘140、203接合。

[0273]

硅半导体芯片230的多个接合焊盘232分别通过多个接合线235来与印刷布线基板200的多个接合焊盘204连接。

[0274]

半导体装置500、硅半导体芯片230、其他表面安装型元件、接合线 225、235被密封用固化树脂240密封。

[0275]

在第8实施例中,作为半导体装置500,使用基于第1实施例至第7 实施例的任意一个实施例的半导体装置,因此能够实现半导体装置500的小型化。进一步地,能够抑制接合

时的半导体装置500的损伤。由此,提供一种可靠性高的功率放大器模块。

[0276]

上述的各实施例是示例,当然可以进行不同实施例中所示的结构的局部置换或者组合。针对基于多个实施例的相同结构的相同的作用效果,不按照每个实施例来依次提及。进一步地,本发明并不局限于上述的实施例。本领域的技术人员应当清楚,例如能够进行各种变更、改进、组合等。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1