基于多级阶梯波形的低副瓣低边带电平时间调制相控阵

1.本发明属于微波技术及天线工程技术领域,特别是一种基于多级阶梯波形的低副瓣低边带电平时间调制相控阵。

背景技术:

2.随着无线系统的发展,精确制导、航空航天和导航等诸多领域对传统阵列天线提出了越来越高的要求。相控阵天线由大量相同的天线单元组成,通过控制天线单元的馈电幅度和相位以控制阵列的辐射方向图,可实现对其波束指向的控制,但是控制精度受到成本的制约。近年来,时间调制阵列这一新技术被应用于相控阵天线,它将“时间”作为第四个设计维度加入到三维空间的传统天线设计中,通过使天线受到时间调制,从而改变和控制天线的辐射特性,可实现低成本高精度的波束扫描。为了解决时间调制带来的大量无用边带的影响,时间调制相控阵通过采用特定结构的单边带时间调制器控制对应天线单元的时间特性,有效改善了频谱性能和系统效率。

3.目前,大部分单边带时间调制相控阵只具有相位加权的功能,而不具有幅度加权的功能。这是因为采用传统的时间调制的幅度加权方法,即通过射频开关周期性的通断,设置不同占空比的方式实现对应的幅度加权,会导致单边带时间调制器抑制无用边带的能力下降,造成频谱性能显著恶化。因此,基于多级阶梯波形的单边带时间调制器具有的高自由度,设计一种能保持低边带电平的单元幅度加权方法,实现低副瓣低边带电平时间调制相控阵,将具有很高的应用价值。

技术实现要素:

4.本发明的目的在于针对现有技术存在的问题,提供一种基于多级阶梯波形的低副瓣低边带电平时间调制相控阵。

5.实现本发明目的的技术解决方案为:一种基于多级阶梯波形的低副瓣低边带电平时间调制相控阵,该时间调制相控阵包括由n个天线单元构成的天线阵列,n个基于多级阶梯波形的单边带时间调制器,fpga控制电路和一个1-n功分器,n为自然数;所述时间调制相控阵作为接收天线时,射频信号依次从天线阵列、基于多级阶梯波形的单边带时间调制器,到达1-n功分器;所述时间调制相控阵作为发射天线时,射频信号依次从1-n功分器、基于多级阶梯波形的单边带时间调制器,到达天线阵列;所述fpga控制电路用于控制基于多级阶梯波形的单边带时间调制器产生阶梯形时间调制信号;该时间调制相控阵的低副瓣低边带电平由单边带时间调制器的低边带电平幅度加权实现。

6.进一步地,所述基于多级阶梯波形的单边带时间调制器包括第一威尔金森功分器、第二威尔金森功分器、同步通道、正交通道、第一端口以及第二端口;第一端口通过第一威尔金森功分器分别连接同步通道和正交通道,之后经由第二威尔金森功分器到达第二端口;所述同步通道和正交通道由来自fpga控制电路发出的周期时间序列控制生成阶梯形时间调制信号。

7.进一步地,所述同步通道包括沿第一端口指向第二端口的方向依次设置的第一数控衰减器、第一单刀双掷射频开关、第一0/180o移相器以及第二单刀双掷射频开关。

8.进一步地,所述正交通道包括沿第一端口指向第二端口的方向依次设置的第二数控衰减器、第三单刀双掷射频开关、第二0/180o移相器、第四单刀双掷射频开关以及90o移相器。

9.进一步地,所述阶梯形时间调制信号,是具有s级阶梯波形周期为t

p

的阶梯形调制波,第s级阶梯的幅度和持续时长分别为bs和τs,幅度bs由第一数控衰减器和第二数控衰减器能实现的衰减值决定。

10.进一步地,所述时间调制相控阵的低副瓣低边带电平由单边带时间调制器的低边带电平幅度加权实现,具体包括以下步骤:

11.步骤1,根据单边带时间调制器的硬件结构,确定多级阶梯时间调制信号的阶梯级数s和各级阶梯幅度bs;

12.步骤2,优化时间调制信号的各级阶梯持续时长τs,获得最低边带电平的时间调制信号;

13.步骤3,根据低副瓣相控阵的幅度加权分布,确定单边带时间调制器的目标幅度加权值a;

14.步骤4,优化时间调制信号的各级阶梯持续时长τs,获得满足目标幅度加权值a的最低边带电平的时间调制信号;

15.步骤5,基于满足目标幅度的时间调制信号,确定fpga电路的控制程序。

16.进一步地,步骤2具体为:

17.基于目标函数

[0018][0019]

优化阶梯形时间调制信号的各级持续时长τ={τ1,τ2,

…

,τs},获得最低边带电平的单边带时间调制信号;

[0020]

其中,bs、b

s-1

分别为阶梯形时间调制信号第s级、s-1级阶梯的幅度。

[0021]

进一步地,步骤3中所述目标幅度加权值其中τs′

为满足目标幅度的最低边带电平的多级阶梯时间调制信号的第s级阶梯的持续时长。

[0022]

进一步地,步骤4具体为:

[0023]

基于目标函数

[0024][0025]

优化满足目标幅度加权值的阶梯形时间调制信号的各级持续时长τ={τ1,τ2,

…

,τs},其中,w1为目标幅度加权值的加权值,w2为边带电平的加权值。

[0026]

本发明与现有技术相比,其显著优点:

[0027]

1)所设计的时间调制相控阵基于多级阶梯波形的高自由度,在实现时间调制幅度加权的同时,兼顾抑制无用边带,改善了频谱性能,更具有实用性;

[0028]

2)各单边带时间调制器采用低边带电平的幅度加权方法,使得时间调制相控阵进行低副瓣低边带电平的波束扫描时,无需针对不同波束指向反复优化控制时序以满足性能要求,仅需要调整各单元之间控制信号的时延,大大简化了系统的控制手段。

[0029]

下面结合附图对本发明作进一步详细描述。

附图说明

[0030]

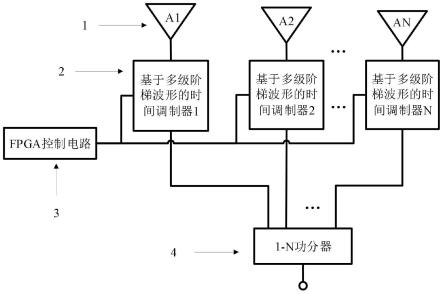

图1为本发明基于多级阶梯波形的低副瓣低边带电平时间调制相控阵结构示意图。

[0031]

图2为本发明基于多级阶梯波形的单边带时间调制器的硬件结构示意图。

[0032]

图3为本发明基于多级阶梯波形的单边带时间调制器的同相通道生成的阶梯形时间调制信号示意图。

[0033]

图4为本发明基于多级阶梯波形的单边带时间调制器的正交通道生成的阶梯形时间调制信号示意图。

[0034]

图5为本发明基于多级阶梯波形的单边带时间调制器的低边带电平幅度加权控制方法的流程图。

[0035]

图6为本发明实施例的基于多级阶梯波形的低副瓣低边带电平时间调制相控阵的仿真和实测归一化方向图。

[0036]

图7为本发明实施例的基于多级阶梯波形的低副瓣低边带电平时间调制相控阵的实测频谱图。

[0037]

图8为本发明实施例的基于多级阶梯波形的低副瓣低边带电平时间调制相控阵的实测波束扫描归一化方向图。

具体实施方式

[0038]

为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

[0039]

需要说明,若本发明实施例中有涉及“第一”、“第二”等的描述,则该“第一”、“第二”等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。另外,各个实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当认为这种技术方案的结合不存在,也不在本发明要求的保护范围之内。

[0040]

结合图1,本发明提出了一种基于多级阶梯波形的低副瓣低边带电平时间调制相控阵,包括n个天线单元构成的天线阵列1,n个基于多级阶梯波形的单边带时间调制器2,fpga控制电路3和一个1-n功分器4,n为自然数。所述时间调制相控阵作为接收天线时,射频信号依次从天线阵列1、基于多级阶梯波形的单边带时间调制器2,到达1-n功分器4;所述时

间调制相控阵作为发射天线时,射频信号依次从1-n功分器4、基于多级阶梯波形的单边带时间调制器2,到达天线阵列1;所述fpga控制电路3用于控制基于多级阶梯波形的单边带时间调制器2产生阶梯形时间调制信号;该时间调制相控阵的低副瓣低边带电平由单边带时间调制器的低边带电平幅度加权实现。所述时间调制相控阵的低副瓣低边带电平由单边带时间调制器的低边带电平幅度加权方法实现。

[0041]

结合图2,基于多级阶梯波形的单边带时间调制器是时间调制相控的核心组成部分,具体包括:第一威尔金森功分器6、第二威尔金森功分器9、同步通道7、正交通道8、第一端口5以及第二端口10;第一端口5通过第一威尔金森功分器6分别连接同步通道7和正交通道8,之后经由第二威尔金森功分器9到达第二端口10。所述同步通道7和正交通道8由来自fpga控制电路发出的周期时间序列控制生成阶梯形时间调制信号。同步通道7包括沿第一端口指向第二端口的方向依次设置的第一数控衰减器11、第一单刀双掷射频开关12、第一0/180o移相器13以及第二单刀双掷射频开关14。正交通道8包括沿第一端口指向第二端口的方向依次设置的第二数控衰减器15、第三单刀双掷射频开关16、第二0/180o移相器17、第四单刀双掷射频开关18以及90o移相器19。

[0042]

结合图3和图4,时间调制信号由fpga电路控制同步通道3和正交通道4分别生成的阶梯形时间调制信号叠加形成。所述阶梯形时间调制信号,是具有s级阶梯波形周期为t

p

的阶梯形调制波,第s级阶梯的幅度和持续时长分别为bs和τs。

[0043]

结合图5,基于单边带时间调制器的低边带电平幅度加权控制方法,包括以下步骤:

[0044]

步骤s1、根据单边带时间调制器的硬件结构,确定多级阶梯时间调制信号的阶梯级数s和各级阶梯幅度bs。

[0045]

多级阶梯时间调制信号的阶梯级数s和各级阶梯幅度bs取决于第一数控衰减器11和第二数控衰减器15可实现的幅度。

[0046]

步骤s2、优化时间调制信号的各级阶梯持续时长τs,获得最低边带电平的时间调制信号。

[0047]

为了实现单边带,保留+1次的工作边带并抑制其它无用边带,单边带时间调制信号需要拟合欧拉公式e

jωt

=cos(ωt)+jsin(ωt),从而确定同步通道3和正交通道4生成的的阶梯形时间调制信号的各级幅度bs和持续时长τs。一般情况下,同步通道3和正交通道4生成的的阶梯形时间调制信号的波形形状一致,并存在t

p

/4的时间差。

[0048]

由于采用正交调制的方式,仅有m=4k+1(k≠0)次无用边带保留。为了抑制这些边带,基于目标函数优化阶梯形时间调制信号的各级持续时长τ={τ1,τ2,

…

,τs},获得最低边带电平的单边带时间调制信号,其中,bs、b

s-1

分别为阶梯形时间调制信号第s级、s-1级阶梯的幅度。

[0049]

步骤s3、根据低副瓣相控阵的幅度加权分布,确定单边带时间调制器的目标幅度加权值a。

[0050]

以低副瓣相控阵对应的幅度加权值为基础,以最低边带电平的单边带时间调制信

号的幅度为参照,目标幅度加权值等于其中τs′

为满足目标幅度的最低边带电平的多级阶梯时间调制信号的第s级阶梯的持续时长。

[0051]

步骤s4、优化时间调制信号的各级阶梯持续时长τs,获得满足目标幅度加权值a的最低边带电平的时间调制信号。

[0052]

基于目标函数

[0053][0054]

优化满足目标幅度加权值的阶梯形时间调制信号的各级持续时长τ={τ1,τ2,

…

,τs}。其中w1为目标幅度加权值的加权值,w2为边带电平的加权值。

[0055]

当目标幅度加权值a较低时,阶梯形时间调制信号的各级持续时长τ={τ1,τ2,

…

,τs}中的部分参数为0,表位为实际阶梯形时间调制信号的级数小于s,实际最高阶梯的幅度降低。

[0056]

步骤s5、基于满足目标幅度的时间调制信号,确定fpga电路的控制程序。

[0057]

下面结合具体实施例对本发明进行进一步详细说明。

[0058]

实施例

[0059]

基于多级阶梯波形的低副瓣低边带电平时间调制相控阵由n个单边带时间调制器以及相连的n个天线单元,fpga控制电路,1-n功分器组成。

[0060]

示例性地,本发明实施例中由n个天线单元构成的整个时间调制天线阵的规模可以是任意一种需要的一维或二维阵列,例如本实施例中采用一维8单元的天线阵列,并与8个单边带时间调制器对应相连,本发明实施例对此不进行限制。

[0061]

本实施例的实测硬件电路工作于2ghz,其产生的多级阶梯时间调制信号频率为100khz。

[0062]

示例性地,本发明实施例采用8级阶梯时间调制波形(s=8)。根据实际数控衰减器的幅度分布,所有时间调制器的同步通道和正交通道的多级阶梯时间调制信号的各级阶梯幅度均满足b1=-14db,b2=-12db,b3=-10db,b4=-8db,b5=-6db,b6=-4db,b7=-2db,b8=0db。

[0063]

基于目标函数优化阶梯形时间调制信号的各级持续时长τ={τ1,τ2,

…

,τs},最低边带电平的单边带时间调制信号的各级阶梯持续时间为τ1=0.469,τ2=0.422,τ3=0.406,τ4=0.383,τ5=0.348,τ6=0.305,τ7=0.242,τ8=0.148,边带电平为-35.57db。

[0064]

示例性地,本发明实施例中时间调制相控阵为实现-25db的低副瓣,天线单元的幅度加权值采用采用切皮雪夫分布,理论值a分别为0.38、0.58、0.84、1、1、0.84、0.58、0.38,并利用单边带时间调制器实现上述幅度加权。

[0065]

经过优化,8个单边带时间调制器的多级阶梯时间调制信号的各级阶梯持续时间如下表1所示。

[0066]

表1多级阶梯时间调制信号的各级阶梯持续时间

[0067]

序号τ1τ2τ3τ4τ5τ6τ7τ810.4140.3130.2030.1020000 20.4490.3670.3520.2850.2150.06600 30.4690.4100.4060.3670.3240.2700.1840.008 40.4690.4300.4100.3910.3480.3010.2420.148 50.4690.4300.4100.3910.3480.3010.2420.148 60.4690.4100.4060.3670.3240.2700.1840.008 70.4490.3670.3520.2850.2150.06600 80.4140.3130.2030.1020000

[0068]

同一时间调制器的同步通道3和正交通道4生成的阶梯形时间调制信号的波形形状一致,并存在t

p

/4的时间差。

[0069]

最后,基于上述8个单边带时间调制器的多级阶梯时间调制信号的各级阶梯持续时间,确定fpga电路的控制程序,实现副瓣电平为-25db的时间调制相控阵。

[0070]

参见图6,为本发明实施例的基于多级阶梯波形的低副瓣低边带电平时间调制相控阵的实测和仿真归一化方向图,实测副瓣电平为-23.53db。

[0071]

参见图7,为本发明实施例的基于多级阶梯波形的低副瓣低边带电平时间调制相控阵的实测和理论频谱图,实测边带电平为-33.34db。

[0072]

参见图8,为本发明实施例的基于多级阶梯波形的低副瓣低边带电平时间调制相控阵的实测波束扫描归一化方向图,其中波束分别指向0

°

、

±

15

°

、

±

30

°

、

±

45

°

。通过fpga电路的控制,相邻单边带时间调制器产生的单边带时间调制信号之间产生δt

′

的时间差,满足:

[0073][0074]

其中,为相邻时间调制单元产生的相位差,即天线单元之间的相位差;t

p

为阶梯形时间调制脉冲的周期,β为自由空间波束,d为天线单元间距,θ0为天线阵列的波束指向。

[0075]

本发明通过优化时间调制相控阵中各单元的多级阶梯时间调制信号,在满足幅度加权的同时有效抑制边带电平,优化了时间调制相控阵的频谱特性,实现低副瓣低边带电平的性能,具有重要的实用价值。

[0076]

以上显示和描述了本发明的基本原理、主要特征及优点。本行业的技术人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中描述的只是说明本发明的原理,在不脱离本发明精神和范围的前提下,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1