一种图像传感器及其制造方法与流程

本公开实施例涉及半导体制造,尤其涉及一种图像传感器及其制造方法。

背景技术:

1、图像传感器可以划分为电荷耦合器件(charge coupled device,ccd)图像传感器和互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)图像传感器两种类型。其中,cmos图像传感器(cmos image sensor,cis)是一种利用硅半导体的光电特性来实现光电信号转换的图像传感器件,其结构简单、功耗低、成品率高且价格低廉,广泛应用于消费电子、生物医疗、安全监控和航天等领域。

2、cis包括卷帘快门(rolling shutter)cis和全局快门(global shutter)cis两种类型。其中,卷帘快门cis指的是一帧中各行的曝光时刻不同,下一行的曝光时刻比上一行推迟一个行读出周期,而一帧中最后一行的曝光时刻比第一行推迟了一个帧的读出周期;而全局快门cis指的是所有像素的曝光时刻均相同,同时开始曝光,同时结束曝光。

3、然而,由于卷帘快门cis的逐行曝光的特性,存在不可避免的“果冻效应”,尤其是在拍摄高速运动的物体时,会造成图像的严重失真。这里“果冻效应”指的是使用卷帘快门的方式拍摄,逐行扫描速度不够,拍摄结果就可能出现“倾斜”、“摇摆不定”或“部分曝光”等情况。

4、不同于卷帘快门cis采用逐行曝光的方式,全局快门cis采用整个像素阵列同时开始曝光和完成曝光的方式工作,因此,使用全局快门cis可以完美地解决卷帘快门cis逐行曝光时导致的不同行像素之间的偏差。随着人们对于高清图像的不断追求以及高速机器视觉、工业测量、航空航天等领域的发展,对于高性能全局快门cis的需求日益迫切。

技术实现思路

1、有鉴于此,本公开实施例为解决现有技术中存在的至少一个技术问题而提供一种图像传感器及其制造方法。

2、为达到上述目的,本公开的技术方案是这样实现的:

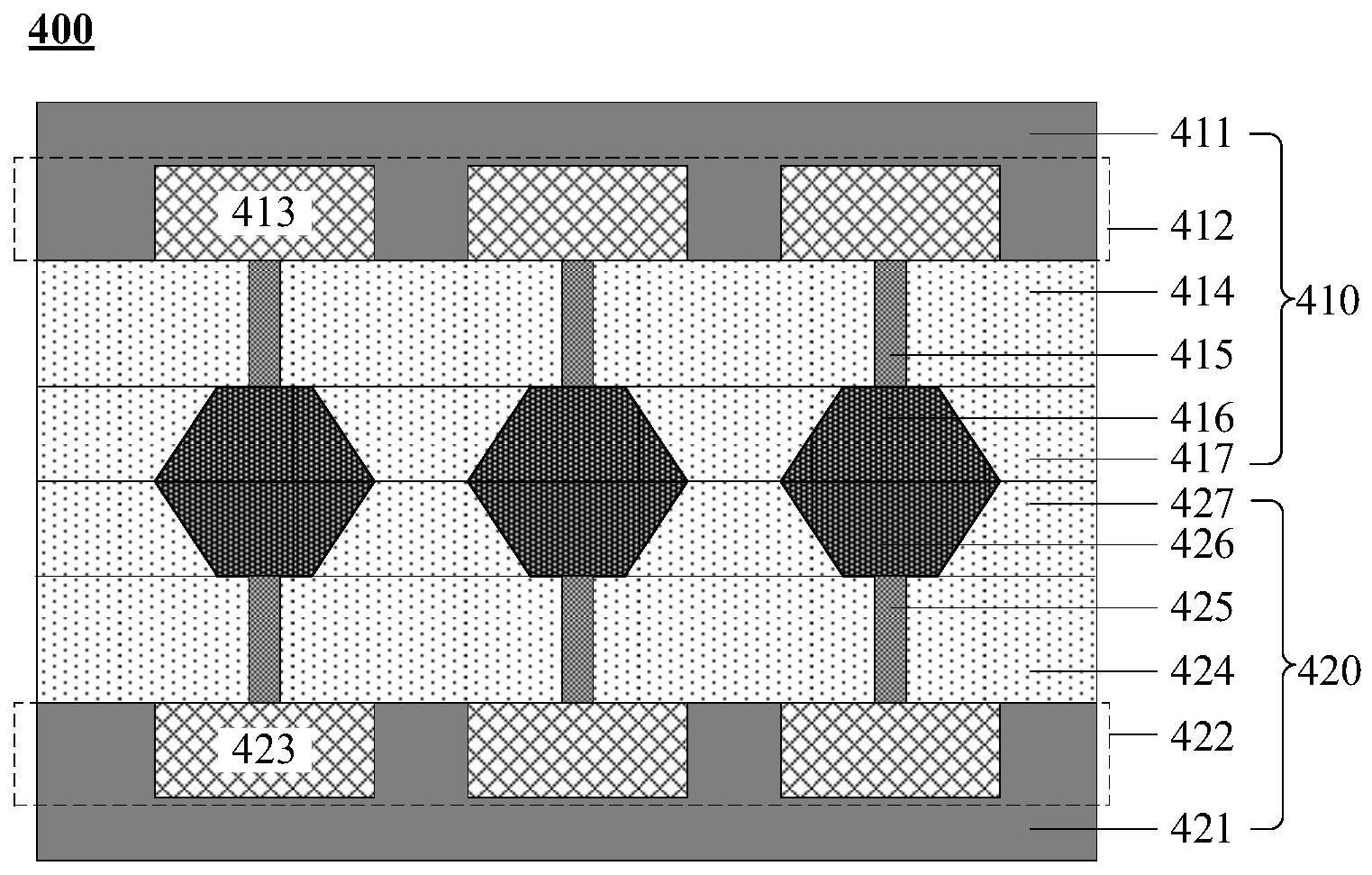

3、第一方面,本公开实施例提供一种图像传感器,所述图像传感器包括:相互键合的第一半导体结构和第二半导体结构;其中,

4、所述第一半导体结构包括像素阵列,所述像素阵列包括多个呈阵列排布的像素单元;其中,每个所述像素单元包括光电二极管,所述光电二极管用于将光信号转换为电信号;

5、所述第二半导体结构包括逻辑电路,所述逻辑电路包括多个晶体管;所述晶体管包括复位晶体管、源极跟随晶体管和行选择晶体管;其中,所述复位晶体管用于对所述像素单元进行复位,所述源极跟随晶体管用于输出所述电信号,所述行选择晶体管用于将所述源极跟随晶体管输出的所述电信号选择输出。

6、在一些实施例中,所述第一半导体结构的相邻所述像素单元之间设有第一隔离结构;所述第二半导体结构的相邻所述晶体管之间设有第二隔离结构;其中,所述第一隔离结构和所述第二隔离结构不同。

7、在一些实施例中,每个所述像素单元还包括传输晶体管和浮置扩散区,所述传输晶体管和所述光电二极管连接,用于将所述电信号传输至所述浮置扩散区。

8、在一些实施例中,所述光电二极管包括:

9、设于第一衬底内的第一掺杂类型的第一掺杂区;

10、设于所述第一衬底内且位于所述第一掺杂区上方的第二掺杂类型的第二掺杂区,所述第一掺杂区用于收集所述光信号转换生成的电荷;其中,所述传输晶体管的栅极用于将所述第一掺杂区收集的电荷转移至所述浮置扩散区。

11、在一些实施例中,所述晶体管包括:

12、设于第二衬底内的第三掺杂区和第四掺杂区;

13、位于所述第二衬底之上的控制栅极,且所述控制栅极位于所述第三掺杂区和所述第四掺杂区之间;其中,所述第一掺杂区和所述第三掺杂区不同,所述第一掺杂区和所述第四掺杂区不同。

14、在一些实施例中,所述第一半导体结构还包括:位于所述像素阵列上方的第一互连层和位于所述第一互连层上方的第一键合层;其中,所述第一键合层包括第一介质层和设于所述第一介质层内的第一键合触点,所述第一介质层的表面和所述第一键合触点的表面基本齐平;

15、所述第二半导体结构还包括:位于所述逻辑电路上方的第二互连层和位于所述第二互连层上方的第二键合层;其中,所述第二键合层包括第二介质层和设于所述第二介质层内的第二键合触点,所述第二介质层的表面和所述第二键合触点的表面基本齐平。

16、在一些实施例中,所述图像传感器还包括:

17、键合界面,位于所述第一键合层和所述第二键合层之间,所述第一键合触点在所述键合界面处和所述第二键合触点接触。

18、第二方面,本公开实施例提供一种图像传感器的制造方法,所述制造方法包括:

19、形成第一半导体结构,所述第一半导体结构包括像素阵列,所述像素阵列包括多个呈阵列排布的像素单元;其中,每个所述像素单元包括光电二极管,所述光电二极管用于将光信号转换为电信号;

20、形成第二半导体结构,所述第二半导体结构包括逻辑电路,所述逻辑电路包括多个晶体管;所述晶体管包括复位晶体管、源极跟随晶体管和行选择晶体管;

21、将所述第一半导体结构和所述第二半导体结构进行键合,使得所述像素阵列和所述逻辑电路之间电连接;其中,所述复位晶体管用于对所述像素单元进行复位,所述源极跟随晶体管用于输出所述电信号,所述行选择晶体管用于将所述源极跟随晶体管输出的所述电信号选择输出。

22、在一些实施例中,所述形成第一半导体结构,包括:

23、对第一衬底进行刻蚀,以形成多个第一凹槽;

24、对所述第一凹槽进行填充,以形成多个第一隔离结构;

25、所述形成第二半导体结构,包括:

26、对第二衬底进行刻蚀,以形成多个第二凹槽;

27、对所述第二凹槽进行填充,以形成多个第二隔离结构;其中,所述第一隔离结构和所述第二隔离结构不同。

28、在一些实施例中,每个所述像素单元还包括:传输晶体管和浮置扩散区,所述传输晶体管和所述光电二极管连接,用于将所述电信号传输至所述浮置扩散区。

29、在一些实施例中,任意相邻两个所述第一隔离结构之间设有第一有源区;所述形成第一半导体结构,还包括:

30、在所述第一衬底的所述第一有源区内形成第一掺杂类型的第一掺杂区;

31、在所述第一衬底的所述第一有源区内且位于所述第一掺杂区的上方形成具有第二掺杂类型的第二掺杂区;所述第一掺杂区用于收集所述光信号转换生成的电荷;其中,所述传输晶体管的栅极用于将所述第一掺杂区收集的电荷转移至所述浮置扩散区。

32、在一些实施例中,任意相邻两个所述第二隔离结构之间设有第二有源区;所述形成第二半导体结构,还包括:

33、在所述第二衬底的所述第二有源区内形成第三掺杂区和第四掺杂区;

34、在所述第二衬底的所述第二有源区之上形成控制栅极,且所述控制栅极位于所述第三掺杂区和所述第四掺杂区之间;其中,所述第一掺杂区和所述第三掺杂区不同,所述第一掺杂区和所述第四掺杂区不同。

35、在一些实施例中,所述形成第一半导体结构,包括:

36、在所述像素阵列上形成第一互连层;

37、在所述第一互连层上形成第一键合层;其中,所述第一键合层包括第一介质层和设于所述第一介质层内的第一键合触点,所述第一介质层的表面和所述第一键合触点的表面基本齐平;

38、所述形成第二半导体结构,包括:

39、在所述逻辑电路上形成第二互连层;

40、在所述第二互连层上形成第二键合层;其中,所述第二键合层包括第二介质层和设于所述第二介质层内的第二键合触点,所述第二介质层的表面和所述第二键合触点的表面基本齐平。

41、在一些实施例中,所述将所述第一半导体结构和所述第二半导体结构进行键合,包括:

42、对所述第一半导体结构和所述第二半导体结构进行预处理;

43、对所述第一半导体结构和所述第二半导体结构进行键合对准,使得所述第一键合触点和所述第二键合触点一一接触;

44、进行退火处理,使得所述像素阵列和所述逻辑电路通过所述第一键合触点和所述第二键合触点电连接。

45、在一些实施例中,所述对所述第一半导体结构和所述第二半导体结构进行预处理,包括:

46、对所述第一键合层和所述第二键合层进行等离子体活化处理;

47、对所述第一键合层和所述第二键合层进行清洗,以形成亲水性表面。

48、本公开实施例提供一种图像传感器及其制造方法。所述图像传感器包括:相互键合的第一半导体结构和第二半导体结构;其中,所述第一半导体结构包括像素阵列,所述像素阵列包括多个呈阵列排布的像素单元;其中,每个所述像素单元包括光电二极管,所述光电二极管用于将光信号转换为电信号;所述第二半导体结构包括逻辑电路,所述逻辑电路包括多个晶体管;所述晶体管包括复位晶体管、源极跟随晶体管和行选择晶体管;其中,所述复位晶体管用于对所述像素单元进行复位,所述源极跟随晶体管用于输出所述电信号,所述行选择晶体管用于将所述源极跟随晶体管输出的所述电信号选择输出。本公开实施例中,第一半导体结构包括像素阵列,像素阵列的像素单元包括光电二极管,而第二半导体结构包括逻辑电路,逻辑电路的晶体管包括复位晶体管、源极跟随晶体管和行选择晶体管,形成像素阵列和逻辑电路的工艺技术标准不同,分别形成包括像素阵列的第一半导体结构和包括逻辑电路的第二半导体结构,混合键合后形成图像传感器,有利于简化制造工艺流程,且降低工艺难度。

- 还没有人留言评论。精彩留言会获得点赞!