层叠型线圈部件的制作方法

1.本实用新型涉及层叠型线圈部件。

背景技术:

2.作为高频特性优异的层叠型线圈部件,在专利文献1中,公开了40ghz下的透射系数s21为-1.0db以上且0db以下的层叠型线圈部件。

3.专利文献1:日本特开2019-186255号公报

4.然而,随着高速

·

大容量通信的发展,要求层叠型线圈部件直到更加高频带的透射系数s21大,并且直到高频带的透射系数s21的偏差小。

技术实现要素:

5.本实用新型是为了解决上述问题而完成的,其目的在于提供一种高频带下的透射系数s21大,并且其偏差小的层叠型线圈部件。

6.本实用新型的层叠型线圈部件的特征在于,具备:基体,通过在层叠方向上层叠多个绝缘层,并且具有在长度方向上对置的第一端面及第二端面、在与上述长度方向正交的高度方向上对置的第一主面及第二主面、以及在与上述长度方向及上述高度方向正交的宽度方向上对置的第一侧面及第二侧面;线圈,设置在上述基体的内部,并且通过将多个线圈导体电连接而形成;以及第一外部电极,从上述基体的上述第一端面的至少一部分遍及上述第一主面的一部分地延伸,并且与上述线圈电连接,上述绝缘层的上述层叠方向和上述线圈的线圈轴的方向平行于作为安装面的上述基体的上述第一主面,在上述基体的至少一部分存在包含fe、ni、zn以及cu的磁性相和包含si的非磁性相,上述第一外部电极从上述基体侧起依次具有基底电极和设置在上述基底电极上的镀层电极,上述镀层电极中的存在于上述基体的上述第一主面上的部分的上述长度方向的末端位于比上述基底电极中的存在于上述基体的上述第一主面上的部分的上述长度方向的末端靠上述基体的上述第二端面侧,上述镀层电极的上述末端与上述基底电极的上述末端之间的上述长度方向上的距离为30μm以下。

7.根据本实用新型,能够提供一种高频带下的透射系数s21大,并且其偏差小的层叠型线圈部件。

附图说明

8.图1是表示本实用新型的层叠型线圈部件的一个例子的立体示意图。

9.图2是表示从基体的第一端面侧观察图1中的层叠型线圈部件的状态的平面示意图。

10.图3是表示从基体的第一主面侧观察图1中的层叠型线圈部件的状态的平面示意图。

11.图4是表示从基体的第一侧面侧观察图1中的层叠型线圈部件的状态的平面示意

图。

12.图5是表示从基体的第二侧面侧观察图1中的层叠型线圈部件的状态的平面示意图。

13.图6是表示从基体的第二端面侧观察图1中的层叠型线圈部件的状态的平面示意图。

14.图7是表示与图1中的线段a1-a2对应的部分的一个例子的截面示意图。

15.图8是表示将图7中的基体及线圈分解后的状态的一个例子的立体示意图。

16.图9是表示将图7中的基体及线圈分解后的状态的一个例子的平面示意图。

17.图10是图1中的层叠型线圈部件的侧面示意图。

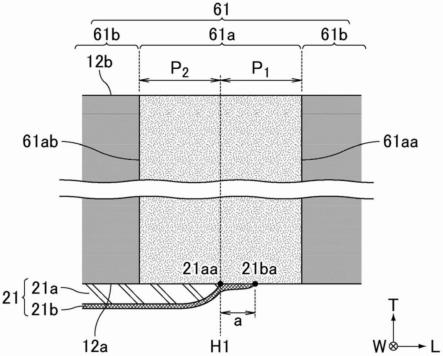

18.图11是表示图10中的第一基体部分及第一外部电极的沿着长度方向及高度方向的截面的一部分的示意图。

19.图12是表示图10中的第二基体部分及第二外部电极的沿着长度方向及高度方向的截面的一部分的示意图。

20.图13是表示层叠型线圈部件的试样1、试样3以及试样4的透射系数s21的测定结果的图表。

21.附图标记说明

[0022]1…

层叠型线圈部件;10

…

基体;11a

…

第一端面;11b

…

第二端面;12a

…

第一主面;12b

…

第二主面;13a

…

第一侧面;13b

…

第二侧面;15、15a、15b、15c、15d、15e

…

绝缘层;21

…

第一外部电极;21a、22a

…

基底电极;21aa、22aa

…

基底电极中的存在于基体的第一主面上的部分的长度方向的末端;21b、22b

…

镀层电极;21ba、22ba

…

镀层电极中的存在于基体的第一主面上的部分的长度方向的末端;22

…

第二外部电极;30

…

线圈;31、31a、31b、31c、31d

…

线圈导体;34a、34b、34c、34d、34e

…

导通孔导体;41

…

第一连结导体;42

…

第二连结导体;50a

…

第一轮廓线;50b

…

第二轮廓线;50c

…

第三轮廓线;50d

…

第四轮廓线;50e

…

第五轮廓线;50f

…

第六轮廓线;50g

…

第七轮廓线;50h

…

第八轮廓线;61

…

第一基体部分;61a、62a

…

第一区域;61aa、62ab

…

第一区域中的第二端面侧的端部;61ab、62aa

…

第一区域中的第一端面侧的端部;61b、62b

…

第二区域;62

…

第二基体部分;a、b

…

镀层电极中的存在于基体的第一主面上的部分的长度方向的末端与基底电极中的存在于基体的第一主面上的部分的长度方向的末端之间的长度方向上的距离;c

…

线圈轴;e1…

第一外部电极的高度方向上的尺寸;e2…

第一外部电极的长度方向上的尺寸;e3…

第二外部电极的高度方向上的尺寸;e4…

第二外部电极的长度方向上的尺寸;g

…

界面;h1

…

第一基准位置;h2

…

第二基准位置;l

…

长度方向;l1…

层叠型线圈部件的长度方向上的尺寸;l2…

基体的长度方向上的尺寸;l3…

线圈的长度方向上的尺寸;p1、p2…

距第一基准位置的长度方向上的尺寸或距离;q1、q2…

距第二基准位置的长度方向上的尺寸或距离;t

…

高度方向;t1…

层叠型线圈部件的高度方向上的尺寸;t2…

基体的高度方向上的尺寸;w

…

宽度方向;w1…

层叠型线圈部件的宽度方向上的尺寸;w2…

基体的宽度方向上的尺寸。

具体实施方式

[0023]

以下,对本实用新型的层叠型线圈部件进行说明。此外,本实用新型并不限定于以下的结构,在不脱离本实用新型的主旨的范围内可以适当地变更。另外,将以下记载的各个

优选结构组合多个的结构也是本实用新型。

[0024]

本实用新型的层叠型线圈部件具备:基体,通过在层叠方向上层叠多个绝缘层而形成,并且具有在长度方向上对置的第一端面及第二端面、在与长度方向正交的高度方向上对置的第一主面及第二主面、以及在与长度方向及高度方向正交的宽度方向上对置的第一侧面及第二侧面;线圈,设置在基体的内部,并且通过将多个线圈导体电连接而形成;以及第一外部电极,从基体的第一端面的至少一部分遍及第一主面的一部分地延伸,并且与线圈电连接。

[0025]

图1是表示本实用新型的层叠型线圈部件的一个例子的立体示意图。

[0026]

如图1所示,层叠型线圈部件1具有基体10、第一外部电极21以及第二外部电极22。虽然在图1中未示出,但如后所述,层叠型线圈部件1还具有设置在基体10的内部的线圈。

[0027]

在本说明书中,如图1等所示,将长度方向、高度方向以及宽度方向分别设为由l、t以及w确定的方向。这里,长度方向l、高度方向t以及宽度方向w相互正交。

[0028]

基体10具有在长度方向l上对置的第一端面11a及第二端面11b、在高度方向t上对置的第一主面12a及第二主面12b、以及在宽度方向w上对置的第一侧面13a及第二侧面13b,例如为长方体状或大致长方体状。

[0029]

基体10的第一端面11a及第二端面11b不需要严格地与长度方向l正交。另外,基体10的第一主面12a及第二主面12b不需要严格地与高度方向t正交。另外,基体10的第一侧面13a及第二侧面13b不需要严格地与宽度方向w正交。

[0030]

在将层叠型线圈部件1安装于基板的情况下,基体10的第一主面12a成为安装面。

[0031]

优选基体10在角部及棱线部带有圆角。基体10的角部是基体10的3个面相交的部分。基体10的棱线部是基体10的2个面相交的部分。

[0032]

图2是表示从基体的第一端面侧观察图1中的层叠型线圈部件的状态的平面示意图。图3是表示从基体的第一主面侧观察图1中的层叠型线圈部件的状态的平面示意图。图4是表示从基体的第一侧面侧观察图1中的层叠型线圈部件的状态的平面示意图。图5是表示从基体的第二侧面侧观察图1中的层叠型线圈部件的状态的平面示意图。图6是表示从基体的第二端面侧观察图1中的层叠型线圈部件的状态的平面示意图。

[0033]

如图1、图2以及图3所示,第一外部电极21从基体10的第一端面11a的至少一部分,这里从基体10的第一端面11a的一部分遍及第一主面12a的一部分地延伸。若第一外部电极21设置在作为安装面的基体10的第一主面12a上,则层叠型线圈部件1的安装性提高。

[0034]

如图2所示,第一外部电极21覆盖基体10的第一端面11a中的包含与第一主面12a相交的棱线部的区域,而不覆盖包含与第二主面12b相交的棱线部的区域。因此,基体10的第一端面11a在包含与第二主面12b相交的棱线部的区域露出。

[0035]

在从长度方向l观察时,第一外部电极21的高度方向t上的尺寸e1在图2中沿着宽度方向w是恒定的,但也可以不是恒定的。例如,在从长度方向l观察时,第一外部电极21也可以是高度方向t上的尺寸e1沿着宽度方向w随着从端部朝向中央部而变大的山形。

[0036]

第一外部电极21可以如图1及图2所示设置在基体10的第一端面11a的一部分上,也可以设置在基体10的第一端面11a的整体上。

[0037]

如图3所示,第一外部电极21覆盖基体10的第一主面12a中的包含与第一端面11a相交的棱线部的区域,而不覆盖包含与第二端面11b相交的棱线部的区域。

[0038]

在从高度方向t观察时,第一外部电极21的长度方向l上的尺寸e2在图3中沿着宽度方向w是恒定的,但也可以不是恒定的。例如,在从高度方向t观察时,第一外部电极21也可以是长度方向l上的尺寸e2沿着宽度方向w随着从端部朝向中央部而变大的山形。

[0039]

如图1、图4以及图5所示,第一外部电极21可以从基体10的第一端面11a的一部分,遍及第一主面12a的一部分、以及第一侧面13a的一部分和第二侧面13b的一部分地延伸。更具体而言,第一外部电极21可以覆盖基体10的第一侧面13a中的包含与第一端面11a及第一主面12a相交的顶点的区域,并且不覆盖包含与第一端面11a及第二主面12b相交的顶点的区域。另外,第一外部电极21可以覆盖基体10的第二侧面13b中的包含与第一端面11a及第一主面12a相交的顶点的区域,并且不覆盖包含与第一端面11a及第二主面12b相交的顶点的区域。

[0040]

如图4所示,优选在第一外部电极21中,覆盖基体10的第一侧面13a的部分的轮廓线除了包含与第一侧面13a及第一端面11a相交的棱线部对置的第一轮廓线50a、和与第一侧面13a及第一主面12a相交的棱线部对置的第二轮廓线50b之外,还包含相对于第一轮廓线50a及第二轮廓线50b倾斜的轮廓线。

[0041]

如图5所示,优选在第一外部电极21中,覆盖基体10的第二侧面13b的部分的轮廓线除了包含与第二侧面13b及第一端面11a相交的棱线部对置的第三轮廓线50c、和与第二侧面13b及第一主面12a相交的棱线部对置的第四轮廓线50d之外,还包含相对于第三轮廓线50c及第四轮廓线50d倾斜的轮廓线。

[0042]

第一外部电极21也可以不设置在基体10的第一侧面13a上。另外,第一外部电极21也可以不设置在基体10的第二侧面13b上。

[0043]

第一外部电极21也可以从基体10的第一端面11a遍及第一主面12a、第二主面12b、第一侧面13a、以及第二侧面13b的各面的一部分地延伸。

[0044]

如图1、图3以及图6所示,第二外部电极22从基体10的第二端面11b的至少一部分,这里从基体10的第二端面11b的一部分,遍及第一主面12a的一部分地延伸。若第二外部电极22设置在作为安装面的基体10的第一主面12a上,则层叠型线圈部件1的安装性提高。

[0045]

如图6所示,第二外部电极22覆盖基体10的第二端面11b中的包含与第一主面12a相交的棱线部的区域,而不覆盖包含与第二主面12b相交的棱线部的区域。因此,基体10的第二端面11b在包含与第二主面12b相交的棱线部的区域露出。

[0046]

在从长度方向l观察时,第二外部电极22的高度方向t上的尺寸e3在图6中沿着宽度方向w是恒定的,但也可以不是恒定的。例如,在从长度方向l观察时,第二外部电极22也可以是高度方向t上的尺寸e3沿着宽度方向w随着从端部朝向中央部而变大的山形。

[0047]

第二外部电极22可以如图1及图6所示设置在基体10的第二端面11b的一部分上,也可以设置在基体10的第二端面11b的整体上。

[0048]

如图3所示,第二外部电极22覆盖基体10的第一主面12a中的包含与第二端面11b相交的棱线部的区域,而不覆盖包含与第一端面11a相交的棱线部的区域。

[0049]

在从高度方向t观察时,第二外部电极22的长度方向l上的尺寸e4在图3中沿着宽度方向w是恒定的,但也可以不是恒定的。例如,在从高度方向t观察时,第二外部电极22也可以是长度方向l上的尺寸e4沿着宽度方向w随着从端部朝向中央部而变大的山形。

[0050]

如图1、图4以及图5所示,第二外部电极22可以从基体10的第二端面11b的一部分,

遍及第一主面12a的一部分、以及第一侧面13a的一部分和第二侧面13b的一部分地延伸。更具体而言,第二外部电极22可以覆盖基体10的第一侧面13a中的包含与第二端面11b及第一主面12a相交的顶点的区域,并且不覆盖包含与第二端面11b及第二主面12b相交的顶点的区域。另外,第二外部电极22可以覆盖基体10的第二侧面13b中的包含与第二端面11b及第一主面12a相交的顶点的区域,并且不覆盖包含与第二端面11b及第二主面12b相交的顶点的区域。

[0051]

如图4所示,优选在第二外部电极22中,覆盖基体10的第一侧面13a的部分的轮廓线除了包含与第一侧面13a及第二端面11b相交的棱线部对置的第五轮廓线50e、和与第一侧面13a及第一主面12a相交的棱线部对置的第六轮廓线50f之外,还包含相对于第五轮廓线50e及第六轮廓线50f倾斜的轮廓线。

[0052]

如图5所示,优选在第二外部电极22中,覆盖基体10的第二侧面13b的部分的轮廓线除了包含与第二侧面13b及第二端面11b相交的棱线部对置的第七轮廓线50g、和与第二侧面13b及第一主面12a相交的棱线部对置的第八轮廓线50h之外,还包含相对于第七轮廓线50g及第八轮廓线50h倾斜的轮廓线。

[0053]

第二外部电极22也可以不设置在基体10的第一侧面13a上。另外,第二外部电极22也可以不设置在基体10的第二侧面13b上。

[0054]

第二外部电极22也可以从基体10的第二端面11b遍及第一主面12a、第二主面12b、第一侧面13a以及第二侧面13b的各面的一部分地延伸。

[0055]

层叠型线圈部件1的尺寸没有特别限定,但优选为0603尺寸、0402尺寸或1005尺寸。

[0056]

针对层叠型线圈部件1为0603尺寸、0402尺寸或1005尺寸的情况,以下示出层叠型线圈部件1、基体10、第一外部电极21以及第二外部电极22的优选尺寸的具体例。

[0057]

(1)在层叠型线圈部件1为0603尺寸的情况下

[0058]

·

层叠型线圈部件1的长度方向l上的尺寸l1优选为0.57mm以上。另外,层叠型线圈部件1的长度方向l上的尺寸l1优选为0.63mm以下。

[0059]

·

层叠型线圈部件1的高度方向t上的尺寸t1优选为0.27mm以上。另外,层叠型线圈部件1的高度方向t上的尺寸t1优选为0.33mm以下。

[0060]

·

层叠型线圈部件1的宽度方向w上的尺寸w1优选为0.27mm以上。另外,层叠型线圈部件1的宽度方向w上的尺寸w1优选为0.33mm以下。

[0061]

·

基体10的长度方向l上的尺寸l2优选为0.57mm以上。另外,基体10的长度方向l上的尺寸l2优选为0.63mm以下。

[0062]

·

基体10的高度方向t上的尺寸t2优选为0.27mm以上。另外,基体10的高度方向t上的尺寸t2优选为0.33mm以下。

[0063]

·

基体10的宽度方向w上的尺寸w2优选为0.27mm以上。另外,基体10的宽度方向w上的尺寸w2优选为0.33mm以下。

[0064]

·

第一外部电极21的高度方向t上的尺寸e1优选为0.10mm以上且0.20mm以下。此外,在第一外部电极21的高度方向t上的尺寸e1沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0065]

·

第一外部电极21的长度方向l上的尺寸e2优选为0.12mm以上且0.22mm以下。此

外,在第一外部电极21的长度方向l上的尺寸e2沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0066]

·

第二外部电极22的高度方向t上的尺寸e3优选为0.10mm以上且0.20mm以下。此外,在第二外部电极22的高度方向t上的尺寸e3沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0067]

·

第二外部电极22的长度方向l上的尺寸e4优选为0.12mm以上且0.22mm以下。此外,在第二外部电极22的长度方向l上的尺寸e4沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0068]

(2)在层叠型线圈部件1为0402尺寸的情况下

[0069]

·

层叠型线圈部件1的长度方向l上的尺寸l1优选为0.38mm以上。另外,层叠型线圈部件1的长度方向l上的尺寸l1优选为0.42mm以下。

[0070]

·

层叠型线圈部件1的高度方向t上的尺寸t1优选为0.18mm以上。另外,层叠型线圈部件1的高度方向t上的尺寸t1优选为0.22mm以下。

[0071]

·

层叠型线圈部件1的宽度方向w上的尺寸w1优选为0.18mm以上。另外,层叠型线圈部件1的宽度方向w上的尺寸w1优选为0.22mm以下。

[0072]

·

基体10的长度方向l上的尺寸l2优选为0.38mm以上。另外,基体10的长度方向l上的尺寸l2优选为0.42mm以下。

[0073]

·

基体10的高度方向t上的尺寸t2优选为0.18mm以上。另外,基体10的高度方向t上的尺寸t2优选为0.22mm以下。

[0074]

·

基体10的宽度方向w上的尺寸w2优选为0.18mm以上。另外,基体10的宽度方向w上的尺寸w2优选为0.22mm以下。

[0075]

·

第一外部电极21的高度方向t上的尺寸e1优选为0.06mm以上且0.13mm以下。此外,在第一外部电极21的高度方向t上的尺寸e1沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0076]

·

第一外部电极21的长度方向l上的尺寸e2优选为0.08mm以上且0.15mm以下。此外,在第一外部电极21的长度方向l上的尺寸e2沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0077]

·

第二外部电极22的高度方向t上的尺寸e3优选为0.06mm以上且0.13mm以下。此外,在第二外部电极22的高度方向t上的尺寸e3沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0078]

·

第二外部电极22的长度方向l上的尺寸e4优选为0.08mm以上且0.15mm以下。此外,在第二外部电极22的长度方向l上的尺寸e4沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0079]

(3)在层叠型线圈部件1为1005尺寸的情况下

[0080]

·

层叠型线圈部件1的长度方向l上的尺寸l1优选为0.95mm以上。另外,层叠型线圈部件1的长度方向l上的尺寸l1优选为1.05mm以下。

[0081]

·

层叠型线圈部件1的高度方向t上的尺寸t1优选为0.45mm以上。另外,层叠型线圈部件1的高度方向t上的尺寸t1优选为0.55mm以下。

[0082]

·

层叠型线圈部件1的宽度方向w上的尺寸w1优选为0.45mm以上。另外,层叠型线

圈部件1的宽度方向w上的尺寸w1优选为0.55mm以下。

[0083]

·

基体10的长度方向l上的尺寸l2优选为0.95mm以上。另外,基体10的长度方向l上的尺寸l2优选为1.05mm以下。

[0084]

·

基体10的高度方向t上的尺寸t2优选为0.45mm以上。另外,基体10的高度方向t上的尺寸t2优选为0.55mm以下。

[0085]

·

基体10的宽度方向w上的尺寸w2优选为0.45mm以上。另外,基体10的宽度方向w上的尺寸w2优选为0.55mm以下。

[0086]

·

第一外部电极21的高度方向t上的尺寸e1优选为0.15mm以上且0.33mm以下。此外,在第一外部电极21的高度方向t上的尺寸e1沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0087]

·

第一外部电极21的长度方向l上的尺寸e2优选为0.20mm以上且0.38mm以下。此外,在第一外部电极21的长度方向l上的尺寸e2沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0088]

·

第二外部电极22的高度方向t上的尺寸e3优选为0.15mm以上且0.33mm以下。此外,在第二外部电极22的高度方向t上的尺寸e3沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0089]

·

第二外部电极22的长度方向l上的尺寸e4优选为0.20mm以上且0.38mm以下。此外,在第二外部电极22的长度方向l上的尺寸e4沿着宽度方向w不是恒定的情况下,优选其最大值在上述范围内。

[0090]

在本实用新型的层叠型线圈部件中,绝缘层的层叠方向和线圈的线圈轴的方向平行于作为安装面的基体的第一主面。

[0091]

图7是表示与图1中的线段a1-a2对应的部分的一个例子的截面示意图。

[0092]

如图7所示,基体10通过将多个绝缘层15在层叠方向,这里为长度方向l上层叠而形成。即,绝缘层15的层叠方向与长度方向l平行,与作为安装面的基体10的第一主面12a平行。此外,在图7中,为了便于说明,示出了这些绝缘层15的边界,但实际上没有明显地显现边界。

[0093]

在基体10的内部设置有线圈30。线圈30通过将多个线圈导体31电连接而形成,例如呈螺线管状。线圈导体31与绝缘层15一起在长度方向l上层叠。此外,在图7中,没有严格地示出线圈30的形状、线圈导体31的位置、线圈导体31的连接等。例如,在长度方向l上相邻的线圈导体31经由图7中未示出的导通孔导体相互电连接。

[0094]

线圈30具有线圈轴c。线圈30的线圈轴c沿长度方向l延伸,并且贯通基体10的第一端面11a与第二端面11b之间。即,线圈30的线圈轴c的方向平行于作为安装面的基体10的第一主面12a。另外,线圈30的线圈轴c经过从长度方向l观察时的线圈30的形状的中心。

[0095]

如上所述,绝缘层15的层叠方向和线圈30的线圈轴c的方向平行于作为安装面的基体10的第一主面12a。

[0096]

绝缘层15的层叠方向和线圈30的线圈轴c的方向可以如图7所示与长度方向l平行,也可以不平行。例如,也可以是绝缘层15的层叠方向与宽度方向w平行,并且线圈30的线圈轴c的方向与长度方向l平行。在该情况下,绝缘层15的层叠方向和线圈30的线圈轴c的方向也平行于作为安装面的基体10的第一主面12a。

[0097]

层叠型线圈部件1也可以还具有第一连结导体41及第二连结导体42。

[0098]

第一连结导体41通过将图7中未示出的多个导通孔导体电连接并与绝缘层15一起在长度方向l上层叠而形成。第一连结导体41从基体10的第一端面11a露出。

[0099]

第一外部电极21经由第一连结导体41与线圈30电连接。这里,在多个线圈导体31中,在离基体10的第一端面11a最近的位置设置有线圈导体31a。即,第一外部电极21经由第一连结导体41与线圈导体31a电连接。

[0100]

第一连结导体41将第一外部电极21与线圈30连接。第一连结导体41优选呈直线状连接第一外部电极21与线圈30之间,这里连接第一外部电极21与线圈导体31a之间。另外,优选在从长度方向l观察时,第一连结导体41与线圈导体31a重叠,并且位于比线圈轴c靠作为安装面的基体10的第一主面12a侧。由此,第一外部电极21与线圈30的电连接变得容易。

[0101]

第一连结导体41呈直线状连接第一外部电极21与线圈30之间表示在从长度方向l观察时,构成第一连结导体41的导通孔导体彼此重叠。因此,构成第一连结导体41的导通孔导体彼此也可以不是严格地呈直线状排列。

[0102]

第一连结导体41优选与线圈导体31a中的离基体10的第一主面12a最近的部分连接。由此,能够减小第一外部电极21中的在基体10的第一端面11a上的部分的面积。其结果,第一外部电极21与线圈30之间的杂散电容变小,因此层叠型线圈部件1的高频特性相应地提高。

[0103]

第一连结导体41可以仅设置一个,也可以设置多个。

[0104]

第二连结导体42通过将图7中未示出的多个导通孔导体电连接并与绝缘层15一起在长度方向l上层叠而形成。第二连结导体42从基体10的第二端面11b露出。

[0105]

第二外部电极22经由第二连结导体42与线圈30电连接。这里,在多个线圈导体31中,在离基体10的第二端面11b最近的位置设置有线圈导体31d。即,第二外部电极22经由第二连结导体42与线圈导体31d电连接。

[0106]

第二连结导体42将第二外部电极22与线圈30连接。第二连结导体42优选呈直线状连接第二外部电极22与线圈30之间,这里连接第二外部电极22与线圈导体31d之间。另外,优选在从长度方向l观察时,第二连结导体42与线圈导体31d重叠,并且位于比线圈轴c靠作为安装面的基体10的第一主面12a侧。由此,第二外部电极22与线圈30的电连接变得容易。

[0107]

第二连结导体42呈直线状连接第二外部电极22与线圈30之间表示在从长度方向l观察时,构成第二连结导体42的导通孔导体彼此重叠。因此,构成第二连结导体42的导通孔导体彼此也可以不是严格地呈直线状排列。

[0108]

第二连结导体42优选与线圈导体31d中的离基体10的第一主面12a最近的部分连接。由此,能够减小第二外部电极22中的在基体10的第二端面11b上的部分的面积。其结果,第二外部电极22与线圈30之间的杂散电容变小,层叠型线圈部件1的高频特性相应地提高。

[0109]

第二连结导体42可以仅设置一个,也可以设置多个。

[0110]

线圈30的长度方向l上的尺寸l3优选为基体10的长度方向l上的尺寸l2的85%以上且94%以下,更优选为90%以上且94%以下。

[0111]

线圈30的长度方向l上的尺寸l3表示从经由第一连结导体41与第一外部电极21电连接的线圈导体31a到经由第二连结导体42与第二外部电极22电连接的线圈导体31d的、长度方向l上的距离(包含线圈导体31a及线圈导体31d的长度方向l上的尺寸)。即,线圈30的

长度方向l上的尺寸l3表示线圈导体31的配置区域的长度方向l上的尺寸。

[0112]

在线圈30的长度方向l上的尺寸l3小于基体10的长度方向l上的尺寸l2的85%的情况下,线圈30的杂散电容变大,因此存在层叠型线圈部件1的高频特性降低的担忧。在线圈30的长度方向l上的尺寸l3大于基体10的长度方向l上的尺寸l2的94%的情况下,第一外部电极21与线圈30之间的杂散电容变大,另外,第二外部电极22与线圈30之间的杂散电容变大,因此存在层叠型线圈部件1的高频特性降低的担忧。

[0113]

图8是表示将图7中的基体及线圈分解后的状态的一个例子的立体示意图。图9是表示将图7中的基体及线圈分解后的状态的一个例子的平面示意图。

[0114]

在图8及图9所示的例子中,基体10将作为绝缘层15的绝缘层15a、绝缘层15b、绝缘层15c、绝缘层15d、以及绝缘层15e在层叠方向,这里为长度方向l上层叠。

[0115]

在本说明书中,在没有特别区分绝缘层15a、绝缘层15b、绝缘层15c、绝缘层15d、以及绝缘层15e的情况下,称为绝缘层15。

[0116]

在绝缘层15a、绝缘层15b、绝缘层15c、以及绝缘层15d的主面上分别设置有作为线圈导体31的线圈导体31a、线圈导体31b、线圈导体31c、以及线圈导体31d。线圈导体31a、线圈导体31b、线圈导体31c、以及线圈导体31d与绝缘层15a、绝缘层15b、绝缘层15c、以及绝缘层15d一起在长度方向l上层叠,各线圈导体电连接。

[0117]

在本说明书中,在没有特别区分线圈导体31a、线圈导体31b、线圈导体31c、以及线圈导体31d的情况下,称为线圈导体31。

[0118]

在图8及图9所示的例子中,线圈导体31a、线圈导体31b、线圈导体31c、以及线圈导体31d的长度分别是线圈30的3/4匝的长度。即,用于构成线圈30的3匝的线圈导体的层叠数为4。在基体10中,将线圈导体31a、线圈导体31b、线圈导体31c、以及线圈导体31d作为一个单位(3匝的量)重复层叠。

[0119]

在线圈导体31的两端也可以设置有焊盘部。更具体而言,在线圈导体31a、线圈导体31b、线圈导体31c、以及线圈导体31d的各两端也可以设置有焊盘部。

[0120]

在从长度方向l观察时,线圈导体31的焊盘部可以为圆形形状,也可以为多边形形状。

[0121]

在绝缘层15a、绝缘层15b、绝缘层15c、以及绝缘层15d分别以在长度方向l上贯通的方式设置有导通孔导体34a、导通孔导体34b、导通孔导体34c、以及导通孔导体34d。

[0122]

导通孔导体34a、导通孔导体34b、导通孔导体34c、以及导通孔导体34d分别与线圈导体31a、线圈导体31b、线圈导体31c、以及线圈导体31d的一端连接。如上所述,在线圈导体31a、线圈导体31b、线圈导体31c、以及线圈导体31d的各两端设置有焊盘部的情况下,导通孔导体34a、导通孔导体34b、导通孔导体34c、以及导通孔导体34d分别与线圈导体31a的焊盘部、线圈导体31b的焊盘部、线圈导体31c的焊盘部、以及线圈导体31d的焊盘部连接。

[0123]

将带线圈导体31a及导通孔导体34a的绝缘层15a、带线圈导体31b及导通孔导体34b的绝缘层15b、带线圈导体31c及导通孔导体34c的绝缘层15c、以及带线圈导体31d及导通孔导体34d的绝缘层15d作为一个单位(图8及图9中的虚线包围的部分)重复层叠。由此,线圈导体31a、线圈导体31b、线圈导体31c以及线圈导体31d经由导通孔导体34a、导通孔导体34b、导通孔导体34c、以及导通孔导体34d电连接。即,在长度方向l上相邻的线圈导体经由导通孔导体相互电连接。

[0124]

由此,构成设置于基体10的内部的螺线管状的线圈30。

[0125]

在从长度方向l观察时,线圈30可以是圆形形状,也可以是多边形形状。此外,在线圈30包含焊盘部的情况下,例如,在线圈导体31的两端设置有焊盘部的情况下,线圈30的形状表示除去焊盘部的形状。

[0126]

在从长度方向l观察时,线圈导体31的内径优选为基体10的宽度方向w上的尺寸w2的15%以上且40%以下。线圈导体31的内径与线圈30的线圈直径同义。在从长度方向l观察时,在线圈30为多边形形状的情况下,将多边形的面积相当圆的直径作为线圈30的线圈直径,即线圈导体31的内径。

[0127]

线圈30的匝数优选为35以上,更优选为35以上且45以下。若线圈30的匝数为35以上,则层叠型线圈部件1的阻抗变大,高频带下的透射系数s21也变大。其结果,层叠型线圈部件1的高频特性提高。

[0128]

在绝缘层15e以沿长度方向l贯通的方式设置有导通孔导体34e。

[0129]

在绝缘层15e的主面上也可以设置有与导通孔导体34e连接的焊盘部。

[0130]

带导通孔导体34e的绝缘层15e多个层叠为与位于线圈30的一端侧的带线圈导体31a及导通孔导体34a的绝缘层15a重叠。由此,导通孔导体34e彼此电连接而构成第一连结导体41,第一连结导体41从基体10的第一端面11a露出。其结果,第一外部电极21与线圈导体31a经由第一连结导体41相互电连接。

[0131]

带导通孔导体34e的绝缘层15e多个层叠为与位于线圈30的另一端侧的带线圈导体31d及导通孔导体34d的绝缘层15d重叠。由此,导通孔导体34e彼此电连接而构成第二连结导体42,第二连结导体42从基体10的第二端面11b露出。其结果,第二外部电极22与线圈导体31d经由第二连结导体42相互电连接。

[0132]

第一连结导体41及第二连结导体42的长度方向l上的尺寸分别优选为基体10的长度方向l上的尺寸l2的2.5%以上且7.5%以下,更优选为2.5%以上且5.0%以下。由此,第一连结导体41及第二连结导体42的电感变小,因此层叠型线圈部件1的高频特性提高。

[0133]

第一连结导体41及第二连结导体42的宽度方向w上的尺寸分别优选为基体10的宽度方向w上的尺寸w2的8.0%以上且20%以下。

[0134]

针对层叠型线圈部件1为0603尺寸、0402尺寸或1005尺寸的情况,以下示出线圈导体31、第一连结导体41以及第二连结导体42的优选尺寸的具体例。

[0135]

(1)在层叠型线圈部件1为0603尺寸的情况下

[0136]

·

在从长度方向l观察时,线圈导体31的内径优选为50μm以上且100μm以下。

[0137]

·

第一连结导体41及第二连结导体42的长度方向l上的尺寸分别优选为15μm以上且45μm以下,更优选为15μm以上且30μm以下。

[0138]

·

第一连结导体41及第二连结导体42的宽度方向w上的尺寸分别优选为30μm以上且60μm以下。

[0139]

(2)在层叠型线圈部件1为0402尺寸的情况下

[0140]

·

在从长度方向l观察时,线圈导体31的内径优选为30μm以上且70μm以下。

[0141]

·

第一连结导体41及第二连结导体42的长度方向l上的尺寸分别优选为10μm以上且30μm以下,更优选为10μm以上且25μm以下。

[0142]

·

第一连结导体41及第二连结导体42的宽度方向w上的尺寸分别优选为20μm以上

且40μm以下。

[0143]

(3)在层叠型线圈部件1为1005尺寸的情况下

[0144]

·

在从长度方向l观察时,线圈导体31的内径优选为80μm以上且170μm以下。

[0145]

·

第一连结导体41及第二连结导体42的长度方向l上的尺寸分别优选为25μm以上且75μm以下,更优选为25μm以上且50μm以下。

[0146]

·

第一连结导体41及第二连结导体42的宽度方向w上的尺寸分别优选为40μm以上且100μm以下。

[0147]

作为线圈导体31a、线圈导体31b、线圈导体31c、线圈导体31d、导通孔导体34a、导通孔导体34b、导通孔导体34c、导通孔导体34d、以及导通孔导体34e的构成材料,例如可列举ag、au、cu、pd、ni、al、含有这些金属中的至少1种的合金等。

[0148]

在本实用新型的层叠型线圈部件中,在基体的至少一部分存在包含fe、ni、zn以及cu的磁性相与包含si的非磁性相。

[0149]

在层叠型线圈部件1中,在基体10的至少一部分存在包含fe、ni、zn以及cu的磁性相与包含si的非磁性相。

[0150]

磁性相可以还包含co、bi、sn、mn等。

[0151]

磁性相优选由ni-cu-zn系铁氧体材料构成。

[0152]

ni-cu-zn系铁氧体材料优选在将总重量设为100mоl%时,包含:以fe2o3换算计40mol%以上且49.5mol%以下的fe、以nio换算计10mol%以上且45mol%以下的ni、以zno换算计2mol%以上且35mol%以下的zn、以cuo换算计6mol%以上且13mol%以下的cu。

[0153]

ni-cu-zn系铁氧体材料可以还包含co、bi、sn、mn等添加物、不可避免的杂质等。

[0154]

非磁性相优选由硼硅酸盐玻璃材料构成。

[0155]

硼硅酸盐玻璃材料优选在将总重量设为100重量%时,包含:以sio2换算计70重量%以上且85重量%以下的si、以b2o3换算计10重量%以上且25重量%以下的b、以a2o换算计0.5重量%以上且5重量%以下的碱金属a、以al2o3换算计0重量%以上且5重量%以下的al。

[0156]

硼硅酸盐玻璃材料可以还包含镁橄榄石(2mgo

·

sio2)、石英(sio2)等作为填料。

[0157]

非磁性相也可以由azno

·

sio2(a为1.8以上且2.2以下)表示的氧化物构成。作为这样的氧化物,例如可列举被称为硅锌矿的zn2sio4等。在这样的氧化物中,zn的一部分也可以被cu置换。

[0158]

对于磁性相及非磁性相,如以下那样进行区别。首先,通过对层叠型线圈部件,实施研磨直到宽度方向的大致中央部,从而使图7等所示的沿着长度方向及高度方向的截面露出。接下来,针对基体的露出截面,通过扫描式透射电子显微镜-能量色散x射线分析(stem-edx)进行元素映射。然后,将存在fe的区域作为磁性相,将存在si的区域作为非磁性相,来区分两相。

[0159]

图10是图1中的层叠型线圈部件的侧面示意图。

[0160]

在图10所示的例子中,在层叠型线圈部件1中,当在基体10的长度方向l的中心位置定义了沿着高度方向t及宽度方向w的界面g时,基体10具有以界面g为界在长度方向l上排列的、包含第一端面11a的第一基体部分61和包含第二端面11b的第二基体部分62。即,基体10在长度方向l上被界面g分割为第一基体部分61和第二基体部分62这两部分。

[0161]

关于界面g,基体10的长度方向l的中心位置被确定为将基体10的长度方向l上的最大尺寸平分的位置。

[0162]

第一外部电极21设置在第一基体部分61的表面上。

[0163]

第二外部电极22设置在第二基体部分62的表面上。

[0164]

在本实用新型的层叠型线圈部件中,第一外部电极从基体侧起依次具有基底电极和设置在基底电极上的镀层电极,镀层电极中的存在于基体的第一主面上的部分的长度方向的末端位于比基底电极中的存在于基体的第一主面上的部分的长度方向的末端靠基体的第二端面侧。

[0165]

图11是表示图10中的第一基体部分及第一外部电极的沿着长度方向及高度方向的截面的一部分的示意图。

[0166]

如图11所示,第一外部电极21从基体10侧起依次具有基底电极21a和设置在基底电极21a上的镀层电极21b。

[0167]

镀层电极21b中的存在于基体10的第一主面12a上的部分的长度方向l的末端21ba位于比基底电极21a中的存在于基体10的第一主面12a上的部分的长度方向l的末端21aa靠基体10的第二端面11b侧(在图11中为右侧)。

[0168]

基底电极中的存在于基体的第一主面上的部分的长度方向的末端和镀层电极中的存在于基体的第一主面上的部分的长度方向的末端在层叠型线圈部件中,由宽度方向的大致中央部处的沿着长度方向及高度方向的截面确定。

[0169]

如本实用新型的层叠型线圈部件那样,在具有基底电极及镀层电极的外部电极中,镀层电极往往成为沿着基体的表面相对于基底电极大幅伸长的状态。这样,当以镀层电极大幅伸长的状态形成外部电极时,外部电极与线圈之间的杂散电容变大,结果,存在层叠型线圈部件的高频特性降低的担忧。

[0170]

与此相对,在本实用新型的层叠型线圈部件中,镀层电极的末端与基底电极的末端之间的长度方向上的距离为30μm以下。

[0171]

在层叠型线圈部件1中,镀层电极21b中的存在于基体10的第一主面12a上的部分的长度方向l的末端21ba与基底电极21a中的存在于基体10的第一主面12a上的部分的长度方向l的末端21aa之间的长度方向l上距离a为30μm以下。更具体而言,镀层电极21b的末端21ba与基底电极21a的末端21aa之间的长度方向l上的距离a比0μm大且为30μm以下。在该情况下,镀层电极21b不会沿着基体10的第一主面12a相对于基底电极21a大幅伸长,能够抑制线圈30与第一外部电极21之间的杂散电容变大,因此层叠型线圈部件1的高频特性相应地提高。

[0172]

在镀层电极21b的末端21ba与基底电极21a的末端21aa之间的长度方向l上的距离a大于30μm的情况下,镀层电极21b沿着基体10的第一主面12a相对于基底电极21a大幅伸长,无法抑制线圈30与第一外部电极21之间的杂散电容变大。

[0173]

如以上那样,在本实用新型的层叠型线圈部件中,即使外部电极,这里为第一外部电极具有镀层电极,由于镀层电极的末端与基底电极的末端之间的长度方向上的距离为30μm以下,因此高频特性也优异。即,在本实用新型的层叠型线圈部件中,高频带下的透射系数s21大,并且直到高频带的透射系数s21的偏差变小。

[0174]

基底电极21a优选包含ag。

[0175]

镀层电极21b优选包含ni及sn中的至少一方。

[0176]

镀层电极21b可以是单层构造,也可以是多层构造,但优选为多层构造。在镀层电极21b为多层构造的情况下,镀层电极21b优选从基底电极21a侧起依次具有ni镀层电极和sn镀层电极。

[0177]

除了利用能量色散x射线分析(edx)的元素分析之外,还利用在图11所示的沿着长度方向及高度方向的截面中致密等信息,将镀层电极21b这样的镀层电极与利用镀覆以外的方法形成的基底电极21a这样的基底电极区分开。

[0178]

在定义了与基底电极21a的末端21aa在高度方向t上重叠的第一基准位置h1时,在第一基体部分61优选存在至少包含从第一基准位置h1朝向第二端面11b(在图11中,朝向右侧)长度方向l上的尺寸p1为20μm的范围的第一区域61a。即,第一区域61a优选至少包含从第一基准位置h1朝向第二端面11b的长度方向l上的距离p1为0μm的位置到20μm的位置的范围。

[0179]

第一区域61a中的第二端面11b侧的端部61aa优选存在于距第一基准位置h1的长度方向l上的距离p1为20μm以上且60μm以下的位置。即,第一区域61a优选包含从第一基准位置h1朝向第二端面11b的长度方向l上的距离p1为0μm的位置到α1μm的位置的范围(20≤α1≤60)。

[0180]

优选第一区域61a还至少包含从第一基准位置h1朝向第一端面11a(在图11中,朝向左侧)长度方向l上的尺寸p2为20μm的范围。即,优选第一区域61a还至少包含从第一基准位置h1朝向第一端面11a的长度方向l上的距离p2为0μm的位置到20μm的位置的范围。

[0181]

第一区域61a中的第一端面11a侧的端部61ab优选存在于距第一基准位置h1的长度方向l上的距离p2为20μm以上且60μm以下的位置。即,优选第一区域61a还包含从第一基准位置h1朝向第一端面11a的长度方向l上的距离p2为0μm的位置到α2μm的位置的范围(20≤α2≤60)。

[0182]

优选在第一区域61a仅存在非磁性相,或者存在非磁性相及磁性相双方。由此,在形成镀层电极21b时,能够抑制镀层电极21b沿着基体10的第一主面12a相对于基底电极21a大幅伸长。即,镀层电极21b的末端21ba与基底电极21a的末端21aa之间的长度方向l上的距离a容易成为30μm以下。其结果,镀层电极21b的末端21ba优选如图11所示,停留在与第一区域61a重叠的位置。

[0183]

在第一区域61a中,非磁性相的体积相对于磁性相及非磁性相的合计体积的比例优选为60体积%以上。更具体而言,在第一区域61a中,非磁性相的体积相对于磁性相及非磁性相的合计体积的比例优选为60体积%以上且100体积%以下。由此,在形成镀层电极21b时,镀层电极21b的末端21ba与基底电极21a的末端21aa之间的长度方向l上的距离a容易成为30μm以下。

[0184]

第一区域61a优选在将总重量设为100重量%时,包含以sio2换算计30.0重量%以上的si。由此,在形成镀层电极21b时,镀层电极21b的末端21ba与基底电极21a的末端21aa之间的长度方向l上的距离a容易成为30μm以下。

[0185]

另外,第一区域61a优选在将总重量设为100重量%时,包含以sio2换算计85.0重量%以下的si。

[0186]

第一区域61a优选在将总重量设为100重量%时,包含:以sio2换算计30.0重量%

以上且85.0重量%以下的si、以b2o3换算计4.0重量%以上且15.0重量%以下的b、以fe2o3换算计0重量%以上且45.0重量%以下的fe、以nio换算计0重量%以上且15.0重量%以下的ni、以zno换算计0重量%以上且8.0重量%以下的zn、以cuo换算计0重量%以上且5.0重量%以下的cu。

[0187]

第一区域61a优选在将总重量设为100重量%时,还包含:以k2o换算计0.3重量%以上且1.5重量%以下的k、以mgo换算计0.9重量%以上且3.5重量%以下的mg。

[0188]

优选在第一基体部分61还存在第一区域61a以外的第二区域61b。

[0189]

优选在第二区域61b仅存在磁性相,或者存在磁性相及非磁性相双方。由此,层叠型线圈部件1的阻抗容易变大。其结果,容易提高层叠型线圈部件1的高频特性。

[0190]

在第二区域61b中,非磁性相的体积相对于磁性相及非磁性相的合计体积的比例优选为50体积%以下。更具体而言,在第二区域61b中,非磁性相的体积相对于磁性相及非磁性相的合计体积的比例优选为0体积%以上且50体积%以下。由此,在第二区域61b中,磁性相的体积相对于磁性相及非磁性相的合计体积的比例为非磁性相的体积相对于磁性相及非磁性相的合计体积的比例同等以上,因此层叠型线圈部件1的阻抗容易变大。其结果,容易提高层叠型线圈部件1的高频特性。

[0191]

在第一区域及第二区域的每一个中,非磁性相的体积相对于磁性相及非磁性相的合计体积的比例如以下那样确定。首先,通过对层叠型线圈部件,实施研磨直到宽度方向的大致中央部,从而使图7、图11等所示的沿着长度方向及高度方向的截面露出。接下来,在第一基体部分的露出截面,测定第一区域的非磁性相的体积比例的情况下,选择从第一基准位置朝向第二端面在长度方向上的尺寸为20μm的范围作为对象区域。另外,在第一基体部分的露出截面,测定第二区域的非磁性相的体积比例的情况下,选择从第一端面朝向第二端面在长度方向上的尺寸为20μm的范围作为对象区域。然后,在各对象区域中,提取三处20μm角的区域后,通过扫描式透射电子显微镜-能量色散x射线分析进行元素映射,由此如上述那样将磁性相与非磁性相区分开。然后,对于上述三处的各区域,根据得到的元素映射图像,利用图像分析软件测定非磁性相的面积相对于磁性相及非磁性相的合计面积的比例。然后,根据这些面积比例的测定值来计算平均值,将该平均值作为非磁性相的体积相对于磁性相及非磁性相的合计体积的比例。

[0192]

第二区域61b优选在将总重量设为100重量%时,包含以sio2换算计25.0重量%以下的si。由此,层叠型线圈部件1的阻抗容易变大。其结果,容易提高层叠型线圈部件1的高频特性。

[0193]

此外,第二区域61b也可以不包含si。

[0194]

第二区域61b优选在将总重量设为100重量%时,包含:以sio2换算计0重量%以上且25.0重量%以下的si、以b2o3换算计0重量%以上且5.0重量%以下的b、以fe2o3换算计45.0重量%以上且70.0重量%以下的fe、以nio换算计10.0重量%以上且20.0重量%以下的ni、以zno换算计5.0重量%以上且12.0重量%以下的zn。

[0195]

优选第一区域61a中的总重量为100重量%时的si的含量与第二区域61b中的总重量为100重量%时的si的含量相比,以sio2换算计多出7.0重量%以上。即,第一区域61a中的总重量为100重量%时的si的含量与第二区域61b中的总重量为100重量%时的si的含量之差优选为以sio2换算计7.0重量%以上。另外,第一区域61a中的总重量为100重量%时的

si的含量与第二区域61b中的总重量为100重量%时的si的含量之差优选为60.0重量%以下。此外,第二区域61b中的总重量为100重量%时的si的含量也可以为0重量%。

[0196]

第一区域及第二区域的组成通过针对上述各对象区域,利用电感耦合等离子体发射光谱法/电感耦合等离子体质谱法(icp-aes/ms)进行分析来确认。

[0197]

在第一基体部分61优选存在第一区域61a及第二区域61b,但也可以仅存在第一区域61a。

[0198]

对于第二基体部分62及第二外部电极22,如以下所示,也优选具有与第一基体部分61及第一外部电极21相同的结构。

[0199]

图12是表示图10中的第二基体部分及第二外部电极的沿着长度方向及高度方向的截面的一部分的示意图。

[0200]

如图12所示,第二外部电极22从基体10侧起依次具有基底电极22a和设置在基底电极22a上的镀层电极22b。

[0201]

镀层电极22b中的存在于基体10的第一主面12a上的部分的长度方向l的末端22ba位于比基底电极22a中的存在于基体10的第一主面12a上的部分的长度方向l的末端22aa靠基体10的第一端面11a侧(在图11中为左侧)。

[0202]

镀层电极22b中的存在于基体10的第一主面12a上的部分的长度方向l的末端22ba与基底电极22a中的存在于基体10的第一主面12a上的部分的长度方向l的末端22aa之间的长度方向l上的距离b为30μm以下。更具体而言,镀层电极22b的末端22ba与基底电极22a的末端22aa之间的长度方向l上的距离b比0μm大且为30μm以下。

[0203]

基底电极22a及镀层电极22b的优选结构分别与基底电极21a及镀层电极21b的优选结构相同。

[0204]

在定义了与基底电极22a的末端22aa在高度方向t上重叠的第二基准位置h2时,优选在第二基体部分62存在至少包含从第二基准位置h2朝向第一端面11a(在图12中,朝向左侧)长度方向l上的尺寸q1为20μm的范围的第一区域62a。即,优选第一区域62a至少包含从第二基准位置h2朝向第一端面11a的长度方向l上的距离q1为0μm的位置到20μm的位置的范围。

[0205]

第一区域62a中的第一端面11a侧的端部62aa优选存在于距第二基准位置h2的长度方向l上的距离q1为20μm以上且60μm以下的位置。即,第一区域62a优选包含从第二基准位置h2朝向第一端面11a的长度方向l上的距离q1为0μm的位置到β1μm的位置的范围(20≤β1≤60)。

[0206]

优选第一区域62a还至少包含从第二基准位置h2朝向第二端面11b(在图12中,朝向右侧)长度方向l上的尺寸q2为20μm的范围。即,优选第一区域62a还至少包含从第二基准位置h2朝向第二端面11b的长度方向l上的距离q2为0μm的位置到20μm的位置的范围。

[0207]

第一区域62a中的第二端面11b侧的端部62ab优选存在于距第二基准位置h2的长度方向l上的距离q2为20μm以上且60μm以下的位置。即,优选第一区域62a还包含从第二基准位置h2朝向第二端面11b的长度方向l上的距离q2为0μm的位置到β2μm的位置的范围(20≤β2≤60)。

[0208]

优选在第一区域62a仅存在非磁性相,或者存在非磁性相及磁性相双方。

[0209]

优选在第二基体部分62还存在第一区域62a以外的第二区域62b。

[0210]

优选在第二区域62b仅存在磁性相,或者存在磁性相及非磁性相双方。

[0211]

第一区域62a及第二区域62b各自中的非磁性相的体积相对于磁性相及非磁性相的合计体积的优选比例与第一区域61a及第二区域61b各自中的非磁性相的体积相对于磁性相及非磁性相的合计体积的优选比例相同。

[0212]

对于第二基体部分,第一区域及第二区域各自中的非磁性相的体积相对于磁性相及非磁性相的合计体积的比例也如上述那样确定。此外,在第二基体部分的露出截面,测定第一区域的非磁性相的体积比例的情况下,选择从第二基准位置朝向第一端面在长度方向上的尺寸为20μm的范围作为对象区域。另外,在第二基体部分的露出截面,测定第二区域的非磁性相的体积比例的情况下,选择从第二端面朝向第一端面在长度方向上的尺寸为20μm的范围作为对象区域。

[0213]

第一区域62a及第二区域62b的优选组成分别与第一区域61a及第二区域61b的优选组成相同。

[0214]

在第二基体部分62优选存在第一区域62a及第二区域62b,但也可以仅存在第一区域62a。

[0215]

层叠型线圈部件1例如通过以下的方法来制造。

[0216]

<磁性材料制作工序>

[0217]

首先,称量fe2o3、nio、zno以及cuo使它们成为规定的比例。

[0218]

接下来,将这些称量物湿式混合后,进行粉碎,由此制成浆料。关于称量物的混合时间,例如为4小时以上、8小时以下。

[0219]

然后,使所得到的浆料干燥后,进行预烧。关于预烧温度,例如为700℃以上、800℃以下。关于预烧时间,例如为2小时以上、5小时以下。

[0220]

这样,制作粉末状的磁性材料,更具体而言,制作粉末状的铁氧体材料。

[0221]

铁氧体材料优选在将总重量设为100mоl%时,包含:以fe2o3换算计40mol%以上且49.5mol%以下的fe、以nio换算计10mol%以上且45mol%以下的ni、以zno换算计2mol%以上且35mol%以下的zn、以cuo换算计6mol%以上且13mol%以下的cu。

[0222]

<非磁性材料制作工序>

[0223]

首先,准备以规定的比例包含si、b、碱金属、al的硼硅酸盐玻璃粉末。

[0224]

硼硅酸盐玻璃材料优选在将总重量设为100重量%时,包含:以sio2换算计70重量%以上且85重量%以下的si、以b2o3换算计10重量%以上且25重量%以下的b、以a2o换算计0.5重量%以上且5重量%以下的碱金属a、以al2o3换算计0重量%以上且5重量%以下的al。

[0225]

接下来,作为填料,准备镁橄榄石粉末以及石英粉末。

[0226]

然后,将硼硅酸盐玻璃粉末、镁橄榄石粉末以及石英粉末以成为规定的比例的方式湿式混合后,进行粉碎,由此制成非磁性材料。

[0227]

<生片制作工序>

[0228]

首先,将磁性材料及非磁性材料称量为规定的比例。接下来,将这些称量物与聚乙烯醇缩丁醛系树脂等有机粘合剂、乙醇、甲苯等有机溶剂以及增塑剂等混合后,进行粉碎,由此制成浆料。然后,通过刮刀法等将所得到的浆料成型为规定厚度的片状后,冲裁成规定的形状,由此制作生片。

[0229]

在制作生片时,通过调整磁性材料及非磁性材料的配合比例,制作非磁性材料的体积相对于磁性材料及非磁性材料的合计体积的比例为60体积%以上的第一种生片、和非磁性材料的体积相对于磁性材料及非磁性材料的合计体积的比例为50体积%以下的第二种生片。

[0230]

此外,也可以在制作生片时,通过调整磁性材料及非磁性材料的配合比例,制作在将总重量设为100重量%时包含以sio2换算计30.0重量%以上的si的第三种生片、和在将总重量设为100重量%时包含以sio2换算计25.0重量%以下的si的第四种生片。

[0231]

以下,在不特别区分第一种生片、第二种生片、第三种生片以及第四种生片的情况下,简称为“生片”。

[0232]

在以下的工序中,对作为生片,组合使用第一种生片及第二种生片的情况进行说明。此外,在作为生片,组合使用第三种生片及第四种生片的情况下也是同样的。

[0233]

<导体图案形成工序>

[0234]

首先,通过对生片的规定部位进行激光照射,形成通孔。

[0235]

接下来,通过丝网印刷法等,将ag糊剂等导电性糊剂填充到通孔并涂布于生片的表面。由此,对于生片,在通孔形成导通孔导体用导体图案,并且在表面上形成与导通孔导体用导体图案连接的线圈导体用导体图案。这样,制作在生片形成有线圈导体用导体图案以及导通孔导体用导体图案的线圈片。制作多张线圈片,对各线圈片形成与图8及图9所示的线圈导体相当的线圈导体用导体图案、和与图8及图9所示的导通孔导体相当的导通孔导体用导体图案。

[0236]

另外,通过利用丝网印刷法等将ag糊剂等导电性糊剂填充到通孔,与线圈片不同地制作在生片形成有导通孔导体用导体图案的导通片。也制作多张导通片,对各导通片形成与图8及图9所示的导通孔导体相当的导通孔导体用导体图案。

[0237]

在制作线圈片及导通片时,在之后形成的基体的第一基体部分及第二基体部分,对于在想要作为第一区域的区域配置的片,使用第一种生片,对于在想要作为第二区域的区域配置的片,使用第二种生片。

[0238]

<层叠体预制件制作工序>

[0239]

将线圈片以及导通片以相当于图8及图9的顺序沿层叠方向层叠后,进行热压接合,由此制作层叠体预制件。由此,在层叠体预制件中,在之后形成的基体的第一基体部分及第二基体部分,在想要作为第一区域的区域配置第一种生片,在想要作为第二区域的区域配置第二种生片。

[0240]

<基体以及线圈制作工序>

[0241]

首先,通过利用切割机等将层叠体预制件切断为规定的大小,制作分片化的芯片。

[0242]

接下来,对分片化的芯片进行煅烧。关于煅烧温度,例如为900℃以上、920℃以下。另外,关于煅烧时间,例如为2小时以上、4小时以下。

[0243]

通过对分片化的芯片进行煅烧,线圈片及导通片的生片成为绝缘层。其结果,制作将多个绝缘层在层叠方向,这里为长度方向上层叠而形成的基体。

[0244]

这里,如上所述,在制作层叠体预制件时,在基体的第一基体部分及第二基体部分,在想要作为第一区域的区域配置第一种生片,在想要作为第二区域的区域配置第二种生片。因此,在本工序中制作的基体的第一基体部分及第二基体部分中,在第一区域中,非

磁性相的体积相对于磁性相及非磁性相的合计体积的比例为60体积%以上,另外,在第二区域中,非磁性相的体积相对于磁性相及非磁性相的合计体积的比例为50体积%以下。

[0245]

通过对分片化的芯片进行煅烧,线圈片的线圈导体用导体图案以及导通孔导体用导体图案分别成为线圈导体以及导通孔导体。其结果,制造将多个线圈导体在长度方向上层叠,并且经由导通孔导体电连接而形成的线圈。

[0246]

由此,制作基体和设置在基体的内部的线圈。绝缘层的层叠方向和线圈的线圈轴的方向与作为安装面的基体的第一主面平行,这里,与长度方向平行。

[0247]

通过对分片化的芯片进行煅烧,导通片的导通孔导体用导体图案成为导通孔导体。其结果,制作将多个导通孔导体在长度方向上层叠且电连接而形成的第一连结导体及第二连结导体。第一连结导体从基体的第一端面露出。第二连结导体从基体的第二端面露出。

[0248]

对于基体,例如也可以通过实施滚筒研磨,使角部及棱线部带有圆角。

[0249]

<外部电极形成工序>

[0250]

首先,使基体倾斜地浸渍于将包含ag及玻璃料的导电性糊剂拉伸为规定的厚度而成的层。接下来,通过对所得到的涂膜进行烧结,形成从基体的第一端面的一部分遍及第一主面、第一侧面以及第二侧面的各面的一部分地延伸的基底电极。同样地,形成从基体的第二端面的一部分遍及第一主面、第一侧面以及第二侧面的各面的一部分地延伸的基底电极。关于涂膜的烧结温度,例如为800℃以上、820℃以下。

[0251]

然后,通过电镀等,在各基底电极上依次形成ni镀层电极和sn镀层电极。

[0252]

此时,镀层电极中的存在于基体的第一主面上的部分的长度方向的末端位于比基底电极中的存在于基体的第一主面上的部分的长度方向的末端靠基体的第二端面侧,但镀层电极的末端,这里为sn镀层电极的末端与基底电极的末端之间的长度方向上的距离为30μm以下。

[0253]

作为使镀层电极的末端与基底电极的末端之间的长度方向上的距离为30μm以下的方法,例如可列举如上述那样,在制作层叠体预制件时,在基体的第一基体部分及第二基体部分,在想要作为第一区域的区域配置第一种生片的方法。若使用这样的方法,则在所制作的基体的第一基体部分及第二基体部分中,在第一区域中,非磁性相的体积相对于磁性相及非磁性相的合计体积的比例为60体积%以上。因此,在形成镀层电极时,镀层电极的末端与基底电极的末端之间的长度方向上的距离容易成为30μm以下。

[0254]

这样,形成经由第一连结导体与线圈电连接的第一外部电极和经由第二连结导体与线圈电连接的第二外部电极。

[0255]

由此,制造层叠型线圈部件1。

[0256]

【实施例】

[0257]

以下,表示更具体地公开了本实用新型的层叠型线圈部件的实施例。此外,本实用新型并不限定于这些实施例。

[0258]

通过以下的方法制造层叠型线圈部件的试样1~5。

[0259]

<磁性材料制作工序>

[0260]

首先,以fe2o3为48.0mol%、nio为14.0mol%、zno为30.0mol%、cuo为8.0mol%的比例进行称量。接下来,将这些称量物与纯水和psz(部分稳定化氧化锆)介质一起放入球磨

机并混合6小时后,进行粉碎,由此制成浆料。然后,使所得到的浆料干燥后,在800℃下预烧2小时。这样,制作粉末状的磁性材料,更具体而言,制作粉末状的铁氧体材料。

[0261]

<非磁性材料制作工序>

[0262]

首先,准备以规定的比例包含si、b、碱金属、al的硼硅酸盐玻璃粉末。接下来,作为填料,准备镁橄榄石粉末及石英粉末。然后,以成为硼硅酸盐玻璃粉末为72重量%、镁橄榄石粉末为4重量%、石英粉末为24重量%的比例的方式将它们湿式混合后,进行粉碎,由此制成非磁性材料。

[0263]

这里,利用以下的方法另外制作用于确认之后得到的层叠型线圈部件的试样1~5的基体的组成的基体试样。首先,以磁性材料为100体积%、非磁性材料为0体积%的比例进行称量。接下来,将这些称量物、作为有机粘合剂的聚乙烯醇缩丁醛系树脂、作为有机溶剂的乙醇及甲苯、以及增塑剂与psz介质一起放入球磨机并混合后,进行粉碎,由此制成浆料。然后,通过刮刀法将所得到的浆料成型为片状后,层叠并进行热压接合,由此制作生预制件。然后,对生预制件进行冲裁,在910℃下煅烧4小时,由此制作厚度为0.5mm且直径为10mm的圆板状的基体试样a。

[0264]

另外,除了将磁性材料及非磁性材料配合为表1所示的比例以外,与基体试样a同样地,制作基体试样b、基体试样c以及基体试样d。

[0265]

通过针对基体试样a、基体试样b、基体试样c以及基体试样d,利用电感耦合等离子体发射光谱法/电感耦合等离子体质谱法进行分析,确认了表1所示的组成。

[0266]

当观察表1所示的组成时,也可以说生片c及生片d相当于在将总重量设为100重量%时包含以sio2换算计30.0重量%以上的si的第三种生片。也可以说生片a及生片b相当于在将总重量设为100重量%时包含以sio2换算计25.0重量%以下的si的第四种生片。

[0267]

【表1】

[0268][0269]

<生片制作工序>

[0270]

使用与基体试样a相同组成的材料,制作构成上述生预制件的生片a。即,在之后制作的基体中,由生片a构成的区域具有与基体试样a相同的组成。

[0271]

同样,使用与基体试样b相同组成的材料制作生片b,使用与基体试样c相同组成的材料制作生片c,使用与基体试样d相同组成的材料制作生片d。在之后制作的基体中,由生片b构成的区域具有与基体试样b相同的组成,由生片c构成的区域具有与基体试样c相同的组成,由生片d构成的区域具有与基体试样d相同的组成。

[0272]

生片c及生片d相当于非磁性材料的体积相对于磁性材料及非磁性材料的合计体积的比例为60体积%以上的第一种生片。生片a及生片b相当于非磁性材料的体积相对于磁性材料及非磁性材料的合计体积的比例为50体积%以下的第二种生片。

[0273]

<导体图案形成工序>

[0274]

首先,通过对生片的规定部位进行激光照射,形成通孔。

[0275]

接下来,通过丝网印刷法,将ag糊剂填充到通孔并涂布于生片的表面。由此,对于生片,在通孔形成导通孔导体用导体图案,并且在表面上形成与导通孔导体用导体图案连接的线圈导体用导体图案。这样,制作在生片形成有线圈导体用导体图案以及导通孔导体用导体图案的线圈片。制作多张线圈片,对各线圈片形成与图8及图9所示的线圈导体相当的线圈导体用导体图案、和与图8及图9所示的导通孔导体相当的导通孔导体用导体图案。

[0276]

另外,通过利用丝网印刷法将ag糊剂填充到通孔,与线圈片不同地制作在生片形

成有导通孔导体用导体图案的导通片。也制作多张导通片,对各导通片形成与图8及图9所示的导通孔导体相当的导通孔导体用导体图案。

[0277]

<层叠体预制件制作工序>

[0278]

将线圈片及导通片以相当于图8及图9的顺序沿层叠方向层叠后,进行热压接合,由此制作层叠体预制件。

[0279]

<基体以及线圈制作工序>

[0280]

首先,通过利用切割机将层叠体预制件切断为规定的大小,制作分片化的芯片。

[0281]

接下来,将分片化的芯片在910℃下煅烧4小时。

[0282]

通过对分片化的芯片进行煅烧,线圈片及导通片的生片成为绝缘层。其结果,制作将多个绝缘层在层叠方向,这里为长度方向上层叠而形成的基体。

[0283]

通过对分片化的芯片进行煅烧,线圈片的线圈导体用导体图案以及导通孔导体用导体图案分别成为线圈导体以及导通孔导体。其结果,制造将多个线圈导体在长度方向上层叠,并且经由导通孔导体电连接而形成的线圈。

[0284]

由此,制作基体和设置在基体的内部的线圈。绝缘层的层叠方向和线圈的线圈轴的方向与作为安装面的基体的第一主面平行,这里,与长度方向平行。

[0285]

通过对分片化的芯片进行煅烧,导通片的导通孔导体用导体图案成为导通孔导体。其结果,制作将多个导通孔导体在长度方向上层叠且电连接而形成的第一连结导体及第二连结导体。第一连结导体从基体的第一端面露出。第二连结导体从基体的第二端面露出。

[0286]

然后,将基体与介质一起放入旋转滚筒机,通过对基体实施滚筒研磨,使角部及棱线部带有圆角。

[0287]

<外部电极形成工序>

[0288]

首先,使基体倾斜地浸渍于将包含ag及玻璃料的导电性糊剂拉伸为规定的厚度而成的层。接下来,通过对所得到的涂膜在810℃下进行烧结,形成从基体的第一端面的一部分遍及第一主面、第一侧面以及第二侧面的各面的一部分地延伸的基底电极。同样地,形成从基体的第二端面的一部分遍及第一主面、第一侧面以及第二侧面的各面的一部分地延伸的基底电极。各基底电极的厚度为5μm。

[0289]

然后,通过电镀,在各基底电极上依次形成ni镀层电极和sn镀层电极。

[0290]

这样,形成经由第一连结导体与线圈电连接的第一外部电极和经由第二连结导体与线圈电连接的第二外部电极。

[0291]

由此,制造层叠型线圈部件的试样1~5。层叠型线圈部件的试样1~5分别是长度方向上的尺寸为0.6mm,高度方向上的尺寸为0.3mm,宽度方向上的尺寸为0.3mm。

[0292]

在层叠型线圈部件的试样1~5中,在定义了与第一外部电极的基底电极中的存在于基体的第一主面上的部分的长度方向的末端在高度方向上重叠的第一基准位置时,将基体的第一基体部分的第一区域设为从第一基准位置朝向第二端面在长度方向上的尺寸(图11中的尺寸p1)为20μm的范围、与从第一基准位置朝向第一端面在长度方向上的尺寸(图11中的尺寸p2)为20μm的范围合在一起的范围。另外,在层叠型线圈部件的试样1~5中,在基体的第一基体部分,将第一区域以外作为第二区域。

[0293]

在层叠型线圈部件的试样1~5中,在定义了与第二外部电极的基底电极中的存在

于基体的第一主面上的部分的长度方向的末端在高度方向上重叠的第二基准位置时,将基体的第二基体部分的第一区域设为从第二基准位置朝向第一端面在长度方向上的尺寸(图12中的尺寸q1)为20μm的范围、与从第二基准位置朝向第二端面在长度方向上的尺寸(图12中的尺寸q2)为20μm的范围合在一起的范围。另外,在层叠型线圈部件的试样1~5中,在基体的第二基体部分,将第一区域以外作为第二区域。

[0294]

在层叠型线圈部件的试样1~5中,对于第一基体部分及第二基体部分,作为构成第一区域及第二区域的生片,使用表2所示的组合。其结果,在层叠型线圈部件的试样1~5中,对于第一基体部分及第二基体部分,第一区域中的非磁性相的体积相对于磁性相及非磁性相的合计体积的比例、和第二区域中的非磁性相的体积相对于磁性相及非磁性相的合计体积的比例如表2所示。另外,在层叠型线圈部件的试样1~5中,对于第一基体部分及第二基体部分,第一区域中的以sio2换算计的si的含量和第二区域中的以sio2换算计的si的含量如表2所示(在表2中记为“sio2含量”)。

[0295]

[评价]

[0296]

对层叠型线圈部件的试样1~5进行以下的评价。

[0297]

<基底电极以及镀层电极的位置>

[0298]

首先,在将层叠型线圈部件的试样以第一侧面向上侧露出的方式竖立成垂直的状态下,利用树脂密封周围。接下来,通过使用研磨机对层叠型线圈部件的试样实施研磨直到宽度方向的大致中央部,从而使沿着长度方向及高度方向的截面露出。然后,对于层叠型线圈部件的试样的露出截面,使用精工电子纳米科技公司制的聚焦离子束加工装置“smi3050r”实施聚焦离子束(fib)加工,由此获得观察用截面。

[0299]

然后,对于层叠型线圈部件的试样的观察用截面,使用扫描式电子显微镜(sem),拍摄第一外部电极的基底电极及镀层电极中的存在于基体的第一主面上的部分的照片。同样地,拍摄第二外部电极的基底电极及镀层电极中的存在于基体的第一主面上的部分的照片。然后,利用拍摄的照片确认基底电极及镀层电极的位置,在长度方向上,镀层电极的末端存在于比基底电极的末端靠基体的中心位置侧,另外,镀层电极的末端与基底电极的末端之间的长度方向上的距离如表2所示。

[0300]

【表2】

[0301][0302]

在表2中,对试样名标注了*的是本实用新型的范围外的比较例。

[0303]

如表2所示,在层叠型线圈部件的试样3、试样4以及试样5中,镀层电极的末端与基底电极的末端之间的长度方向上的距离为30μm以下。

[0304]

另一方面,在层叠型线圈部件的试样1及试样2中,镀层电极的末端与基底电极的末端之间的长度方向上的距离大于30μm。

[0305]

即,在层叠型线圈部件的试样3、试样4以及试样5中,与层叠型线圈部件的试样1及试样2相比,抑制了镀层电极沿着基体的第一主面相对于基底电极伸长。

[0306]

<透射系数s21>

[0307]

对于层叠型线圈部件的试样1、试样3以及试样4,一边使频率从30ghz变化到70gh,一边使用网络分析器测定根据透射信号相对于输入信号的功率之比求出的透射系数s21。

[0308]

图13是表示层叠型线圈部件的试样1、试样3以及试样4的透射系数s21的测定结果的图表。

[0309]

如图13所示,在层叠型线圈部件的试样3及试样4中,与层叠型线圈部件的试样1相比,40ghz、50ghz这样的高频带下的透射系数s21大,并且直到高频带的透射系数s21的偏差小。此外,虽然没有图示,但对于层叠型线圈部件的试样5,也与层叠型线圈部件的试样3及试样4同样,确认了高频带下的透射系数s21大,并且其偏差小。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1