一种低应力氧化物薄膜晶体管阵列基板的制作方法

1.本实用新型涉及显示设备领域,特别是一种低应力氧化物薄膜晶体管阵列基板。

背景技术:

2.随着消费市场需求的多样化,消费者对显示设备的要求也越来越高,对于大多数消费者来说,高分辨率及刷新率的显示器可以带来更流畅的游戏体验和视觉体验。为了实现更高规格的显示效果,对于驱动面板显示的膜晶体管tft器件性能便提出了更高的需求,因此,金属氧化物tft因其具有漏电流小、场效应迁移率高、区域均匀性大等优点而受到人们的青睐。

3.氧化物tft器件具备优秀的电学特性,但是对于器件的商业化制备也存在的诸多困难,例如既满足高效率低成本的同时,又确保商业化大面积生产时器件均一性、稳定性的需求。在氧化物tft电性以及器件稳定性易受到生产工艺中镀膜工艺产生的应力影响而导致电性变化甚至失效,为改善薄膜应力影响需搭配一定的加热工艺进行去应力退火以优化器件电性,但是由于现有阵列基板本身结构影响,镀膜产生应力仍无法避免。

4.ffs-lcd技术,全称为“边缘场开关技术”(fringe field switching,简称ffs)是液晶界为解决大尺寸、高清晰度桌面显示器和液晶电视应用而开发的广视角技术,也就是现在俗称的硬屏技术的一种。ffs技术通过同一平面内像素间电极产生边缘电场,使电极间以及电极正上方的取向液晶分子都能在(平行于基板)平面方向发生旋转转换,从而提高液晶层的透光效率。要实现ffs结构,需要两层透明导电层以及介于两层导电膜之间的中间绝缘层。

5.氮化硅、氧化硅薄膜是一种物理、化学性能均非常优秀的半导体薄膜,具有较高的介电常数、良好的耐热抗腐蚀性能、优异的机械性能、和较高的致密度等。相较于氧化硅,氮化硅的介电常数更大,更致密但是也更容易产生h+离子残留以及残余应力。因此,在显示面板领域中,氮化硅与氧化硅常搭配使用在绝缘层、表面钝化层、保护膜和功能层等。采用现有工艺方法制得的氮化硅和氧化硅薄膜一般都处于某种应力状态,应力的存在在宏观层面上将产生玻璃形变严重时将导致玻璃碎裂,在微观层面,薄膜残余应力引发氧化物薄膜晶体管器件薄膜材料能带跃迁,导致器件特性恶化,如阈值电压vth偏移,偏压稳定性恶化等。现有技术改善薄膜应力的主要方法为改变工艺参数(如温度、流量比例、射频功率、气压、气体流量比等),但是为达到缩减应力进行的基础工艺变更,改变了原有基板的结构平衡,且可能削弱薄膜的绝缘、钝化、密封等效果,而且还会直接影响到半导体器件的性能,从而制约了薄膜材料在实际生产中的应用空间。

技术实现要素:

6.本实用新型要解决的技术问题,在于提供一种低应力氧化物薄膜晶体管阵列基板,在所述第四绝缘层中的无效区开设凹槽区与隔断区,降低了绝缘层大面积成膜的残余应力问题,可以有效提高器件的阈值电压均匀性和面板机械测试可靠性。

7.本实用新型是这样实现的:一种低应力氧化物薄膜晶体管阵列基板,包括:

8.基板;

9.第一金属层,设于所述基板上;

10.第一绝缘层,设于所述第一金属层上;所述第一绝缘层还开设有第一通孔,从所述第一通孔露出所述第一金属层上表面;

11.有源层,设于所述第一绝缘层上;

12.第二金属层,设于所述有源层上,且通过所述第一通孔和所述第一金属层连接;

13.第二绝缘层,设于所述第二金属层上;

14.第三绝缘层,设于所述第二绝缘层上;所述第三绝缘层在tft的漏极区还开设有第二通孔;其中,所述第二通孔贯穿所述第二绝缘层,从所述第二通孔露出漏极区的所述第二金属层上表面;

15.第一ito层,设于所述第三绝缘层上,并通过所述第二通孔与tft的漏极区的第二金属层连接;

16.第四绝缘层,设于所述第一ito层上;所述第四绝缘层在tft的公共电极搭接区还开设有第三通孔,从所述第三通孔露出所述第二金属层上表面;所述第四绝缘层在tft上方的无效区还开设有凹槽区,并在tft与tft之间开设有隔断区;0<所述凹槽区所在位置的第四绝缘层的厚度<正常区位置的第四绝缘层的厚度;0<所述隔断区所在位置的第四绝缘层的厚度<正常区位置的第四绝缘层的厚度;

17.第二ito层,设于所述第三通孔处,并通过所述第三通孔和公共电极搭接区的所述第二金属层连接。

18.进一步地,所述凹槽区的底部和隔断区的底部分别设有垫层。

19.进一步地,所述第一金属层采用夹层式结构为:ti/al/ti、al/ti、al/mo、或mo/al/mo。

20.进一步地,所述第一绝缘层采用氮化硅、氧化硅、氮氧化硅、氧化钛、或氧化铝制备;

21.所述第二绝缘层、第四绝缘层和第一绝缘层采用相同的材料制备。

22.进一步地,所述有源层采用金属氧化物半导体材料制备。

23.进一步地,所述第三绝缘层采用有机高分子材料制备。

24.本实用新型具有如下优点:本实用新型提供一种低应力氧化物薄膜晶体管阵列基板,包括:基板;第一金属层;第一绝缘层;有源层;第二金属层;第二绝缘层;第三绝缘层;第四绝缘层,设于所述第一ito层上;所述第四绝缘层在tft的公共电极搭接区还开设有第三通孔,从所述第三通孔露出所述第二金属层上表面;所述第四绝缘层在tft上方的无效区还开设有凹槽区,并在tft与tft之间开设有隔断区;第二ito层,设于所述第三通孔处,并通过所述第三通孔和所述第二金属层连接。在所述第四绝缘层中的无效区开设凹槽区与隔断区,降低了绝缘层大面积成膜的残余应力问题,可以有效提高器件的阈值电压均匀性和面板机械测试可靠性。

附图说明

25.下面参照附图结合实施例对本实用新型作进一步的说明。

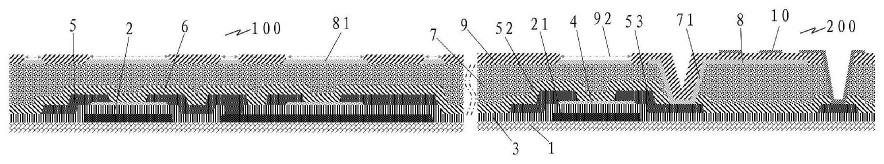

26.图1为本实用新型的一种低应力氧化物薄膜晶体管阵列基板的结构示意图。

27.图2为本实用新型的一种低应力氧化物薄膜晶体管阵列基板的制备方法的工艺流程图。

28.附图标记说明:

29.基板1;

30.第一金属层2,栅极21;

31.第一绝缘层3,第一通孔31;

32.有源层4;

33.第二金属层5,公共电极信号线51,源极52,漏极53;

34.第二绝缘层6;

35.第三绝缘层7,第二通孔71;

36.第一ito层8,垫层81;

37.第四绝缘层9,第三通孔91,凹槽区92,隔断区93;

38.第二ito层10;

39.驱动电路区100;

40.显示区200;

41.正常区300;

42.像素区400。

具体实施方式

43.在对实用新型的描述中,需要理解的是,指示方位或位置关系的描述为基于附图所示的方位或位置关系,仅是为了便于描述实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对实用新型保护范围的限制。

44.在实用新型的描述中,需要说明的是,除非另有明确的规定和限定,术语“设置”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在实用新型中的具体含义。

45.词语解释:本实用新型所说的应力指的是内应力。

46.正常区位置的第四绝缘层的厚度:即为第四绝缘层设计之初的厚度,或预设的厚度。在此基础上在第四绝缘层挖所述凹槽区和隔断区,因此,0≤所述凹槽区所在位置的第四绝缘层的厚度<正常区位置的第四绝缘层的厚度;0≤所述隔断区所在位置的第四绝缘层的厚度<正常区位置的第四绝缘层的厚度。

47.本实用新型的实用新型构思如下:

48.现有技术中,阵列基板易受到生产工艺中镀膜工艺产生的应力影响而导致电性变化甚至失效,因此,现有技术常采用退火的热处理工艺进行消除应力,但是因阵列基板各膜层的热膨胀系数不同,退火处理后,会在膜层之间产生新的内应力,而这就使得阵列基板的应力是否降低,在实际生产中无法保证。

49.因此,本实用新型在阵列基板结构中创新加入了凹槽区92或隔断区93,即在阵列基板的无效区将绝缘层挖薄或挖断,将阵列基板整体的应力进行碎片化,首先凹槽区92和隔断区93的应力降低了,其次将整块阵列基板的应力分化到各个更小的区块上,从而降低了绝缘层大面积成膜的残余应力问题,可以有效提高器件的阈值电压均匀性和面板机械测试可靠性。

50.请参阅图1和图2所示。

51.本实用新型的一种低应力氧化物薄膜晶体管阵列基板,包括:

52.基板1;

53.第一金属层2,作为驱动电路走线或者tft的栅极21,设于所述基板1 上;

54.第一绝缘层3,作为栅极绝缘层,设于所述第一金属层2上;所述第一绝缘层3还开设有第一通孔31,从所述第一通孔31露出所述第一金属层2 上表面;在具体实施中,可在阵列基板的驱动电路区100、扇形区、ic bonding 区等制备第一通孔,露出第一金属层2表面,起到第一金属层2与第二金属层5相连的效果。

55.有源层4,也称半导体层,设于所述第一绝缘层3上;

56.第二金属层5,设于所述有源层4上,且通过所述第一通孔31和所述第一金属层2连接;所述第二金属层5依据需求可以设计为触控感应信号线、公共电极信号线51、tft信号输入端源极52和漏极53、或面板数据线等。

57.第二绝缘层6,作为钝化层,以保护tft器件不受外界水氧入侵,设于所述第二金属层5上;

58.第三绝缘层7,作为平坦层,设于所述第二绝缘层6上;所述第三绝缘层7在tft的漏极区还开设有第二通孔71;其中,所述第二通孔71贯穿所述第二绝缘层7,从所述第二通孔71露出漏极区的所述第二金属层5上表面;所述第二通孔71作为钝化层/平坦层过孔。

59.第一ito层8,作为像素电极,设于所述第三绝缘层7上,并通过所述第二通孔71与tft的漏极区的第二金属层5连接。

60.第四绝缘层9,作为中间绝缘层,设于所述第一ito层8上;所述第四绝缘层9在tft的公共电极搭接区还开设有第三通孔91,作为平坦层过孔,从所述第三通孔91露出所述第二金属层5上表面;所述第四绝缘层9在tft 上方的无效区还开设有凹槽区92,并在tft与tft之间开设有隔断区93; 0≤所述凹槽区92所在位置的第四绝缘层的厚度<正常区300位置的第四绝缘层9的厚度;0≤所述隔断区93所在位置的第四绝缘层9的厚度<正常区 300位置的第四绝缘层9的厚度;在所述第四绝缘层9中的无效区开设凹槽区92与隔断区93,降低了绝缘层大面积成膜的残余应力问题,可以有效提高器件的阈值电压均匀性和面板机械测试可靠性。

61.第二ito层10,作为公共电极,设于所述第三通孔91处,并通过所述第三通孔91和公共电极搭接区的所述第二金属层5连接,即通过第三通孔91与公共电极信号线51相连。

62.所述凹槽区92所在位置的第四绝缘层9的厚度=0;即所述凹槽区92 将第四绝缘层9挖断;

63.所述隔断区93所在位置的第四绝缘层9的厚度=0;即所述隔断区93 将第四绝缘层9挖断。

64.所述凹槽区92的底部和隔断区93的底部分别设有垫层81,可采用ito 材料制造,

在具体实施中,如所述凹槽区92和隔断区93通过蚀刻制备,因此,通过垫层81可保护第三绝缘层7,避免在蚀刻所述凹槽区92和隔断区 93过程中被破坏。

65.所述第一金属层2采用铝、钼、钛、镍、铜、银、或钨中的一种或多种、或者合金制备;

66.所述第二金属层5和第一金属层2采用相同的材料制备。

67.所述第一金属层2采用夹层式结构为:ti/al/ti、al/ti、al/mo、或 mo/al/mo。

68.所述第一绝缘层3采用氮化硅、氧化硅、氮氧化硅、氧化钛、或氧化铝制备;

69.所述第二绝缘层6、第四绝缘层9和第一绝缘层3采用相同的材料制备。

70.所述有源层4采用金属氧化物半导体材料制备。

71.所述第三绝缘层7采用有机高分子材料制备,即第三绝缘层7作为有机平坦层。

72.本实用新型的一种低应力氧化物薄膜晶体管阵列基板的制备方法,所述的低应力氧化物薄膜晶体管阵列基板的制备方法包括以下步骤:

73.s1、在基板1之上成膜制作第一金属层2,作为驱动电路走线或者tft 的栅极21,第一金属层2可选用铝、钼、钛、镍、铜、银、钨等导电性优良金属一种或多种,或者合金;进一步地,第一金属层2还可以使用夹层式结构如ti/al/ti、al/ti、al/mo、mo/al/mo等,但不限于此;

74.s2、在所述第一金属层2上制作第一绝缘层3,作为栅极绝缘层,材料可选无机氧化物或者绝缘性质的化合物,如氮化硅、氧化硅、氮氧化硅、氧化钛、氧化铝等,可以是单层或多层;

75.s3、在所述第一绝缘层3之上制作有源层4,然后在所述第一绝缘层3 上制作第一通孔31,露出第一金属层2上表面;

76.有源层4可选材料为金属氧化物半导体材料,如zno、igzo、igzto、 itzo、pr-izo等。制备完有源层,即在图案化有源层4之后,进一步使用光罩在驱动电路区100、扇形区、ic bonding区等制备第一通孔31,露出第一金属层2表面,起到第一金属层2与第二金属层5相连的效果;

77.s4、在所述有源层4之上成膜制作第二金属层5,工艺以及材料选择同第一金属层2,第二金属层5依据需求可以设计为触控感应信号线、公共电极信号线51、tft信号输入端源极52和漏极53、或面板数据线等,所述第二金属层5通过所述第一通孔31与所述第一金属层2相连;

78.s5、在所述第二金属层5之上制作第二绝缘层6,作为钝化层以保护 tft器件不受外界水氧入侵,材料选择同第一绝缘层3,如氮化硅、氧化硅、氮氧化硅、氧化钛、氧化铝等,可以是单层或多层;

79.s6、在所述第二绝缘层6之上制备第三绝缘层7,作为平坦层,可采用有机高分子材料制备;

80.然后利用光罩在所述第三绝缘层7上对应tft的漏极区制备出第一穿孔,并在对应tft的公共电极搭接区制作出第二穿孔;

81.之后,在漏极区第一穿孔中制备钝化层通孔,从而形成第二通孔71,即第二通孔71分两步制得,并露出漏极区的所述第二金属层5上表面;

82.s7、利用透明导电材料ito制备第一ito层8,作为ffs显示系统中的像素电极,并通过第二通孔71与漏极区的第二金属层5相连,且在tft 上方的无效区、tft器件之间保留膜

层制作垫层81;

83.s8、在所述第一ito层8之上制备第四绝缘层9,作为中间绝缘层,材料选择同第一绝缘层3,氮化硅、氧化硅、氮氧化硅、氧化钛、氧化铝等,可以是单层或多层等,然后通过蚀刻工艺在第二穿孔的上方进一步制备出第三穿孔,第三穿孔向下穿过第二穿孔,露出第二金属层5上表面,形成第三通孔91,作为平坦层过孔,即第三通孔91也分两步制得;同时在所述垫层81的位置蚀刻出凹槽区92和隔断区93,通过垫层81保护第三绝缘层7,避免第三绝缘层7在蚀刻过程遭受破坏;

84.s9、利用ito透明导电材料制备第二ito层10,作为公共电极,并通过所述第三通孔91与第二金属层5相连,即通过第三通孔91与公共电极信号线51相连。

85.本实用新型的有益效果:通过在第四绝缘层9上开设所述凹槽区92和隔断区93,将第四绝缘层9整体的内应力进行碎片化,从而达到降低绝缘层大面积成膜的残余应力问题,可以有效提高器件的阈值电压均匀性和面板机械测试可靠性。

86.虽然以上描述了本实用新型的具体实施方式,但是熟悉本技术领域的技术人员应当理解,我们所描述的具体的实施例只是说明性的,而不是用于对本实用新型的范围的限定,熟悉本领域的技术人员在依照本实用新型的精神所作的等效的修饰以及变化,都应当涵盖在本实用新型的权利要求所保护的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1