高亮度半导体发光二极管芯片的制作方法

1.本实用新型涉及发光二极管技术领域,特别涉及一种高亮度半导体发光二极管芯片。

背景技术:

2.近年来,发光二极管芯片因其节能、环保、寿命长、响应速度快等优点而在白光照明、显示屏、紫外消毒等行业显现出巨大的优势。伴随着全球能源危机的到来,节能环保的理念深入人心。

3.随着发光二极管芯片的不断普及,人们对于发光二极管芯片的亮度的要求也越来越高。目前gan基发光二极管芯片的内量子效率的可提升空间已越来越小,因而一般通过提高光提取效率来提高发光二极管芯片的外量子效率,进而在整体上提高发光二极管芯片的亮度的方式非常有限。

4.另外,由于普通发光二极管芯片结构,其电极位于发光二极管芯片的出光面,因而电极的遮挡和吸收会影响发光二极管芯片的出光效率,进而降低发光二极管芯片的亮度。

技术实现要素:

5.基于此,本实用新型提供一种高亮度半导体发光二极管芯片,目的在于解决常规芯片因电极的遮挡和吸收会影响发光二极管芯片出光效率的问题,有利于提高发光二极管芯片的发光亮度。

6.一种高亮度半导体发光二极管芯片,包括衬底层组、焊盘层组、多个层叠于衬底层组上的外延导电层组以及用于连接相邻所述外延导电层组的隔离导电层组,其中:

7.所述外延导电层组包括依次层叠于衬底层组上的n型半导体层、有源层及p型半导体层,所述p型半导体层上设有电流阻挡层以及完全覆盖所述电流阻挡层的透明导电层,所述n型半导体层设有n电极,所述透明导电层上设有p电极,所述n电极的顶表面至少局部覆盖有第一金属反射膜层,所述p电极的顶表面至少局部覆盖有第二金属反射膜层;

8.所述隔离导电层组包括用于隔离相邻所述外延导电层组中所述n型半导体层的隔离层和设于所述隔离层上的导电连接层,所述导电连接层的一端与一相邻所述外延导电层组中的所述第一金属反射膜层电连接,所述导电连接层的另一端与另一相邻所述外延导电层组中的所述第二金属反射膜层电连接。

9.综上,根据上述的高亮度半导体发光二极管芯片,通过隔离导电层组中的隔离层将相邻外延导电层组中n型半导体层进行隔离,并通过隔离导电层组中的导电连接层将相邻外延导电层组中n型半导体层和p型半导体进行电性连接,从而形成耐高压的发光二极管芯片;同时,通过在所述p型半导体层上设置的电流阻挡层和完全覆盖电流阻挡层的透明导电层,能够减缓p电极的电流拥挤导致的过热现象,同时能引导光线从p电极的周边区域出射以降低p电极对光线的遮挡,提高光线的出射效率;另外,通过设置的第一金属反射膜层和第二金属反射膜层能够改善第一反射层在大角度下反射率降低的现象,进一步提高了发

光二极管的亮度,并且还有较好的电流扩散能力,进而提高了产品耐大电流能力。

10.进一步地,所述n型半导体和所述透明导电层上设有第一反射层,所述第一反射层上设有贯穿至所述n型半导体层的第一通孔以及贯穿至所述透明导电层的第二通孔,所述第一通孔和所述第二通孔均包括第一子通孔和与第一子通孔连通的第二子通孔,所述n电极设于所述第一通孔中的所述第一子通孔中,所述p电极设于所述第二通孔的第一子通孔中,所述第一金属反射膜层设于所述第一通孔的第二子通孔中,所述第二金属反射膜层设于所述第二通孔的所述第二子通孔中。

11.进一步地,所述第一子通孔的孔宽大于所述第二子通孔的孔宽。

12.进一步地,所述第二子通孔与所述第一子通孔的孔宽比为30%~60%,所述第一金属反射膜层和第二金属反射膜层所覆盖的所述第一反射层表面的覆盖面积分别与第一反射层的表面面积之比为70%~90%。

13.进一步地,所述隔离层包括层叠于所述衬底层组上的第二反射层,所述第一反射层和所述第二反射层均包括预设周期个交替层叠的第一反射子层和第二反射子层,所述第一反射层和第二反射层中的第一个子层为第一反射子层。

14.进一步地,所述第一反射子层的折射率大于第二反射子层的折射率。

15.进一步地,所述衬底层组包括衬底及设于所述衬底远离所述外延导电层组一面上的光学膜层,所述光学膜层包括多个交替层叠的第三反射子层和第四反射子层,所述光学膜层中首尾两个子层均为第三反射子层,所述第三反射子层的折射率小于所述第四反射子层的折射率。

16.进一步地,在所述有源层及所述p型半导体层之间还设有依次交替层叠的第一电子阻挡层和第二电子阻挡层。

17.进一步地,所述p型半导体层为p型gan层,所述第一电子阻挡层为gan 层,所述第二电子阻挡层为p型掺杂的algan层,所述p型掺杂的algan层的 al含量沿远离所述有源层的方向依次递减。

18.进一步地,所述导电连接层包括层叠于所述隔离层上的第三金属反射膜层,所述第三金属反射膜层、第一金属反射膜层及第二金属反射膜层均由mg、al、 ag及au中任一种材料制成。

附图说明

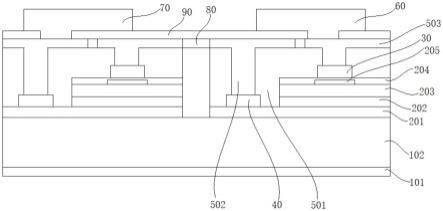

19.图1为本实用新型一实施例中的高亮度半导体发光二极管芯片的结构示意图。

20.主要元件符号说明:101、光学膜层,102、衬底,201、n型半导体层,202、有源层,203、p型半导体层,204、透明导电层,205、电流阻挡层,30、p电极,40、n电极,501、第一反射层,502、第一金属反射膜层,503、第二金属反射膜层,60、p焊盘,70、n焊盘,80、导电连接层,90、钝化层。

21.如下具体实施方式将结合上述附图进一步说明本实用新型。

具体实施方式

22.为了便于理解本实用新型,下面将参照相关附图对本实用新型进行更全面的描述。附图中给出了本实用新型的若干实施例。但是,本实用新型可以以许多不同的形式来实

现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本实用新型的公开内容更加透彻全面。

23.需要说明的是,当元件被称为“固设于”另一个元件,它可以直接在另一个元件上或者也可以存在居中的元件。当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中元件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

24.除非另有定义,本文所使用的所有的技术和科学术语与属于本实用新型的技术领域的技术人员通常理解的含义相同。本文中在本实用新型的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本实用新型。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

25.请参阅图1,所示为本发明一实施例中提出的高亮度半导体发光二极管芯片的结构示意图,该高亮度发光二极管芯片包括衬底层组、焊盘层组、多个层叠于衬底层组上的外延导电层组及用于连接相邻外延导电层组的隔离导电层组,其中:

26.外延导电层组包括依次层叠于衬底层组上的n型半导体层201、有源层202 及p型半导体层203,n型半导体层201上设有贯穿有源层202及p型半导体层 203的凹槽,设于p型半导体层203上的电流阻挡层205和完全覆盖电流阻挡层 205的透明导电层204,需要说明的是,在本实施例中,电流阻挡层205设于p 型半导体层203的顶表面,且p型半导体层203与透明导电层204共同将电流阻挡层205完全包裹,由于p电极30设于透明导电层204上,进而使得透明导电层204能够减缓p电极30的电流拥挤,避免p电极30附近出现过热现象,同时有利于避免p电极30对光线的遮挡。

27.为了改善传统技术中设置一层普通反射层难以适用于大角度的发光二极管芯片的情况,在n型半导体和透明导电层204上设有第一反射层501,第一反射层501上设有贯穿至n型半导体层201的第一通孔以及贯穿至透明导电层204 的第二通孔,第一通孔的底部设有与n型半导体层201电连接的n电极40,n 电极40上设有从第一通孔延伸至第一反射层501表面的第一金属反射膜层502,第二通孔的底部设有与透明导电层204电连接的p电极30,p电极30上设有从第二通孔延伸至第一反射层501表面的第二金属反射膜层503,第一金属反射膜层502和第二金属反射膜层503之间设有第一间隙。在本实施例中,通过增设第一金属反射膜层502以及第二金属发射膜层以与第一反射层501共同构成一新的具有高反射率的反射结构,以改善传统技术中采用一层金属反射层难以适用于大角度半导体发光二极管芯片的问题,极大地提高了入射光线的反射能力,进而有利于提高半导体发光二极管芯片的发光亮度。

28.进一步地,第一通孔和第二通孔均包括第一子通孔和与第一子通孔连通的第二子通孔,第一子通孔的孔宽大于第二子通孔的孔宽,在本实施例中,为了增强电极的牢固性,将n电极40设于第一通孔中的第一子通孔中,p电极30 设于第二通孔的第一子通孔中,第一金属反射膜层502设于第一通孔的第二子通孔中,第二金属反射膜层503设于第二通孔的第二子通孔中,且第二子通孔与第一子通孔的孔宽比为30%~60%,即通过将第二子通孔的孔宽设计成小于第一子通孔的孔宽,以便设于第一子通孔中的金属反射膜层能够对p电极30和n 电极40进行阻挡,从而提高电极的牢固性。除此之外,第一金属反射膜层502 和第二金属反射膜层503所覆盖的第一反射层501表面的覆盖面积分别与第一反射层501的表面面

积之比为70%~90%,以保证第一金属反射膜层502、第二金属反射膜层503分别与第一反射层501的重叠面积较大,从而使得该高亮度半导体发光二极管芯片具有良好的电流扩散能力,进而提高产品耐大电流能力。

29.为了提高产品的耐高压能力,隔离导电层组包括用于隔离相邻外延导电层组中n型半导体层201的隔离层和设于隔离层上的导电连接层80,导电连接层 80的一端与一相邻外延导电层组中的第一金属反射膜层502电连接,导电连接层80的另一端与另一相邻外延导电层组中的第二金属反射膜层503电连接,通过隔离导电层组中的隔离层将相邻外延导电层组中n型半导体层201进行隔离,并通过隔离导电层组中的导电连接层80将相邻外延导电层组中n型半导体层 201和p型半导体进行电性连接,从而形成耐高压的发光二极管芯片。

30.焊盘层组包括n焊盘70以及p焊盘60,n焊盘70与未和导电连接层80 电连接的第一金属反射膜层502电连接,p焊盘60与未和导电层电连接的第二金属反射膜层503电连接,通过设置n焊盘70和p焊盘60,能够形成良好的欧姆接触,以降低电压,延长发光二极管芯片的使用寿命,同时以p焊盘60为例,由于该高亮度发光二极管芯片中包括多个外延层组,因此,在本实施例中, p焊盘60只是与位于与自身同一侧的第二金属反射膜层503电连接,以防止发生短路的现象。

31.还需说明的是,焊盘层组还包括钝化层90,钝化层90的两端设有贯穿至第一金属反射膜层502的第三通孔和贯穿至第二金属反射膜层503的第四通孔,n 焊盘70和p焊盘60分别设于第三通孔和第四通孔中并延伸至钝化层90表面, p焊盘60和n焊盘70之间设有第二间隙,第二间隙大于第一间隙,在本实施例中,通过设置钝化层90,能够对发光二极管芯片进行保护,同时能够分隔p/n 电极40,防止杂质、水汽吸附表面而造成短路;另外第二间隙大于第一间隙,能够进一步避免短路现象,提高产品的安全性能。

32.由于在实际使用过程中,会有部分光线进入到隔离层中,为了提高进入到隔离层中的光线的出射率,该隔离层还包括层叠于衬底层组上的第二反射层,第一反射层501和第二反射层均包括预设周期个交替层叠的第一反射子层和第二反射子层,第一反射层501和第二反射层中第一个子层为第一反射子层,第一反射子层的折射率大于第二反射子层的折射率。具体地,共设置有21个第一反射子层和第二反射子层,通过将隔离层设置成两种不同折射率的反射子层,以提高光线的出射效率,从而进一步提高发光二极管芯片的发光亮度。

33.具体地,为进一步提高衬底102处光线的出光率,提高发光二极管的亮度,本实施例通过在衬底102远离外延导电层组一面上设置光学膜层101,光学膜层 101采用上述反射结构,能够提高光线的出现率。具体为,衬底层组包括衬底 102及设于衬底102远离外延导电层组一面上的光学膜层101,光学膜层101包括多个交替层叠的第三反射子层和第四反射子层,光学膜层101中首尾两个子层均为第三反射子层,第三反射子层的折射率小于第四反射子层的折射率。通过在衬底102表面设置由不同反射率的子层构成的光学膜层101,进而提高衬底102处光线的出光效率。

34.在有源层202及p型半导体层203之间还设有依次交替层叠的第一电子阻挡层和第二电子阻挡层,p型半导体层203为p型gan层,第一电子阻挡层为 gan层,第二电子阻挡层为p型掺杂的algan层且其al含量沿远离有源层202 的方向依次递减。在本实施例中,通过第一电子阻挡层降低第二电子阻挡层与量子垒的晶格失配,减少缺陷的产生,进而提高外延

长晶质量,通过al含量依次递减的第二电子阻挡层,能够阻挡多量子阱层的电子溢流,同时还减少对空穴的阻挡,进而提高电子和空穴的复合效率,从而提高发光效率。

35.优选地,导电连接层80包括层叠于隔离层上的第三金属反射膜层,第三金属反射膜层、第一金属反射膜层502及第二金属反射膜层503均由mg、al、ag 及au中任一种材料制成。

36.优选地,电流阻挡层205、钝化层90、第一反射子层、第三反射子层均为二氧化硅层,第二反射子层和第四反射子层均为五氧化三钛层,透明导电层204 为ito层。

37.综上,根据上述的高亮度半导体发光二极管芯片,通过新增第一金属反射膜层以及第二金属反射膜层,以与第一反射层形成新的高反射率结构,以适用于大角度下的发光二极管芯片,有效提高了半导体发光二极管芯片的发光亮度,具体为,首先在n型半导体层和透明导电层上铺设一层第一反射层,该第一反射层,而后,通过在第一反射层的基础上设置贯穿的第一通孔和第二通孔,以从第一通孔和第二通孔内分别生长第一金属反射膜层和第二金属反射膜层,同时该第一金属反射膜层和第二金属反射膜层均从通孔内延伸至第一反射层的表面,进而与第一反射层构成新的具有高反射率的反射结构,从而进一步增强大角度的入射光的反射能力,进而改善第一反射层在大角度下反射率下降的情况,以提高半导体发光二极管芯片的发光亮度。另外,通过在p型半导体层上设置的电流阻挡层和完全覆盖电流阻挡层的透明导电层,能够减缓p电极的电流拥挤导致的过热现象,同时能引导光线从p电极的周边区域出射以降低p电极对光线的遮挡,提高光线的出射效率,从而进一步提高发光效率,同时第一金属反射膜层与第二金属反射膜层之间设置成存在间隙,能够防止发生短路。

38.以上所述实施例仅表达了本实用新型的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本实用新型专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本实用新型构思的前提下,还可以做出若干变形和改进,这些都属于本实用新型的保护范围。因此,本实用新型专利的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1