一种多路信号保护型低电容TVS阵列陶瓷贴片式封装外壳的制作方法

一种多路信号保护型低电容tvs阵列陶瓷贴片式封装外壳

技术领域

1.本实用新型涉及一种多路信号保护型低电容tvs阵列陶瓷贴片式封装外壳及其封装方法。

背景技术:

2.目前,大功率tvs管多为单管封装,且结电容较大,在一般的设计中经常会用到多个单管器件进行叠加使用,在满足产品电性能指标要求下,产品需要多个单管器件叠加使用,这将导致pcb板面面积增大、安装工艺步骤多,兼容性低。为了解决这些问题,我们着手开发了多路集成阵列产品,为解决这类产品的封装难题我们开发一种多路信号保护型低电容tvs阵列陶瓷贴片式封装结构及封装方法,直接从封装接解决组装难题。以满足高可靠高性能阵列tvs管封装的应用需求。

3.本实用新型涉及一种高功率密度、高可靠性二极管阵列的小型陶瓷外壳零件。本系列陶瓷零件设计主要用于高可靠性低电容瞬态保护二极管阵列的金属陶瓷贴片封装外壳零件。是模拟混合集成电路小型化、集成化陶瓷封装类零件的典型代表,可满足电子元器件在科研及生产上对该外形封装产品的高可靠性、高集成度要求和技术要求。

技术实现要素:

4.为解决上述技术问题,本实用新型提供了一种多路信号保护型低结电容tvs阵列产品的封装结构。根据该类电子元器件的性能及产品对热和电流的传导要求,设计的一种能同时对多路信号进行保护的阵列产品,它具有功率密度高、寄生容抗/感抗/阻抗小、可同时保护3路信号线等特点(单路承受功率可达3000w)。能很好的满足科研和生产中对该类型外形产品的高可靠性要求和技术要求。

5.本实用新型通过以下技术方案得以实现。

6.本实用新型提供的一种多路信号保护型低电容tvs阵列陶瓷贴片式封装外壳;包括陶瓷基座、封口环、盖板;

7.陶瓷基座,陶瓷基座的上端面加工有至少一个热沉区和至少一个键合区,陶瓷基座的下端面设置有至少两个电极,热沉区和键合区和电极之间加工有通孔;

8.封口环,封口环和陶瓷基座的截面形状相同;

9.盖板,盖板的一端面加工有凸起,凸起的形状和大小与封口环的内圈相同;

10.所述热沉区和键合区的底部通过金属层覆盖,所述通孔内凝固有导电柱,导电柱将电极和金属层分别连接;

11.热沉区和键合区为在芯片a上加工凹槽或凸起。

12.所述热沉区包括第一热沉区、第二热沉区、第三热沉区、第四热沉区、第五热沉区,第五热沉区加工在芯片a中心,第一热沉区、第二热沉区、第三热沉区、第四热沉区均匀环绕在第五热沉区周围。

13.所述第五热沉区相对两端旁分别加工有第一键合区和第二键合区。

14.所述电极包括第一电极、第二电极、第三电极、第四电极,第一电极通过两根导电柱分别与第一热沉区和第二热沉区上的金属层连接,第二电极通过两根导电柱分别与第三热沉区和第四热沉区上的金属层连接,第三电极通过两根导电柱分别与第一键合区和第二键合区上的金属层连接,第四电极通过导电柱与第二键合区上金属层连接。

15.所述金属层包括金属块,金属块和陶瓷基座加工有钨或钼锰镀层,金属块表面为金镀层,金镀层和金属块之间还有镍或镍钴或镍磷镀层。

16.所述热沉区横截面的形状和大小与芯片横截面的形状大小相同。

17.本实用新型的有益效果在于:通过在陶瓷基座内开槽或凸起作为热沉区和键合区,合理布局芯片粘接区和键合线区位置,从而降低其后部工艺封装难度;使芯片及键合区底部采用整体金属镀金和局部镀镍工艺,整体金属镀金和局部镀镍工艺。

附图说明

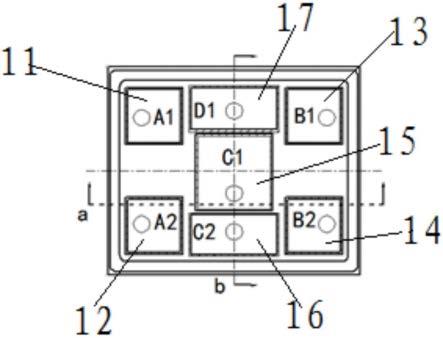

18.图1是本实用新型的陶瓷基座结构示意图;

19.图2是本实用新型图1的a向截面图;

20.图3是本实用新型图1的b向截面图;

21.图4是本实用新型的陶瓷基座底部结构示意图;

22.图5是本实用新型的管芯安装结构示意图;

23.图6是本实用新型的盖板结构示意图;

24.图7是本实用新型的管芯内部连接结构示意图;

25.图8是本实用新型的实施例2陶瓷基座结构示意图;

26.图9是本实用新型图8的截面结构示意图;

27.图10是本实用新型实施例2的陶瓷基座结构示意图;

28.图中:1-陶瓷基座,2-通孔,3-封口环,4-热沉区,5-盖板,6-芯片a,7-焊片,8-铜片,9-芯片b,10-钨铜压块,11-第一热沉区,12-第二热沉区,13-第三热沉区,14-第四热沉区,15-第五热沉区,16-第一键合区,17-第二键合区,18-第一电极,19-第二电极,20-第三电极,21-第四电极。

具体实施方式

29.下面进一步描述本实用新型的技术方案,但要求保护的范围并不局限于所述。

30.本专利从cbcc封装着手,设计了两款新型多通道的扁平金属陶瓷封装结构,设计中合理布局芯片粘接区和键合线区位置,从而降低其后部工艺封装难度,提高产品的稳定性和可靠性。

31.根据电路安装要求,陶瓷陶瓷基座除4个电极块外、其余部位均为陶瓷,同时采用多层陶瓷件与边框3烧焊结在一起,保证器件的绝缘性气密性要求。

32.热沉区底部采用整体金属镀金和局部镀镍工艺,键合区镀镍,解决了陶瓷零件的热和瞬态大电流的传导问题以及金铝键合问题,提高了该类型封装的高功率密度和集成度。

33.实施例1:如图8~10所示为一种cbcc封装,陶瓷基座的尺寸为外形尺寸为9.1mm

×

9.4mm

×

4.4mm,和封口环及盖板形成的封闭空腔尺寸为7.2mm

×

7.9mm;

34.如图10所示,热沉区和键合区为陶瓷基座上的凸台,第一键合区和第二键合区分别加工在陶瓷基座两端边缘,第一热热沉区11、第二热热沉区12、第三热热沉区13、第四热热沉区14分别在陶瓷基座的的两侧边缘,第五热沉区加工在陶瓷基座中心;

35.陶瓷基座上加工有通孔将键合区和热沉区分别和陶瓷基座底部联通,通孔的半径为0.5mm,1个方形通孔,尺寸为3.6mm

×

0.8mm,通孔填充材料均为tu1(无氧铜);在热沉区底部电镀一层厚度在在5um的钨或钼锰,将金属块安放在镀层上,然后在金属块上电镀厚度在1.39um的镍、镍钴或者镍磷,金属块表层电镀厚度在1.3um,纯度≥99.9%的金。键合区的镀层材料和结构和热沉区相同,但其表层材料金属镍、镍钴或者镍磷的厚度在1.3um,金属块与陶瓷之间的材料金属钨或钼锰的厚度在在5um。

36.实施例2:如图1~4所示为一种cbcc封装,陶瓷基座的尺寸为外形尺寸为15.1mm

×

1.5mm

×

4.7mm,和封口环及盖板形成的封闭空腔尺寸为13.7mm

×

10.9mm;

37.如图1所示,热沉区和键合区为陶瓷基座上的凹槽台,第一热热沉区11、第二热热沉区12、第三热热沉区13、第四热热沉区14分别加工在陶瓷基座的四角上,第五热沉区加工在陶瓷基座中心,第一键合区和第二键合区分别加工在陶瓷基座两侧边缘;

38.陶瓷基座上加工有通孔将键合区和热沉区分别和陶瓷基座底部联通,通孔的半径为0.5mm,1个方形通孔,尺寸为3.6mm

×

0.8mm,通孔填充材料均为tu1(无氧铜);在热沉区底部电镀一层厚度在在30um的钨或钼锰,将金属块安放在镀层上,然后在金属块上电镀厚度在8.9um的镍、镍钴或者镍磷,金属块表层电镀厚度在5.7um,纯度≥99.9%的金。键合区的镀层材料和结构和热沉区相同,但其表层材料金属镍、镍钴或者镍磷的厚度在8.9um,金属块与陶瓷之间的材料金属钨或钼锰的厚度在在30um。

39.实施例3:多路信号保护型低电容tvs阵列陶瓷贴片式封装陶瓷基座产品的封装方法,以大功率低电容tvs阵列器件模块的封装方案为例,具体步骤如下:

40.(1)将陶瓷基座进行清洗:

41.①

先将陶瓷基座进行湿法清洗,使用真空或氮气烘烤:首先将封装陶瓷基座用丙酮浸泡10分钟,然后再用超声波低频清洗3分钟,再用常规水冲洗5分钟,再用离子水冲洗10分钟,最后用酒精进行脱水处理。完成用60℃的氮气烘箱进行烘烤。

42.②

使用前再将陶瓷基座进行氩等离子清洗;具体方案如下:氩等离子清洗采用功率优选设定为100w,氩流量为≯50sccm,清洗时间优选设定为180s,每次陶瓷基座清洗后需在24小时内用完。

43.(2)准备待封装的功率芯片并选取焊接材料为高温焊片;

44.(3)将芯片按照图5所示进行安装,首先在每个焊接区线安装焊片7,其次再将芯片a6和芯片b9,芯片正面朝上进行安装,按照位置要求放置在每个焊接区的焊片之上,在每个独立区域中底层芯片a6和芯片b9上安装上层焊片7,再在焊片上面安装铜片8,然后再在铜片上放置钨铜压块10,最后将组装完成的模具整体放置在真空烧结炉中进行高温烧结;在氮气条件下以设定的升温速度v1升温至预设的温度t1保温t1时间后;抽真空,抽真空t1时间后再次充入氮气,设定升温速度v2升温至预设温度t2,保温t3时间后;再次抽真空,抽真空t4时间后,设定升温速度v3升温至预设温度t3(最高温度),保温t5时间后;开始降温,设定降温速度v4,当温度降至熔点以下后开始充入氮气,最后随炉冷却,去除压块后便完成器件烧结。(升温速度关系,v1>v2>v3>v4)。

45.(4)将烧结后的模块,置于键合机上通过互连材料进行各个上层芯片与陶瓷基座内表面电极及图形成进行引线键合,得到电性能互连的模块;

46.(5)将完成步骤(5)电性能互连的器件,放入平行缝焊设备,在陶瓷基座安装盖板(16),进行陶瓷基座封口环(3)与盖板(5)封接,完成多路信号保护型低电容tvs阵列模块的模组封装。

47.芯片均为硅基芯片,背面金属化层可为au,芯片尺寸最大为4.0mm

×

4.0mm,最小尺寸为2.8mm

×

2.8mm,。通过结构设计实现错层结构封装,为每颗芯片形成一个独立的安装室,使得组装工艺变得简单。

48.底层芯片与陶瓷基座采用底层焊料连接,大芯片烧结所用焊料为ausn或pbsnag成分预成型固态焊料片。

49.底层大芯片与陶瓷基座连接采用的焊料,具体为:采用ausn或pbsnag固态焊片共晶焊接温度范围为320℃~350℃,焊接时间为30s~150s,焊接氛围为真空。

50.通过零件自身的分立结构进行焊片与芯片定位,芯片、焊片的安装采用粘片机进行。

51.陶瓷基座与盖板通过平行缝焊连接陶瓷基座材料为陶瓷陶瓷基座,盖板为金属盖板(成分为4j42或4j29),陶瓷基座与盖板封接为气密性封接,封接后内部水汽含量≤5000ppm,封接后漏率≤1

×

10-3pa

·

cm3/s。

52.功率芯片与陶瓷基座采用金属线连接如图7所示,a-a1-a2、b-b1-b2、c-c1-c2、d-d1,金属线材料为硅铝丝,丝径≥380μm,数量12颗。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1