采用填充金属用于基于ETS的基板中的嵌入式金属迹线以降低信号路径阻抗的集成电路(IC)封装件和相关制造方法与流程

背景技术:

1、i.技术领域

2、本公开的领域涉及集成电路(ic)封装件,并且更具体地涉及对封装基板的设计和制造,该封装基板支持至ic封装件中的半导体管芯的信号路由。

3、ii.背景技术

4、集成电路(ic)是电子设备的基石。ic被封装在ic封装件(也被称为“半导体封装件”或“芯片封装件”)中。ic封装件包括作为ic的一个或多个半导体管芯(“这些管芯”或“管芯”),该一个或多个半导体管芯被安装在封装基板上并且电耦合到封装基板以提供对管芯的物理支持和电接口。封装基板包括一个或多个金属化层,该一个或多个金属化层包括具有垂直互连通路(过孔)的金属互连件(例如,金属迹线、金属线),这些垂直互连通路将这些金属互连件一起耦合在邻近的金属化层之间,以在管芯之间提供电接口。管芯被电连接到封装基板的顶层或外层中所暴露的金属互连件,以将管芯电耦合到该封装基板的金属互连件。封装基板包括耦合到外部金属互连件(例如,焊料凸块)的外部金属化层,以在ic封装件中的管芯之间提供外部接口,该外部接口用于将ic封装件安装在电路板上以将管芯与其他电路系统连接。封装基板可包括邻近管芯的嵌入式迹线基板(ets)(或包括薄ets金属化层)以促进较高密度凸块/焊点以用于将管芯耦合到封装基板。

5、一些ic封装件被称为“混合”ic封装件,其中包括用于不同目的或应用的具有相应管芯的多个管芯封装件。例如,混合ic封装件可以是应用管芯,诸如通信调制解调器或处理器(包括系统)。混合ic封装件还可包括例如一个或多个存储器管芯以提供存储器以支持由应用管芯进行的数据存储和访问。多个管芯可设置在单个管芯层中,并且在ic封装件中的封装基板上在水平方向上彼此邻近设置。该多个管芯还可被提供在其自身的相应管芯封装件中,这些管芯封装件在整个ic封装件内彼此堆叠,其间设置有中介层,以支持在该封装件中的堆叠式管芯之间提供电连接。可能需要堆叠式管芯封装件来减小封装件的横截面积。在堆叠式管芯ic封装件中,直接支持在封装基板上的第一底部管芯通过管芯互连件电耦合到封装基板的上部金属化层中的金属互连件。不直接邻近ic封装件中的封装基板的其他堆叠式管芯可通过引线接合和/或中间中介层电耦合到封装基板,以在该多个堆叠式管芯之间提供管芯到管芯(d2d)连接。

6、ic封装件中的管芯可包括高速输入/输出(hsio)电路(例如,动态随机存取存储器(dram)),其中信号性能(即,高信令速度和低信号损耗)对于预期操作而言是至关重要的。例如,如果ic封装件中的管芯是存储器管芯,则ic封装件可能需要支持高速存储器访问时间以缓解存储器访问延迟。路由到ic封装件中的管芯的信号的速度和损耗与信号路径长度成比例地受到负面影响。将接口电路设置在管芯的边缘附近以减小管芯与ic封装件的封装路由结构(例如,封装基板、中介层)之间的信号路径长度可能是有利的。例如,在堆叠式管芯ic封装件中,如果接口电路的位置更靠近管芯边缘,则中介层与管芯对准以支持较短信号路由路径。然而,将接口电路放置在管芯的边缘附近还可增加接口电路与耦合到管芯中的接口电路的其他管芯上电路之间的信号路径长度。因此,虽然将接口电路在管芯中更靠近管芯的中心放置以减小管芯内的信号路径长度可能是更“管芯友好”的,但这样可能会以接口电路与ic封装件的路由结构之间的较长信号路径为代价。

技术实现思路

1、本文中所公开的各方面包括集成电路(ic)封装件,其采用填充金属用于基于ets的基板中的嵌入式金属迹线以降低信号路径阻抗。还公开了相关制造方法。在示例性方面,提供了包括具有ets金属化层的基于ets的封装基板的ic封装件,ets金属化层是包括嵌入式金属迹线的金属化层。ets金属化层促成提供具有减小的线/间距比(l/s)的更高密度的凸块/焊点,以用于将半导体管芯(“管芯”)电耦合到封装基板以进行信号路由。金属嵌入式迹线形成在ets金属化层中,这些金属嵌入式迹线被电耦合到封装基板的其他金属化层中的管芯和金属互连件,以提供用于信号路由的信号路由路径。与封装基板中其他类型的金属化层中形成的其他类型的金属互连件相比,由ets金属化层得到的可用的降低的l/s比减少了嵌入式金属迹线的金属表面积,从而增加了电阻和阻抗。由于将接口电路更管芯友好地、中心放置在管芯中,从而导致ic封装件中的信号路由路径的长度较长,因此包括嵌入式金属迹线的信号路由路径也可能增加阻抗。信号路由路径阻抗的增加通过降低信令速度和增加信号损耗来成比例地降低信号性能。

2、为了缓解或抵消管芯中的电路系统与封装基板之间的信号路径中的阻抗增加,本文中所公开的示例性方面包括提供耦合到封装基板的ets金属化层中的嵌入式金属迹线的填充金属互连件。以此方式,作为管芯的信号/接地信号路径的一部分的ets金属化层的嵌入式金属迹线的金属表面积增加。增加耦合到管芯的信号/接地信号路径的嵌入式金属迹线的金属表面积增加了此类信号/接地信号路径的电容。因为阻抗与电容成反比,所以增加信号/接地信号路径的电容降低了信号/接地信号路径的阻抗。减小封装基板和管芯偏移之间的信号/接地信号路径的阻抗以缓解阻抗的增加可以允许在管芯中提供更“管芯友好”的接口电路系统的布置。接口电路系统在管芯中的“管芯友好”放置一般意味着将接口电路系统更靠近管芯中心而不朝向管芯边缘来放置,以减少接口电路系统和其他管芯上电路之间的信号路径长度。

3、填充金属互连件可以在ic封装件中的垂直方向上添加到嵌入式金属迹线的顶部,以使得填充金属互连件被设置在ets金属化层和管芯之间。这将避免必须提供在水平方向上更宽的ets金属化层和封装基板,并且因此增加ic封装件宽度以容适嵌入式金属迹线的增加的金属表面积。在此场景中,作为示例,填充金属互连件可被添加在单独的层中,诸如在制造封装基板时在垂直方向上设置在ets金属化层上的阻焊层,作为非限制性示例。阻焊层的未蚀刻部分可以驻留在ic封装件中,作为其制造的一部分,以使得在阻焊层中放置金属添加物不对增加ic封装件的整体高度作出贡献。另选地,金属添加物可被耦合到ets互连件之下的嵌入式金属迹线,以使得ets嵌入式金属迹线仍在ets金属化层和管芯之间形成金属互连件。在此场景中,填充金属互连件可被添加到ets金属化层中的其ets金属层之下的绝缘层中,在该绝缘层中形成嵌入式金属迹线,和/或除了或代替将嵌入式金属迹线耦合到封装基板中邻近的下方的金属化层中的金属互连件的垂直互连通路(过孔)。在此实例中,这些过孔的横截面积可被扩大,以增加嵌入式金属迹线的金属表面积。作为一个非限制性示例,为嵌入式金属迹线提供的填充金属互连件可以包括附加金属镀层,诸如铜镀层。填充金属互连件也可以是在ets金属化层的邻近层中形成的附加金属迹线或线,该ets金属化层被耦合到嵌入式金属迹线。

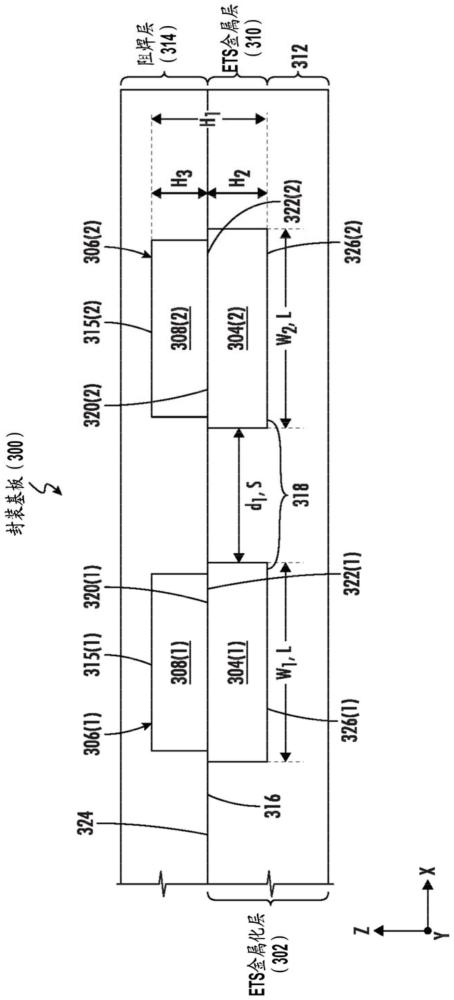

4、就此而言,在一个示例性方面,提供了一种ic封装件。该ic封装件包括封装基板。封装基板包括多个金属化层。该多个金属化层包括第一金属化层和第二金属化层,该第一金属化层包括一个或多个第一金属互连件。该第二金属化层包括第二金属层和嵌入在第二金属层中的一个或多个金属迹线。封装基板还包括邻近第二金属层设置的第三层,该第三层包括一个或多个第三金属互连件,该一个或多个金属互连件各自耦合到一个或多个金属迹线之中的金属迹线。

5、在另一示例性方面,提供了一种制造ic封装件的方法。该方法包括形成封装基板,其包括形成多个金属化层。形成多个金属化层包括形成包括一个或多个第一金属互连件的第一金属化层,以及形成第二金属化层。该第二金属化层包括第二金属层和嵌入在第二金属层中的一个或多个金属迹线。该方法还包括将该一个或多个金属迹线中的每个金属迹线耦合到该一个或多个金属互连件之中的第一金属互连件。该方法还包括形成邻近第二金属层设置的第三层,该第三层包括一个或多个第三金属互连件。该方法还包括将该一个或多个金属互连件中的每个金属互连件耦合到该一个或多个金属迹线之中的金属迹线。

- 还没有人留言评论。精彩留言会获得点赞!