一种环栅晶体管及其制造方法

本发明涉及半导体,尤其涉及一种环栅晶体管及其制造方法。

背景技术:

1、环栅晶体管相对于平面晶体管和鳍式场效应晶体管具有较高的栅控能力等优势,可以提高包括该环栅晶体管的半导体器件的工作性能。

2、但是,在一些特殊的应用场景中,需要环栅晶体管具有非对称的开关电流(例如:磁性随机存储器包括的访问晶体管)。而采用常规环栅晶体管的制造工艺形成的现有的环栅晶体管通常具有对称性的开关电流,难以满足上述应用要求。

技术实现思路

1、本发明的目的在于提供一种环栅晶体管及其制造方法,以使得环栅晶体管具有非对称的开关电流,满足相应应用场景的工作要求。

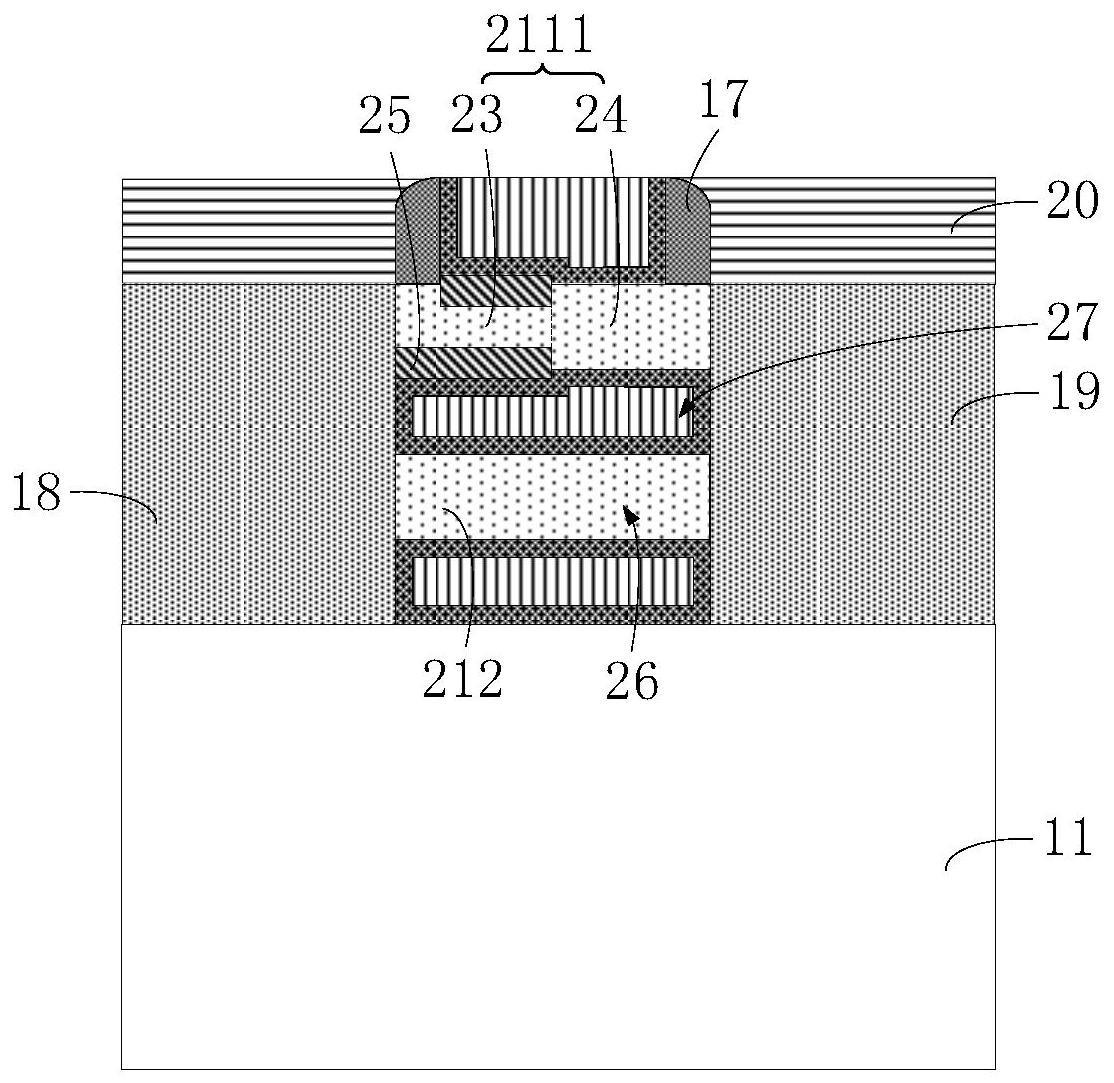

2、为了实现上述目的,本发明提供了一种环栅晶体管,该环栅晶体管包括:第一有源区、第二有源区、沟道和栅堆叠结构。沟道位于第一有源区和第二有源区之间、且分别与第一有源区和第二有源区接触。栅堆叠结构环绕在沟道的外周。其中,沟道包括至少一个第一纳米结构。沿第一有源区至第二有源区的方向,每个第一纳米结构被栅堆叠结构覆盖的部分均具有第一区域和第二区域。同一第一纳米结构中,第一区域的宽度和厚度分别小于第二区域的宽度和厚度。

3、与现有技术相比,本发明提供的环栅晶体管中,位于第一有源区和第二有源区之间的沟道,其包括至少一个第一纳米结构。沿第一有源区至第二有源区的方向,每个第一纳米结构被栅堆叠结构覆盖的部分均具有第一区域和第二区域。同一第一纳米结构中,第一区域的宽度和厚度分别小于第二区域的宽度和厚度。此时,同一第一纳米结构中,第一区域的横截面积小于第二区域的横截面积。基于此,因电阻与横截面积成反比,故每个第一纳米结构位于第一区域的部分的电阻大于自身位于第二区域的部分的电阻。并且,当第一区域的横截面积小于第二区域的横截面积时,栅堆叠结构对每个第一纳米结构位于第一区域的部分的控制能力大于其对每个第一纳米结构位于第二区域的部分的控制能力。在此情况下,在每个第一纳米结构位于第一区域和第二区域的电阻不同、且栅堆叠结构对每个第一纳米结构位于第一区域和第二区域的控制能力不同的情况下,环栅晶体管在导通后具有非对称的开关电流,以满足相应应用场景的工作要求。

4、本发明还提供了一种环栅晶体管的制造方法,该环栅晶体管的制造方法包括:

5、提供一半导体基底。

6、在半导体基底上形成第一有源区、第二有源区和沟道。沟道位于第一有源区和第二有源区之间、且分别与第一有源区和第二有源区接触。

7、形成环绕在沟道外周的栅堆叠结构。其中,沟道包括至少一个第一纳米结构。沿第一有源区至第二有源区的方向,每个第一纳米结构被栅堆叠结构覆盖的部分均具有第一区域和第二区域。同一第一纳米结构中,第一区域的宽度和厚度分别小于第二区域的宽度和厚度。

8、与现有技术相比,本发明提供的环栅晶体管的制造方法的有益效果可以参考前文所述的环栅晶体管的有益效果分析,此处不再赘述。

技术特征:

1.一种环栅晶体管,其特征在于,包括:第一有源区、第二有源区、沟道和栅堆叠结构;所述沟道位于所述第一有源区和所述第二有源区之间、且分别与所述第一有源区和所述第二有源区接触;所述栅堆叠结构环绕在所述沟道的外周;其中,

2.根据权利要求1所述的环栅晶体管,其特征在于,每个所述第一纳米结构具有的所述第一区域的宽度与自身具有的所述第二区域的宽度的比值范围为:1:2至4:5;和/或,

3.根据权利要求1所述的环栅晶体管,其特征在于,所述环栅晶体管还包括形成在所述栅堆叠结构与每个所述第一纳米结构具有的第一区域之间的氧化层。

4.根据权利要求3所述的环栅晶体管,其特征在于,所述氧化层的外表面与相应所述第一纳米结构具有的所述第二区域的外表面平齐。

5.根据权利要求1所述的环栅晶体管,其特征在于,所述沟道包括多个第一纳米结构;多个所述第一纳米结构沿自身的厚度方向间隔设置。

6.根据权利要求5所述的环栅晶体管,其特征在于,沿所述第一纳米结构的长度方向,不同所述第一纳米结构具有的第一区域首尾平齐;和/或,

7.根据权利要求1所述的环栅晶体管,其特征在于,所述沟道还包括至少一个第二纳米结构;所述至少一个第二纳米结构与所述至少一个第一纳米结构间隔设置;所述至少一个第二纳米结构的材料不同于所述至少一个第一纳米结构的材料;沿所述栅堆叠结构的长度方向,每个所述第二纳米结构各区域的宽度相同、且每个所述第二纳米结构各区域的厚度相同。

8.一种环栅晶体管的制造方法,其特征在于,包括:

9.根据权利要求8所述的环栅晶体管的制造方法,其特征在于,在所述半导体基底上形成所述沟道包括:

10.根据权利要求9所述的环栅晶体管的制造方法,其特征在于,所述沟道预形成结构包括多个所述第一沟道部,多个所述第一沟道部沿所述半导体基底的厚度方向间隔设置。

11.根据权利要求9所述的环栅晶体管的制造方法,其特征在于,所述在掩膜层的掩膜作用下,对每个所述第一沟道部对应所述第一区域的部分进行减薄处理,包括:

12.根据权利要求11所述的环栅晶体管的制造方法,其特征在于,所述在所述掩膜层的掩膜作用下,采用氧化工艺对每个所述第一沟道部对应所述第一区域的部分进行减薄处理后,所述形成环绕在所述沟道外周的栅堆叠结构前,所述环栅晶体管的制造方法还包括:

13.根据权利要求9所述的环栅晶体管的制造方法,其特征在于,在所述掩膜层的掩膜作用下,采用原子层刻蚀工艺对每个所述第一沟道部对应所述第一区域的部分进行减薄处理,以形成所述至少一个第一纳米结构。

14.根据权利要求9所述的环栅晶体管的制造方法,其特征在于,所述提供一半导体基底后,所述在所述半导体基底上形成沟道预形成结构前,所述环栅晶体管的制造方法还包括:

15.根据权利要求14所述的环栅晶体管的制造方法,其特征在于,采用制造所述牺牲栅的光刻掩膜版形成所述掩膜层。

16.根据权利要求9~15任一项所述的环栅晶体管的制造方法,其特征在于,所述沟道预形成结构还包括至少一个第二纳米结构;所述至少一个第二纳米结构与所述至少一个第一沟道部间隔设置,每个所述第二纳米结构与所述半导体基底间隔设置;所述至少一个第二纳米结构的材料不同于所述至少一个第一沟道部的材料;沿所述栅堆叠结构的长度方向,每个所述第二纳米结构各区域的宽度相同、且每个所述第二纳米结构各区域的厚度相同。

技术总结

本发明公开了一种环栅晶体管及其制造方法,涉及半导体技术领域,以使得环栅晶体管具有非对称的开关电流,满足相应应用场景的工作要求。所述环栅晶体管包括:第一有源区、第二有源区、沟道和栅堆叠结构。沟道位于第一有源区和第二有源区之间、且分别与第一有源区和第二有源区接触。栅堆叠结构环绕在沟道的外周。其中,沟道包括至少一个第一纳米结构。沿第一有源区至第二有源区的方向,每个第一纳米结构被栅堆叠结构覆盖的部分均具有第一区域和第二区域。同一第一纳米结构中,第一区域的宽度和厚度分别小于第二区域的宽度和厚度。

技术研发人员:李永亮,张佳熠,罗军,王文武

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!