半导体装置的制作方法

本发明的实施方式涉及一种半导体装置。

背景技术:

1、一直以来,已知通过针对微细化的对策,将nmos(n-channel metal-oxidesemiconductor,n型金属氧化物半导体)与pmos(p-channel metal-oxide semiconductor,p型金属氧化物半导体)的晶体管积层而以三维电路构成。然而,即便将nmos与pmos的晶体管一层一层地积层,衬底每单位面积的元件密度仍有可能较小。

技术实现思路

1、一实施方式提供一种使衬底每单位面积的元件密度及布局的自由度提高的半导体装置。

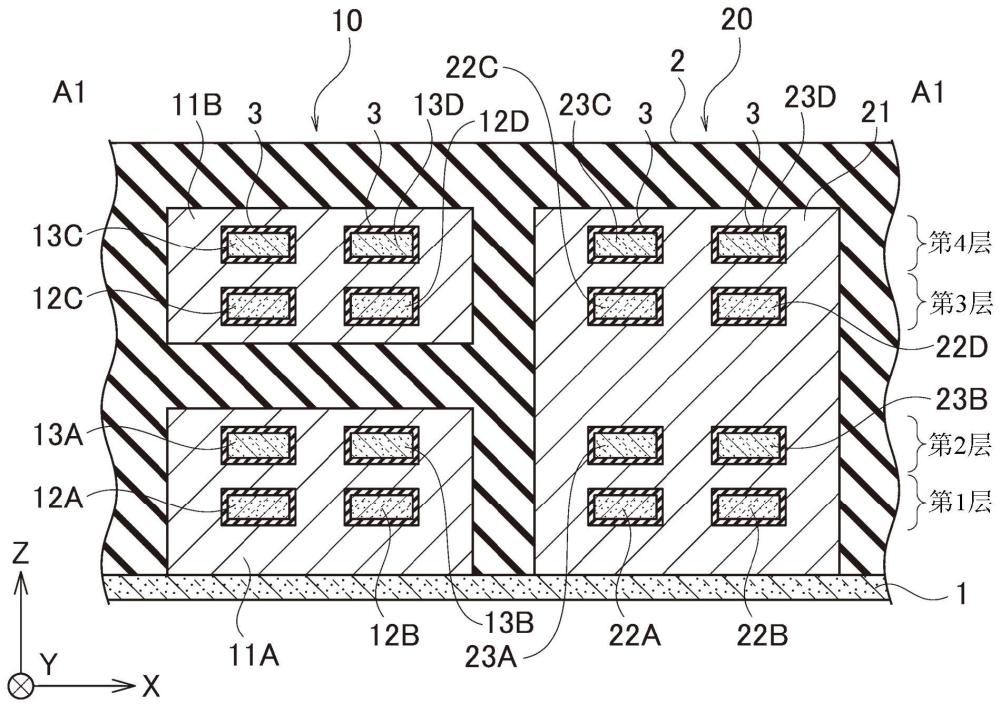

2、实施方式的半导体装置具备:第1半导体层,具有第1源极区域、第1漏极区域、及第1通道区域;第2半导体层,具有第2源极区域、第2漏极区域、及第2通道区域;以及栅极电极,以隔着栅极绝缘膜覆盖第1通道区域及第2通道区域的方式形成。半导体装置具备由具有第1半导体层的第1导电型mos与具有第2半导体层的第2导电型mos的组合构成的第1cmos电路及第2cmos电路。第1半导体层积层在第(2n-1)层。第2半导体层积层在第2n层(1≦n≦n,n≧2,n与n为整数)。关于某i(1≦i≦n),第1cmos电路中,栅极电极至少在第(2i-1)层的第1半导体层的第1导电型mos与第2i层的第2半导体层的第2导电型mos共通地电连接。第2cmos电路中,栅极电极至少在第2i层的第2半导体层的第2导电型mos与第(2i+1)层的第1半导体层的第1导电型mos共通地电连接。

3、根据所述构成,可提供一种使衬底每单位面积的元件密度及布局的自由度提高的半导体装置。

技术特征:

1.一种半导体装置,具备:

2.根据权利要求1所述的半导体装置,其中在所述第1半导体层及所述第2半导体层的下方还具备衬底。

3.根据权利要求2所述的半导体装置,其中所述第1半导体层与所述衬底的表面垂直积层而配置。

4.根据权利要求2所述的半导体装置,其中所述第2半导体层与所述衬底的表面垂直积层而配置。

5.根据权利要求2所述的半导体装置,其中所述衬底形成有氧化膜。

6.根据权利要求1所述的半导体装置,其中所述栅极电极

7.根据权利要求1所述的半导体装置,其中所述栅极电极

8.根据权利要求1所述的半导体装置,其中所述栅极电极

9.根据权利要求1所述的半导体装置,其中所述第1cmos电路具有:

10.根据权利要求1所述的半导体装置,其中所述第2cmos电路具有:

11.根据权利要求1所述的半导体装置,还具备:

12.一种半导体装置,具备:

13.根据权利要求12所述的半导体装置,其中所述栅极电极

14.根据权利要求12所述的半导体装置,其中所述栅极电极

15.根据权利要求12所述的半导体装置,其中所述第1cmos电路具有:

16.根据权利要求12所述的半导体装置,其中所述第2cmos电路

17.根据权利要求12所述的半导体装置,其中在所述第1半导体层及所述第2半导体层的下方还具备衬底。

18.根据权利要求17所述的半导体装置,其中所述衬底形成有氧化膜。

19.根据权利要求12所述的半导体装置,还具备第2电源配线层,所述第2电源配线层夹在第(4n-2)层与第(4n-1)层的所述第2半导体层之间,且在与所述第2半导体层正交的方向上配置。

技术总结

实施方式的半导体装置具备:第1半导体层,具有第1源极区域、第1漏极区域、及第1通道区域;第2半导体层,具有第2源极区域、第2漏极区域、及第2通道区域;以及栅极电极,以隔着栅极绝缘膜覆盖第1通道区域及第2通道区域的方式形成。半导体装置具备由具有第1半导体层的第1导电型MOS与具有第2半导体层的第2导电型MOS的组合构成的第1CMOS电路及第2CMOS电路。第1半导体层积层在第(2n-1)层。第2半导体层积层在第2n层(1≦n≦N,N≧2,n与N为整数)。

技术研发人员:矢部友章

受保护的技术使用者:铠侠股份有限公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!