集成电路芯片的电容增加方法和电容增加结构与流程

本发明涉及集成电路芯片的,尤其涉及一种集成电路芯片的电容增加方法和电容增加结构。

背景技术:

1、随着集成电路的发展,人们对产品质量和可靠性要求不断提高,失效分析工作也显得越来越重要。工程师在失效分析验证过程中经常需要在集成电路芯片的电路中增加电容来达到验证的需求。

2、目前的增加电容的方法是在芯片内部定点生长探针点(probe pad),然后通过探针台扎针外加电容来实现,这种方式操作起来步骤繁琐,导致集成电路芯片的芯片验证效率较低。

技术实现思路

1、本发明提供了一种集成电路芯片的电容增加方法和电容增加结构,以解决现有的电容增加方法步骤繁琐,导致集成电路芯片的芯片验证效率较低的问题。

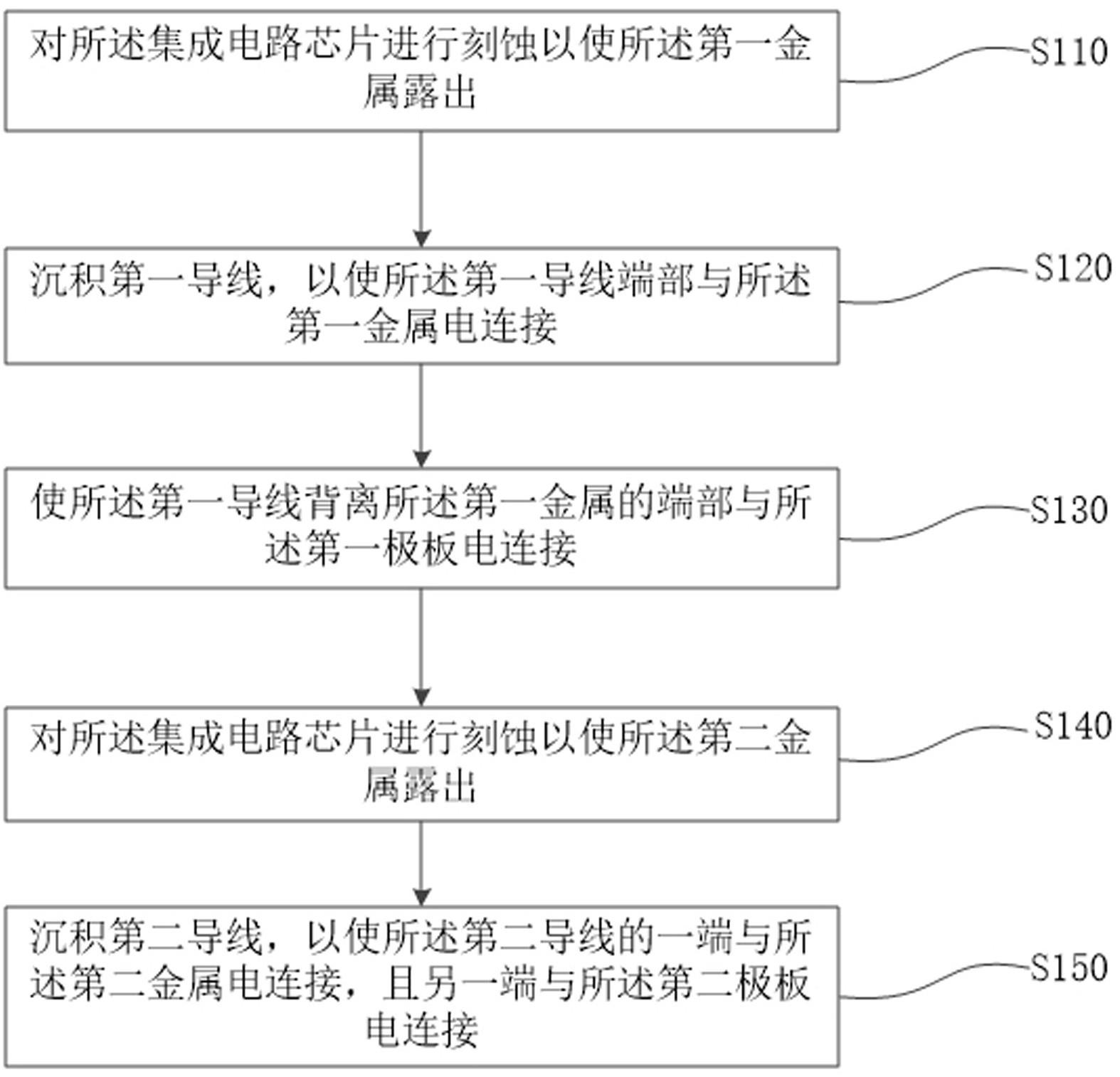

2、根据本发明的一方面,提供了一种集成电路芯片的电容增加方法,所述集成电路芯片的电容增加方法用于在集成电路芯片的第一金属和第二金属之间增加电容,所述电容包括第一极板和第二极板;所述电容增加方法包括:

3、对所述集成电路芯片进行刻蚀以使所述第一金属露出;

4、沉积第一导线,以使所述第一导线端部与所述第一金属电连接;

5、使所述第一导线背离所述第一金属的端部与所述第一极板电连接;

6、对所述集成电路芯片进行刻蚀以使所述第二金属露出;

7、沉积第二导线,以使所述第二导线的一端与所述第二金属电连接,且另一端与所述第二极板电连接。

8、在本发明的可选实施例中,所述使所述第一导线背离所述第一金属的端部与所述第一极板电连接,包括:

9、在所述第一导线背离所述第一金属的端部沉积金属板形成所述第一极板。

10、在本发明的可选实施例中,所述在所述第一导线背离所述第一金属的端部沉积金属板形成所述第一极板之后,还包括:

11、在所述第一极板的上方沉积绝缘材料形成介质层;

12、在所述介质层的上方沉积金属板形成所述第二极板。

13、在本发明的可选实施例中,所述电容增加方法还包括以下至少一项:

14、所述绝缘材料包括二氧化硅;

15、所述第一导线背离所述第一金属的端部位于所述集成电路芯片表面的空白区域;

16、所述第一极板和所述第二极板中的至少一个厚度为1um。

17、在本发明的可选实施例中,所述在所述第一极板的上方沉积绝缘材料形成介质层之前,还包括:

18、通过辅助气体清洁所述第一极板和所述第一导线以外的金属溅射污染物;

19、和/或,所述沉积第二导线,以使所述第二导线的一端与所述第二金属电连接,且另一端与所述第二极板电连接之后,还包括:

20、通过辅助气体清洁所述第二极板和所述第二导线以外的金属溅射污染物。

21、在本发明的可选实施例中,所述辅助气体包括二氟化氙。

22、在本发明的可选实施例中,所述对所述集成电路芯片进行刻蚀以使所述第一金属露出,包括:

23、确定所述集成电路芯片需要增加电容的第一目标位置;

24、通过离子束对所述第一目标位置进行刻蚀以使所述第一金属露出;所述第一目标位置的刻蚀区域的宽度与所述第一导线的线宽相同。

25、在本发明的可选实施例中,所述对所述集成电路芯片进行刻蚀以使所述第二金属露出,包括:

26、确定所述集成电路芯片需要增加电容的第二目标位置;

27、通过离子束对所述第二目标位置进行刻蚀以使所述第二金属露出;所述第二目标位置的刻蚀区域的宽度与所述第二导线的线宽相同。

28、根据本发明的另一方面,提供了一种集成电路芯片的电容增加结构,由本发明任一实施例所述的集成电路芯片的电容增加方法制成,所述集成电路芯片的电容增加结构包括芯片本体和电容,所述芯片本体包括第一金属、第二金属、第一导线、第二导线、加工面、第一通道和第二通道;

29、所述电容位于所述加工面,所述电容包括第一极板和第二极板;

30、所述第一通道由所述加工面贯通至所述第一金属的表面;

31、所述第二通道由所述加工面贯通至所述第二金属的表面;

32、所述第一导线位于所述第一通道内,且一端与所述第一金属电连接,另一端与所述第一极板电连接;

33、所述第二导线位于所述第二通道内,且一端与所述第二金属电连接,另一端与所述第二极板电连接。

34、在本发明的可选实施例中,所述电容还包括介质层,所述介质层由绝缘材料制成;

35、所述第一极板与所述加工面接触,所述介质层位于所述第一极板和所述第二极板之间。

36、在本发明的可选实施例中,所述电容增加结构还包括以下至少一项:

37、所述第一极板和第二极板中的至少一个厚度为1um;

38、所述第一极板和所述第二极板中的至少一种由沉积金属板形成;

39、所述介质层由二氧化硅沉积形成。

40、本发明实施例的技术方案,通过对所述集成电路芯片进行刻蚀以使所述第一金属露出;沉积第一导线,以使所述第一导线端部与所述第一金属电连接;使所述第一导线背离所述第一金属的端部与所述第一极板电连接;对所述集成电路芯片进行刻蚀以使所述第二金属露出;最后沉积第二导线,以使所述第二导线的一端与所述第二金属电连接,且另一端与所述第二极板电连接。从而实现了在集成电路芯片的电路中增加电容,无需在芯片内部定点生长探针点(probe pad),然后通过探针台扎针外加电容,解决了现有的电容增加方法步骤繁琐,导致集成电路芯片的芯片验证效率较低的问题。

41、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种集成电路芯片的电容增加方法,其特征在于,用于在集成电路芯片的第一金属和第二金属之间增加电容,所述电容包括第一极板和第二极板;所述电容增加方法包括:

2.根据权利要求1所述的集成电路芯片的电容增加方法,其特征在于,所述使所述第一导线背离所述第一金属的端部与所述第一极板电连接,包括:

3.根据权利要求2所述的集成电路芯片的电容增加方法,其特征在于,所述在所述第一导线背离所述第一金属的端部沉积金属板形成所述第一极板之后,还包括:

4.根据权利要求3所述的集成电路芯片的电容增加方法,其特征在于,所述电容增加方法还包括以下至少一项:

5.根据权利要求3所述的集成电路芯片的电容增加方法,其特征在于,所述在所述第一极板的上方沉积绝缘材料形成介质层之前,还包括:

6.根据权利要求5所述的集成电路芯片的电容增加方法,其特征在于,所述辅助气体包括二氟化氙。

7.根据权利要求1至6中任一项所述的集成电路芯片的电容增加方法,其特征在于,所述对所述集成电路芯片进行刻蚀以使所述第一金属露出,包括:

8.根据权利要求1至6中任一项所述的集成电路芯片的电容增加方法,其特征在于,所述对所述集成电路芯片进行刻蚀以使所述第二金属露出,包括:

9.一种集成电路芯片的电容增加结构,其特征在于,由权利要求1-8中任一项所述的集成电路芯片的电容增加方法制成,所述电容增加结构包括芯片本体(1)和电容(2),所述芯片本体(1)包括第一金属(11)、第二金属(12)、第一导线(13)、第二导线(14)、加工面(15)、第一通道(16)和第二通道(17);

10.根据权利要求9所述的集成电路芯片的电容增加结构,其特征在于,所述电容(2)还包括介质层(23),所述介质层(23)由绝缘材料制成;

11.根据权利要求9或10所述的集成电路芯片的电容增加结构,其特征在于,所述电容增加结构还包括以下至少一项:

技术总结

本发明公开了一种集成电路芯片的电容增加方法和电容增加结构。该集成电路芯片的电容增加方法用于在集成电路芯片的第一金属和第二金属之间增加电容,所述电容包括第一极板和第二极板;所述电容增加方法包括:对所述集成电路芯片进行刻蚀以使所述第一金属露出;沉积第一导线,以使所述第一导线端部与所述第一金属电连接;使所述第一导线背离所述第一金属的端部与所述第一极板电连接;对所述集成电路芯片进行刻蚀以使所述第二金属露出;沉积第二导线,以使所述第二导线的一端与所述第二金属电连接,且另一端与所述第二极板电连接。通过采用上述方案,解决了现有的电容增加方法步骤繁琐,导致集成电路芯片的芯片验证效率较低的问题。

技术研发人员:尚跃,李豪

受保护的技术使用者:上海聚跃检测技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!