一种PN结制备方法、半导体器件的制作方法与流程

本发明涉及一种pn结制备方法、半导体器件的制作方法,属于半导体功率器件。

背景技术:

1、如图16所示,现有半导体功率器件通常会遇到大能量(能量大于80kev)、大剂量(剂量大于3e14cm-2)的离子注入,注入后需要生长氧化层并退火推进以获得一定结深的pn结结构,退火后进行pn结漏电测试,芯片的漏电流会偏大,且整个晶圆上各个pn的漏电流分布一致性不好。

2、如图17所示,现有pn结采用大能量(能量大于80kev)、小剂量(剂量小于3e14cm-2)的离子注入虽然可以降低漏电流并提高整个晶圆上各个pn的漏电流分布的一致性,但由于注入剂量受限,难以满足器件性能要求,采用多次生长氧化层并推进的方式,工艺复杂。

技术实现思路

1、本发明的目的在于克服现有技术中的不足,提供一种pn结制备方法、半导体器件的制作方法,能够解决制成的pn结漏电流一致性差的、工艺复杂的问题。

2、为达到上述目的,本发明是采用下述技术方案实现的:

3、第一方面,本发明提供了一种pn结制备方法,包括:

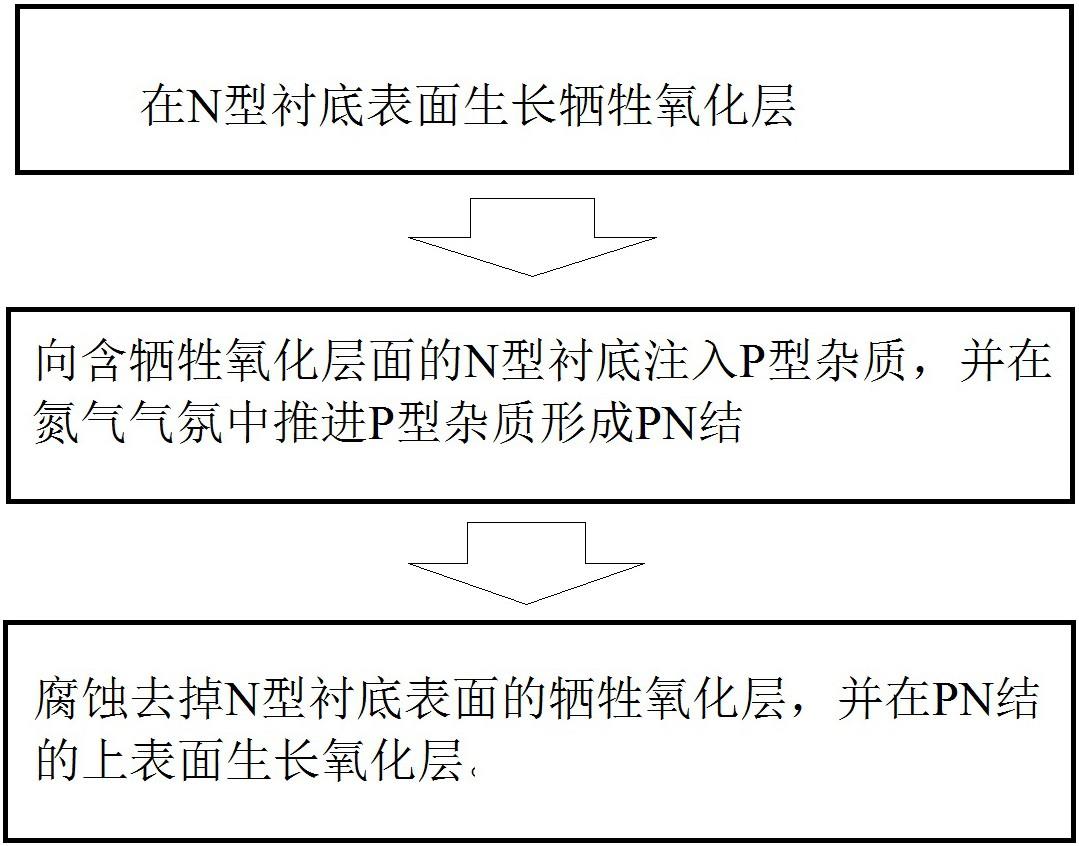

4、在n型衬底表面生长牺牲氧化层;

5、向含牺牲氧化层面的n型衬底注入p型杂质,并在氮气气氛中推进p型杂质形成pn结;

6、腐蚀去掉n型衬底表面的牺牲氧化层,并在pn结的上表面生长氧化层。

7、进一步的,所述n型衬底的厚度为50um-720um。

8、进一步的,所述牺牲氧化层为10nm-50nm。

9、进一步的,注入所述p型杂质的离子能量大于80kev,且剂量大于3e14cm-2。

10、进一步的,所述氧化层厚度为1um-5um。

11、第二方面,本发明提供了一种半导体器件的制作方法,包括上述任一所述的pn结制备方法产生的pn结;

12、光刻并腐蚀pn结上的氧化层,使其与pn结形成凹槽;

13、淀积二氧化硅介质层充满凹槽;

14、光刻并腐蚀二氧化硅介质层,使其与pn结形成凹槽形接触孔;

15、对凹槽形接触孔处淀积金属并光刻形成二极管的阳极;

16、在pn结的背面注入n型杂质并激活后,淀积金属层形成二极管的阴极。

17、进一步的,所述二氧化硅介质层的厚度为1um-4um。

18、进一步的,所述金属层的厚度为1um-5um厚。

19、与现有技术相比,本发明所达到的有益效果:

20、本发明提供的一种pn结制备方法,在n型衬底表面生长牺牲氧化层后,

21、向含牺牲氧化层面的n型衬底注入p型杂质,并在氮气气氛中推进p型杂质形成pn结,改变退火氛围,在注入p型杂质后,先通入氮气退火来消除p型杂质注入后产生的缺陷,再通过氧气生成氧化层的方式,解决pn结漏电流一致性差的问题。

技术特征:

1.一种pn结制备方法,其特征在于,包括:

2.根据权利要求1所述的pn结制备方法,其特征在于,所述n型衬底的厚度为50um-720um。

3.根据权利要求1所述的pn结制备方法,其特征在于,所述牺牲氧化层为10nm-50nm。

4.根据权利要求1所述的pn结制备方法,其特征在于,注入所述p型杂质的离子能量大于80kev,且剂量大于3e14cm-2。

5.根据权利要求1所述的pn结制备方法,其特征在于,所述氧化层厚度为1um-5um。

6.一种半导体器件的制作方法,其特征在在于,包括权利要求1至5任一所述的pn结制备方法产生的pn结;

7.根据权利要求6所述的半导体器件的制作方法,其特征在于,所述二氧化硅介质层的厚度为1um-4um。

8.根据权利要求6所述的半导体器件的制作方法,其特征在于,所述金属层的厚度为1um-5um厚。

技术总结

本发明公开了半导体功率器件领域的一种PN结制备方法、半导体器件的制作方法,旨在解决现有工艺制成的PN结漏电流偏大的技术问题。其包括在N型衬底表面生长牺牲氧化层;向含牺牲氧化层面的N型衬底注入P型杂质,并在氮气气氛中推进P型杂质形成PN结;腐蚀去掉N型衬底表面的牺牲氧化层,并在PN结的上表面生长氧化层;本发明方法制成的PN结可解决现有工艺制成PN结漏电流一致性差的问题。

技术研发人员:高东岳,张大华,叶枫叶,周东海,钱培华

受保护的技术使用者:南瑞联研半导体有限责任公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!