一种半导体器件的制作方法

本发明涉及半导体,特别涉及一种半导体器件。

背景技术:

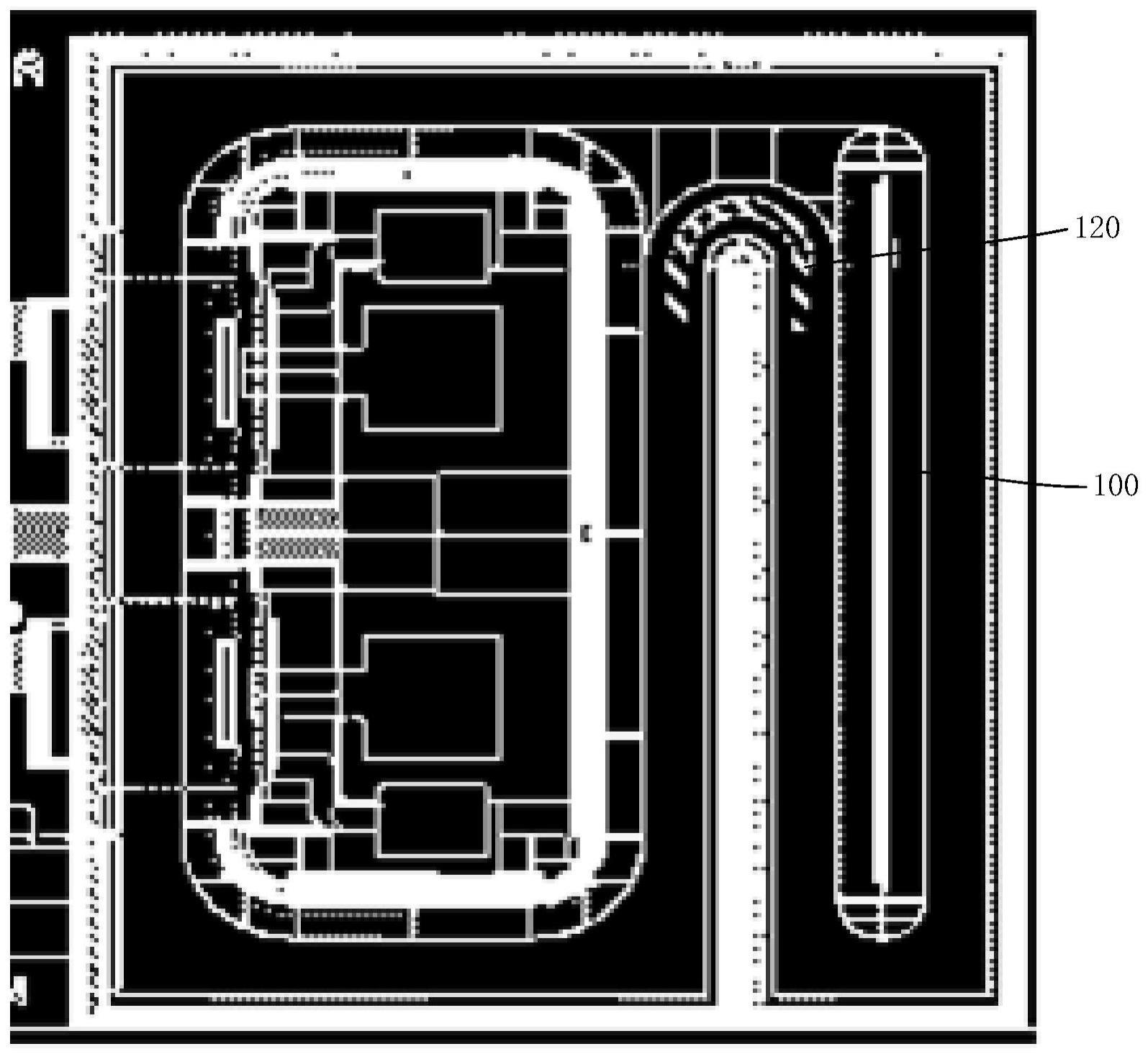

1、随着半导体集成电路技术的不断发展,芯片内部通常会划分有多个不同的电压区域,用于集成不同电源电压需求的器件。相关技术中集成有不同电压区域的芯片,包括低压区域和高压区域,低压区域和高压区域之间由隔离环结构隔离。通常高压区域器件的电源需求电压高于低压区域器件的电源需求电压,因此为了实现低压区域器件和高压区域器件之间的信息交互,需要在低压区域和高压区域之间连接电压转换器,通过该电压转换器实现电压转换。如图1所示,目前,集成了ldmos(横向双扩散金属氧化物半导体)晶体管的高压环结构包括u型升压二极管1以增大电流。在这种结构中,由于u型升压二极管1的漏端电场向源端过于集中,导致u型升压二极管1的源流bv(击穿电压)减低。

技术实现思路

1、本发明的目的在于,提供一种半导体器件,可以提高u型升压二极管的源流bv。

2、为了解决上述问题,本发明提供一种半导体器件,所述半导体器件为集成ldmos晶体管的高压环结构,所述半导体器件包括u型升压二极管,所述u型升压二极管包括衬底及位于所述衬底上的外延层,所述u型升压二极管具有依次设置的基极接出端、源极接出端、栅极接触端和漏极接出端,所述基极接出端和源极接出端位于所述外延层中,所述栅极接触端以及所述漏极接出端的部分位于所述外延层上,且所述基极接出端和源极接出端之间设置有第一场氧区,所述栅极接触端的部分和所述漏极接出端的部分位于第二场氧区上;

3、所述第一场氧区、源极接出端和基极接出端下方设置有第一隔离结构,所述第二场氧区的下方设置有第二隔离结构,所述第一隔离结构和第二隔离结构同层且间隔设置,且所述第一隔离结构沿厚度方向的部分以及所述第二隔离结构沿厚度方向的部分均位于所述衬底中,所述第一隔离结构沿厚度方向的剩余部分以及所述第二隔离结构沿厚度方向的剩余部分均位于所述外延层中。

4、可选的,所述第一隔离结构包括第一埋层和第一掺杂区,所述第一掺杂区位于所述第一埋层的上方,且所述第一掺杂区位于所述外延区中,所述第一埋层沿厚度方向的部分位于所述外延区中,且沿厚度方向的剩余部分位于所述衬底中。

5、进一步的,所述第一埋层为p型埋层,所述第一掺杂区为p型掺杂区。

6、进一步的,所述第二隔离结构位于所述u型升压二极管的底部区域。

7、进一步的,所述第二隔离结构的形状呈拱门状。

8、进一步的,所述第二隔离结构包括第二埋层和第二掺杂区,所述第二掺杂区位于所述第二埋层的上方,且第二埋层和第二掺杂区接触设置。

9、进一步的,所述第二埋层为p型埋层,所述第二掺杂区为p型掺杂区。

10、进一步的,所述第二掺杂区与所述第一掺杂区同层设置,且所述第二埋层和第一埋层同层设置。

11、进一步的,所述第二掺杂区和所述第一掺杂区的深度相同,所述第二掺杂区和所述第一掺杂区的厚度相同,所述第二埋层和第一埋层的深度相同,所述第二埋层和第一埋层的厚度相同。

12、进一步的,所述第二埋层沿厚度方向的部分位于所述外延区中,沿厚度方向的剩余部分位于所述衬底中。

13、可选的,所述衬底为p型衬底,所述外延区为n型外延区。

14、可选的,所述外延区中形成有p阱,所述第一隔离结构位于所述p阱下方,所述p阱形成有间隔设置的第一n+区和p+区,所述第一n+区为源极接出端,所述p+区为基极接出端。

15、与现有技术相比,本发明具有以下有益效果:

16、本发明提供一种半导体器件,包括u型升压二极管,所述u型升压二极管包括衬底及位于所述衬底上的外延层,所述u型升压二极管具有依次设置的基极接出端、源极接出端、栅极接触端和漏极接出端,所述基极接出端和源极接出端位于所述外延层中,所述栅极接触端以及所述漏极接出端的部分位于所述外延层上,且所述基极接出端和源极接出端之间设置有第一场氧区,所述栅极接触端的部分和所述漏极接出端的部分位于第二场氧区上;所述第一场氧区、源极接出端和基极接出端下方设置有第一隔离结构,所述第二场氧区的下方设置有第二隔离结构,所述第一隔离结构和第二隔离结构同层且间隔设置,且所述第一隔离结构沿厚度方向的部分以及所述第二隔离结构沿厚度方向的部分均位于所述衬底中,所述第一隔离结构沿厚度方向的剩余部分以及所述第二隔离结构沿厚度方向的剩余部分均位于所述外延层中。本发明中的第二隔离结构使得横跨的高电位可以分散电场,以防止电场集中,从而使得电场不会集中的u型升压二极管底部的源极端,增大了半导体器件中升压二极管的击穿电压bv。

技术特征:

1.一种半导体器件,所述半导体器件为集成ldmos晶体管的高压环结构,其特征在于,所述半导体器件包括u型升压二极管,所述u型升压二极管包括衬底及位于所述衬底上的外延层,所述u型升压二极管具有依次设置的基极接出端、源极接出端、栅极接触端和漏极接出端,所述基极接出端和源极接出端位于所述外延层中,所述栅极接触端以及所述漏极接出端的部分位于所述外延层上,且所述基极接出端和源极接出端之间设置有第一场氧区,所述栅极接触端的部分和所述漏极接出端的部分位于第二场氧区上;

2.如权利要求1所述的半导体器件,其特征在于,所述第一隔离结构包括第一埋层和第一掺杂区,所述第一掺杂区位于所述第一埋层的上方,且所述第一掺杂区位于所述外延区中,所述第一埋层沿厚度方向的部分位于所述外延区中,且沿厚度方向的剩余部分位于所述衬底中。

3.如权利要求2所述的半导体器件,其特征在于,所述第一埋层为p型埋层,所述第一掺杂区为p型掺杂区。

4.如权利要求2所述的半导体器件,其特征在于,所述第二隔离结构位于所述u型升压二极管的底部区域。

5.如权利要求4所述的半导体器件,其特征在于,所述第二隔离结构的形状呈拱门状。

6.如权利要求4所述的半导体器件,其特征在于,所述第二隔离结构包括第二埋层和第二掺杂区,所述第二掺杂区位于所述第二埋层的上方,且第二埋层和第二掺杂区接触设置。

7.如权利要求6所述的半导体器件,其特征在于,所述第二埋层为p型埋层,所述第二掺杂区为p型掺杂区。

8.如权利要求6所述的半导体器件,其特征在于,所述第二掺杂区与所述第一掺杂区同层设置,且所述第二埋层和第一埋层同层设置。

9.如权利要求6所述的半导体器件,其特征在于,所述第二掺杂区和所述第一掺杂区的深度相同,所述第二掺杂区和所述第一掺杂区的厚度相同,所述第二埋层和第一埋层的深度相同,所述第二埋层和第一埋层的厚度相同。

10.如权利要求6所述的半导体器件,其特征在于,所述第二埋层沿厚度方向的部分位于所述外延区中,沿厚度方向的剩余部分位于所述衬底中。

11.如权利要求1所述的半导体器件,其特征在于,所述衬底为p型衬底,所述外延区为n型外延区。

12.如权利要求1所述的半导体器件,其特征在于,所述外延区中形成有p阱,所述第一隔离结构位于所述p阱下方,所述p阱形成有间隔设置的第一n+区和p+区,所述第一n+区为源极接出端,所述p+区为基极接出端。

技术总结

本发明提供一种半导体器件,包括U型升压二极管,U型升压二极管包括位于所述第一场氧区、源极接出端和基极接出端下方设置有第一隔离结构,以及位于所述第二场氧区的下方设置有第二隔离结构,所述第一隔离结构和第二隔离结构同层且间隔设置,且所述第一隔离结构沿厚度方向的部分以及所述第二隔离结构沿厚度方向的部分均位于所述衬底中,所述第一隔离结构沿厚度方向的剩余部分以及所述第二隔离结构沿厚度方向的剩余部分均位于所述外延层中。本发明中的第二隔离结构使得横跨的高电位可以分散电场,以防止电场集中,从而使得电场不会集中的U型升压二极管底部的源极端,增大了半导体器件中升压二极管的击穿电压BV。

技术研发人员:潘山山,蔡莹,金锋

受保护的技术使用者:上海华虹宏力半导体制造有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!