半导体封装件及其制造方法与流程

本发明构思的实施方式涉及一种半导体封装件及其制造方法。

背景技术:

1、由于电子工业的巨大进步和用户需求,电子装置已经变得更小和更轻。随着电子装置的尺寸和重量持续减小,用于电子装置的半导体封装件也已经在尺寸和重量方面减小。此外,半导体封装件需要高性能、高容量以及高可靠性。通常,对半导体封装件的高性能和高容量的要求导致高功耗。因此,与尺寸、性能和稳定供电有关的半导体封装件的结构变得重要。

技术实现思路

1、本公开涉及半导体封装件,并且具体地,涉及包括位于半导体芯片的上部和位于半导体芯片的下部的重分布衬底的半导体封装件及其制造方法。在包括上芯片和下芯片的半导体封装件内,在上芯片和下芯片之间会存在缩短的路径,例如,上芯片和下芯片彼此面对的表面之间的路径。在一些实施方式中,对半导体封装件进行配置使得信号传输路径沿着这个缩短的路径能够减少热量、改进信号完整性(si)并且相对于半导体封装件中的功耗而提高性能。

2、另外,本发明构思要解决的问题不限于上述问题,本领域的普通技术人员通过下文的描述可以清楚地理解一些其它问题。

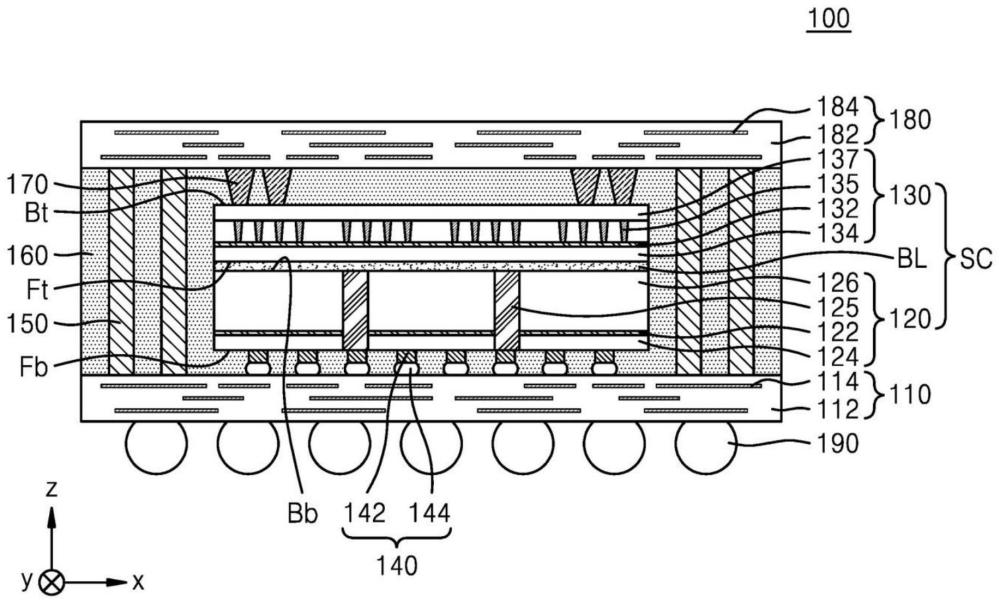

3、通常,在本说明书中描述的主题的创新方面可以在半导体封装件中实施,该半导体封装件包括:第一重分布衬底;半导体芯片堆叠件,其布置在第一重分布衬底上,其中,半导体芯片堆叠件包括下芯片和上芯片;贯通柱,其布置在第一重分布衬底上围绕半导体芯片堆叠件;以及第二重分布衬底,其布置在半导体芯片堆叠件和贯通柱上。上芯片可以包括布置在集成电路层上的贯通电极。上芯片具有前表面和背表面,前表面是有源面并且面向下芯片,背表面是无源面并且面向第二重分布衬底。

4、通常,在另一方面,本公开的主题可以在半导体封装件中实施,该半导体封装件包括:第一重分布衬底;半导体芯片堆叠件,其布置在第一重分布衬底上,其中,半导体芯片堆叠件包括下芯片和上芯片;贯通柱,其布置在第一重分布衬底上围绕半导体芯片堆叠件;密封件,其包围贯通柱的侧表面并覆盖半导体芯片堆叠件,以密封半导体芯片堆叠件;第二重分布衬底,其布置在封装件和贯通柱上;以及外部接触端子,其以扇出(fo)结构布置在第一重分布衬底的下表面上,其中上芯片包括:集成电路层;集成电路层上的贯通电极;贯通电极上的上布线层;以及集成电路层下方的下布线层。

5、通常,在另一方面,本公开的主题可以在半导体封装件中实施,该半导体封装件包括:下封装件;上封装件,其通过衬底间接触端子堆叠在下封装件上;外部接触端子,其以扇出(fo)结构布置在下封装件的下表面上,其中,下封装件包括:第一重分布衬底;布置在第一重分布衬底上的半导体芯片堆叠件,其中,半导体芯片堆叠件包括下芯片和上芯片;贯通柱,其布置在第一重分布衬底上围绕半导体芯片堆叠件;以及第二重分布衬底,其布置在半导体芯片堆叠件和贯通柱上。上芯片包括:集成电路层;布置在集成电路层上的贯通电路;贯通电极上的上布线层;以及集成电路层下方的下布线层。

6、通常,在另一方面,本公开的主题可以在包括以下步骤的方法中实施,该方法包括:形成具有下芯片和上芯片的半导体芯片堆叠件;在载体衬底上形成第一重分布衬底;在第一重分布衬底的周边部分上形成贯通柱;将半导体芯片堆叠件布置在第一重分布衬底的中心部分上;形成覆盖贯通柱和半导体芯片堆叠件的密封件;对密封件的上部进行平坦化以暴露贯通柱的上表面;以及在贯通柱和密封件上形成第二重分布衬底,其中,形成半导体芯片堆叠件包括:在集成电路层上形成具有贯通电极的上芯片;以及将上芯片堆叠在下芯片上。

技术特征:

1.一种半导体封装件,包括:

2.根据权利要求1所述的半导体封装件,其中,所述贯通电极连接至所述集成电路层,或者

3.根据权利要求1所述的半导体封装件,其中,所述上芯片包括下布线层和上布线层,所述下布线层布置在所述集成电路层下方,所述上布线层布置在所述贯通电极上。

4.根据权利要求3所述的半导体封装件,还包括上封装件,所述上封装件布置在所述第二重分布衬底上,

5.根据权利要求1所述的半导体封装件,还包括密封件,所述密封件填充所述第一重分布衬底和所述第二重分布衬底之间的间隙空间,其中,所述密封件覆盖所述半导体芯片堆叠件,以密封所述半导体芯片堆叠件,

6.根据权利要求5所述的半导体封装件,还包括竖直接触件,所述竖直接触件将所述半导体芯片堆叠件连接至所述第二重分布衬底。

7.根据权利要求1所述的半导体封装件,其中,所述上芯片和所述下芯片通过混合键合彼此连接,其中,所述混合键合包括焊盘至焊盘键合和绝缘体至绝缘体键合的组合。

8.根据权利要求1所述的半导体封装件,其中,所述上芯片的前表面键合至所述下芯片的前表面,或者

9.一种半导体封装件,包括:

10.根据权利要求9所述的半导体封装件,还包括所述第二重分布衬底上的上封装件,

11.根据权利要求9所述的半导体封装件,其中,所述上芯片和所述下芯片通过混合键合彼此键合。

12.根据权利要求11所述的半导体封装件,其中,所述上芯片的前表面键合至所述下芯片的前表面,或者

13.一种半导体封装件,包括:

14.根据权利要求13所述的半导体封装件,其中,所述上封装件包括存储器芯片,并且通过所述衬底间接触端子安装在所述第二重分布衬底上,

15.根据权利要求13所述的半导体封装件,其中,所述上芯片和所述下芯片通过混合键合彼此键合,并且

16.一种制造半导体封装件的方法,所述方法包括:

17.根据权利要求16所述的方法,其中,形成所述上芯片包括:

18.根据权利要求17所述的方法,其中,所述上芯片和所述下芯片通过混合键合彼此键合,使得所述下芯片的前表面或所述下芯片的背表面键合至所述上芯片的前表面。

19.根据权利要求16所述的方法,还包括:在形成所述第二重分布衬底之前,形成竖直接触件,所述竖直接触件穿透所述半导体芯片堆叠件上的所述密封件,并且连接至所述半导体芯片堆叠件。

20.根据权利要求16所述的方法,还包括:在形成所述第二重分布衬底之后,通过衬底间接触端子将上封装件堆叠在所述第二重分布衬底上,

技术总结

提供了一种具有半导体芯片之间的信号传输路径的半导体封装件及其制造方法。该半导体封装件包括:第一重分布衬底;布置在第一重分布衬底上并且包括下芯片和上芯片的半导体芯片堆叠件;布置在第一重分布衬底上围绕半导体芯片堆叠件的贯通柱;以及布置在半导体芯片堆叠件和贯通柱上的第二重分布衬底。上芯片包括布置在集成电路层上的贯通电极,并且具有作为有源面且面向下芯片的前表面,以及作为无源面并且面向第二重分布衬底的背表面。

技术研发人员:文炅墩

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!